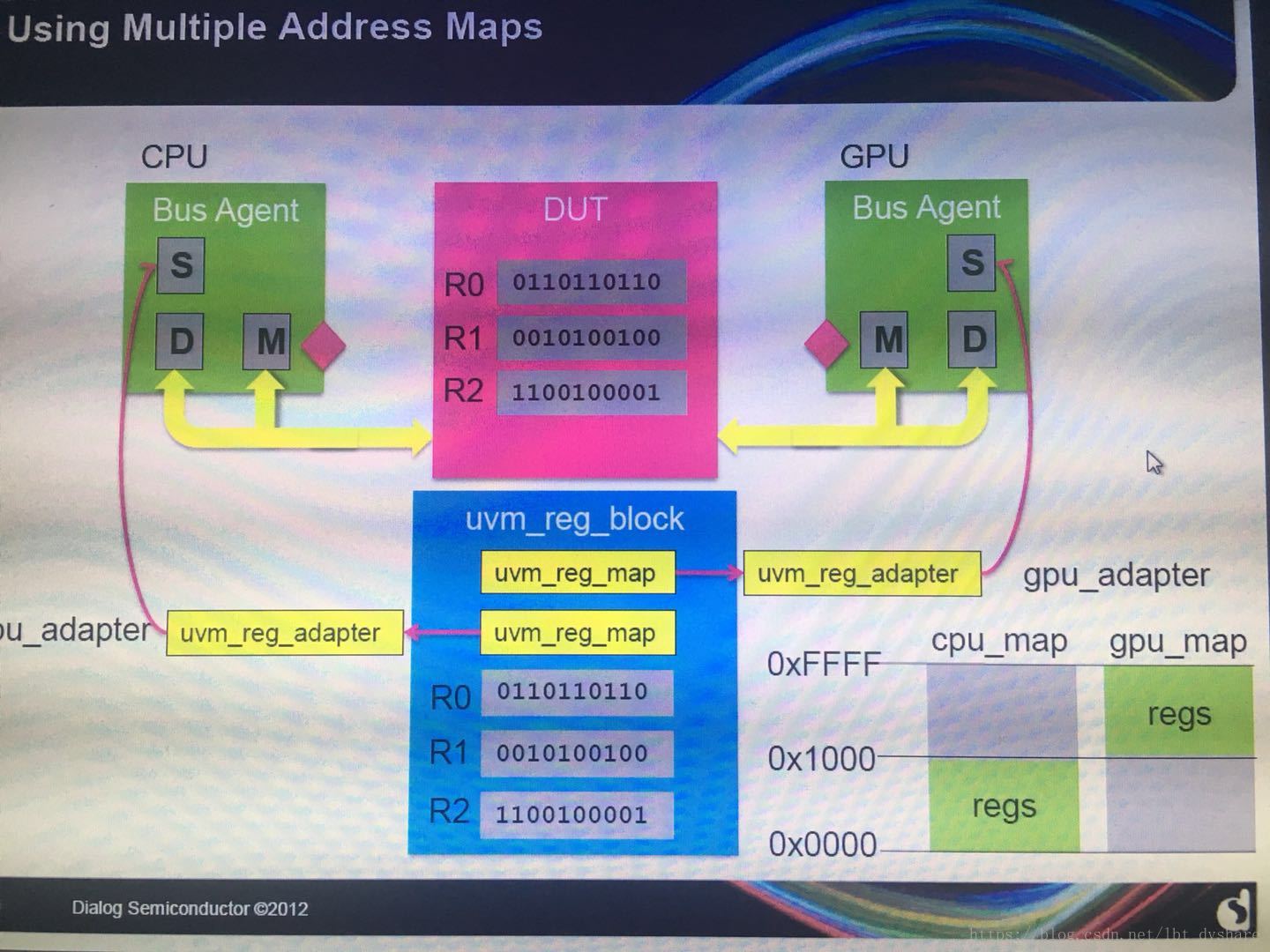

ral model 中涉及到不同的map,这边给一些例子~~

class my_regmodel extends uvm_reg_block;

...

uvm_reg_mapcpu_map;

uvm_reg_mapgpu_map;

...

cpu_map= create_map("cpu_map", 'h0, 2, UVM_LITTLE_ENDIAN);

cpu_map.add_reg(R0, 'h0, "RW"); // real address: 'h0

cpu_map.add_reg(R1, 'h2, "RW"); // real address: 'h2

cpu_map.add_reg(R2, 'h4, "RW"); // real address: 'h4

gpu_map= create_map("gpu_map", 'h1000, 2, UVM_LITTLE_ENDIAN);

gpu_map.add_reg(R0, 'h0, "RW"); // real address: 'h1000

gpu_map.add_reg(R1, 'h2, "RO"); // real address: 'h1002

gpu_map.add_reg(R2, 'h4, "RW"); // real address: 'h1004

set_default_map(cpu_map); // map to use if none specified

endclass: my_regmodel

//-----------------------------------------------------------------------

//sequence

//-----------------------------------------------------------------------

regblock.R0.write(status,8'ha5,.map(cpu_map),.parent(this));

regblock.R1.read(status,data,.map(gpu_map),.parent(this));

. . .//----------------------------------------------

//env

//----------------------------------------------

function void my_env::build_phase(uvm_phasephase);

uvm_reg_pridictor#(cpu_trans) cpu_predictor;

uvm_reg_pridictor#(gpu_trans) gpu_predictor;

...

regmodel= my_regmodel::type_id::create("regmodel");

reg2apb = reg2apb_adapter::type_id::create("reg2apb");

reg2ahb = reg2ahb_adapter::type_id::create("reg2ahb");

cpu_predictor = uvm_reg_pridictor#(cpu_trans)::type_id::create("cpu_predictor");

gpu_predictor = uvm_reg_pridictor#(gpu_trans)::type_id::create("gpu_predictor");

regmodel.build();

//1.use auto predict

//regmodel.cpu_map.set_auto_predict();

//regmodel.gpu_map.set_auto_predict();

endfunction: build_phase

function void my_env::connect_phase(uvm_phasephase);

...

regmodel.cpu_map.set_sequencer(apb_agent.sequencer, reg2apb);

regmodel.gpu_map.set_sequencer(ahb_agent.sequencer, reg2ahb);

//2. use predictor

cpu_predictor.map= regmodel.cpu_map;

cpu_predictor.adapter= reg2apb;

apb_agent.monitor.ap(cpu_predictor.bus_in);

gpu_predictor.map= regmodel.gpu_map;

gpu_predictor.adapter= reg2ahb;

ahb_agent.monitor.ap(gpu_predictor.bus_in);

endfunction: connect_phaseUVM提供了两种用来跟踪寄存器值的方式,分别为自动预测(auto predicition)和显式预测。(上例已示范)

- auto prediction 对于sequence 直接在总线层面上对寄存器操作(不用ral model 的write/read task)无法自动得到register的的mirror value 和期望值。

- 显式预测则可以,因为predictor实时监测bus上的动作。