整个过程我没有记录,因为之前记录过了,都是一样的,这里只是记录了下思路。之前的博文:全过程实现一个最简单的FPGA项目之PWM蜂鸣器控制

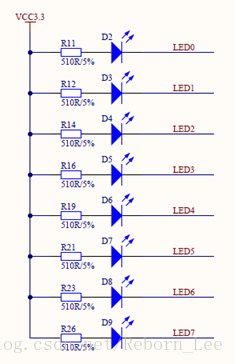

这些LED的正极连接510欧姆限流电阻到3.3V电压,负极都连接到了FPGA的IO引脚上。因此,FPGA可以通过引脚的高或低电平控制LED的亮灭状态。

8个LED指示灯,我们依次给他们赋值,每次只有一个LED点亮,每次点亮某个LED的时间一定(固定延时)。8个LED依次被点亮一次,如此循环便成就了流水灯的效果。

Verilog HDL设计代码

module sp6(

input ext_clk_25m, //外部输入25MHz时钟信号

input ext_rst_n, //外部输入复位信号,低电平有效

output reg[7:0] led //8个LED指示灯接口

);

//-------------------------------------

reg[19:0] cnt; //20位计数器

//cnt计数器进行循环计数

always @ (posedge ext_clk_25m or negedge ext_rst_n)

if(!ext_rst_n) cnt <= 20'd0;

else cnt <= cnt+1'b1;

//-------------------------------------

//计数器cnt计数到最大值时,切换点亮的指示灯

always @ (posedge ext_clk_25m or negedge ext_rst_n)

if(!ext_rst_n) led <= 8'b1111_1110; //默认只点亮一个指示灯D2

else if(cnt == 20'hfffff) led <= {led[6:0],led[7]}; //循环移位操作

else ;

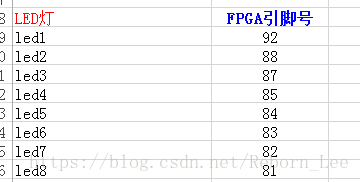

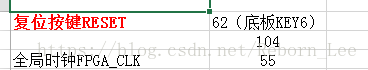

endmodule找到输入输出对应的引脚在FPGA上的位置:

根据这些写引脚约束:

# PlanAhead Generated physical constraints

NET "led[7]" LOC = P81;

NET "led[6]" LOC = P82;

NET "led[5]" LOC = P83;

NET "led[4]" LOC = P84;

NET "led[3]" LOC = P85;

NET "led[2]" LOC = P87;

NET "led[1]" LOC = P88;

NET "led[0]" LOC = P92;

NET "ext_clk_25m" LOC = P55;

NET "ext_rst_n" LOC = P62;

之后进行综合、实现、产生可配置文件,下载到FPGA上调试即可。