ISE ChipScope使用

2014年09月04日 16:25:37

阅读数:12950

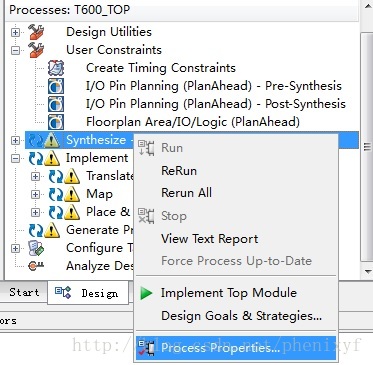

1. 先在综合中设置保持层次,以便在chipsope中保持原电路代码结构

右键Synthesize->Process Properties..

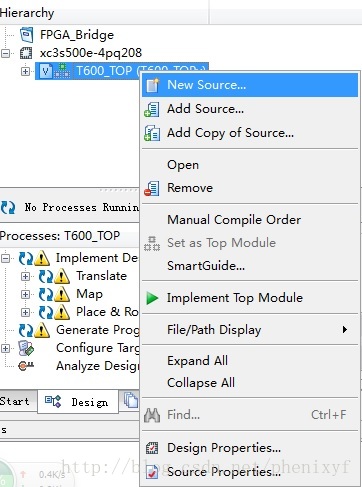

2. 添加CDC文件,给ChipScope使用

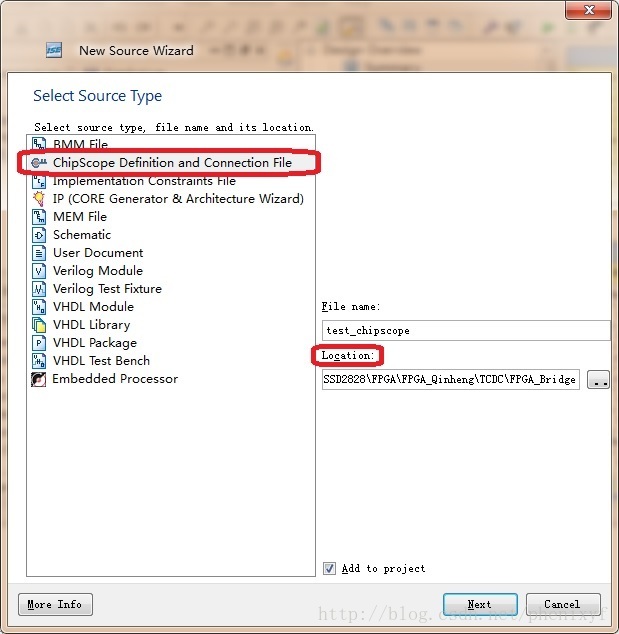

2.1 建立.cdc文件

添加完成后,项目分支中出现cdc文件

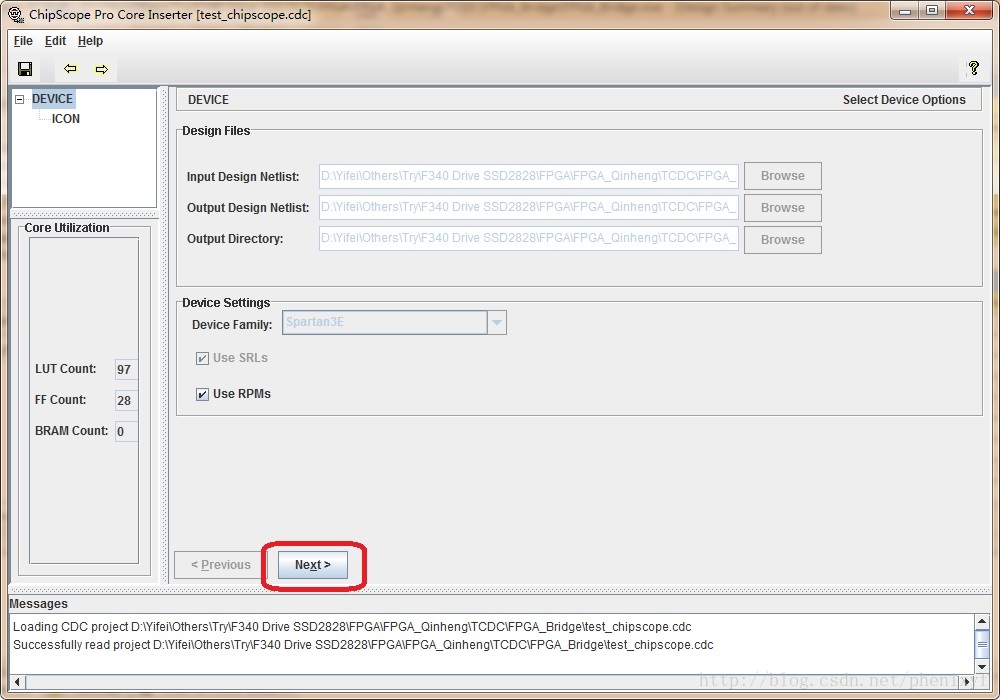

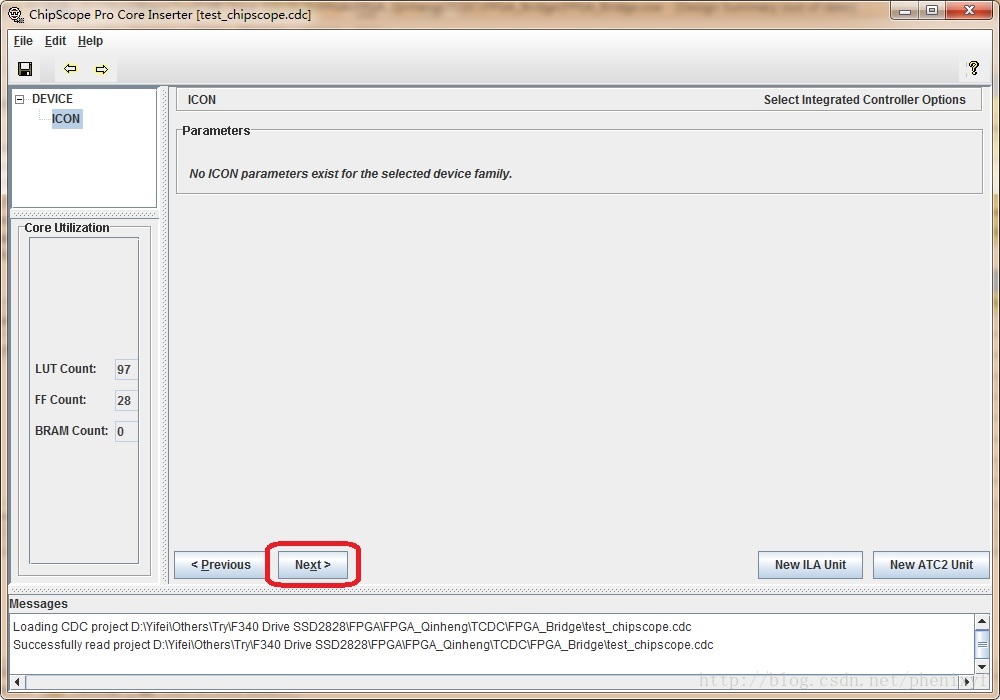

2.2 双击该图标,进入cdc设置窗口,点next

继续点next

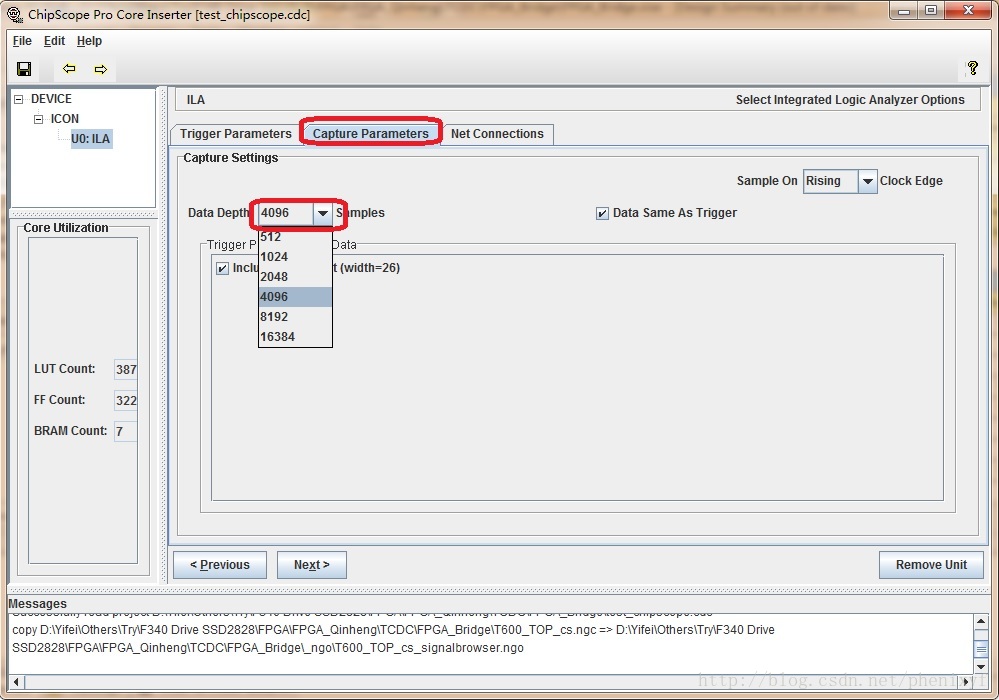

在下面的窗口中进行chipsope参数配置:

2.2.1 设定要监测的信号个数:下图中设置26个

2.2.2 设定监测范围,这项设置与使用的FPGA所自带的RAM大小相关,如设置过大在implement时会报错,下图设置4096深度

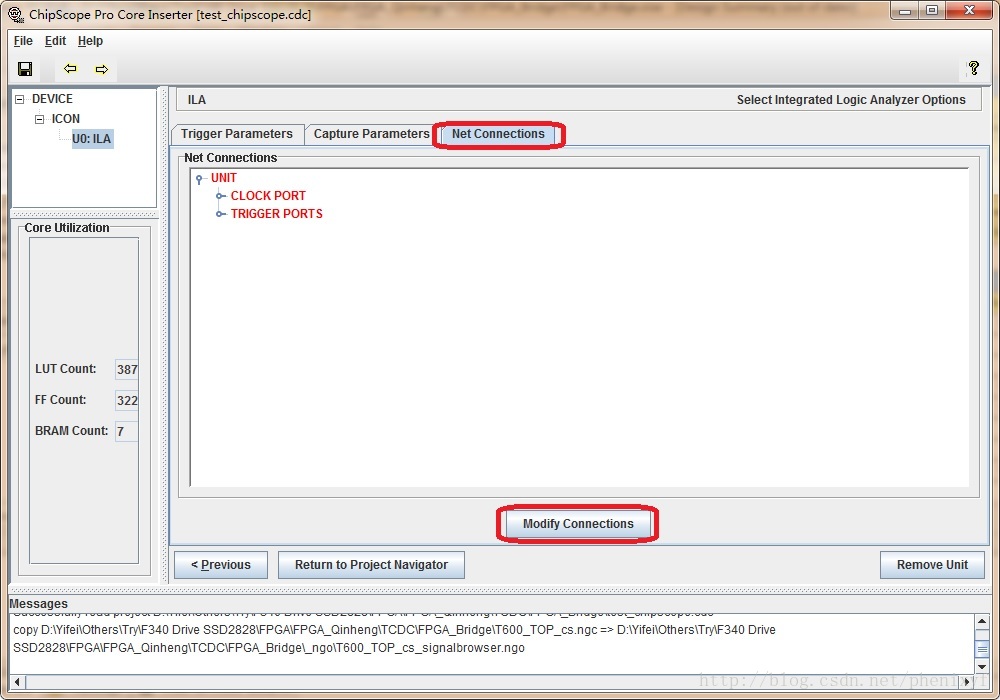

2.2.3 选择要监测的信号及时钟信号:

2.2.3.1 选择时钟信号,下图以clk信号为例

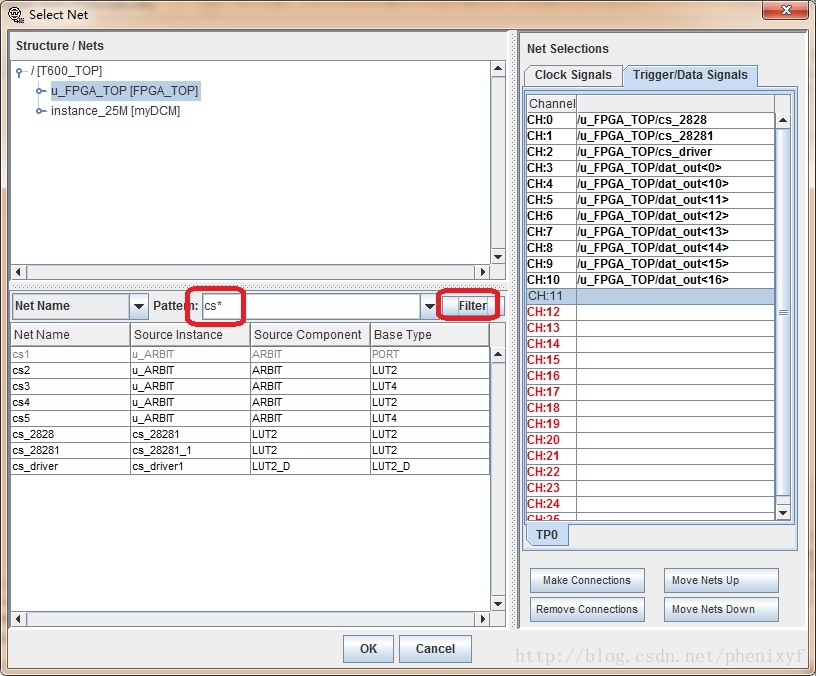

2.2.3.2 设置要监测的信号:

这个步骤中寻找需要的信号,可以使用Filter,在Filter中输入相关字符加*,即可把包含相关字符的所有信号找出

2.3 所有设置完成后,点击保存

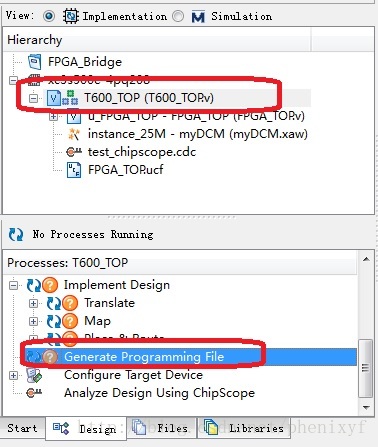

3. 生成.bit文件,运行ChipScope

3.1 生成.bit文件:双击Generate Programming File,第一次运行会比较慢

(右键Generae Programming File -> Process Properties -> Startup Options -> FPGA Start-Up Clock可选JTAG,这个是干什么用的还没试过,可尝试,括号内的动作可以不做)

3.2 用Xilinx仿真器将PC和FPGA连接起来。

3.3 运行ChipScope

双击 Analyze Design Using ChipScope

3.1 在弹出的窗口中,点击连接按钮

3.2 添加生成的.bit文件

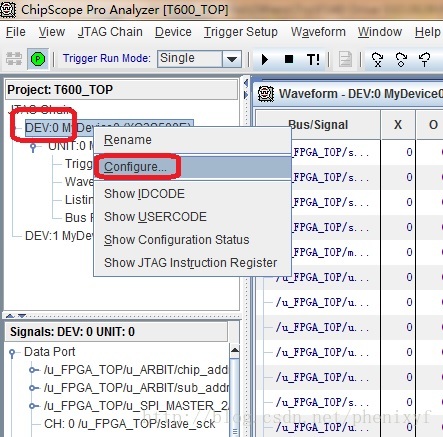

因直接配置给FPGA,所以右键DEV:0

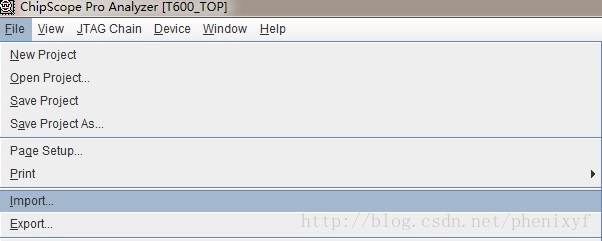

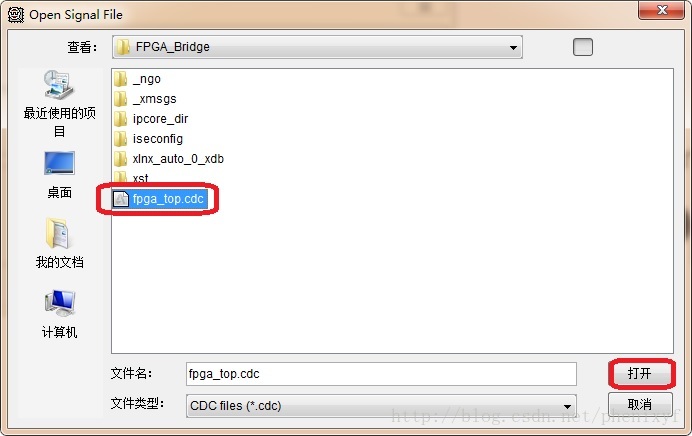

3.3 导入cdc文件

File -> Import

3.4 Trigger 设置

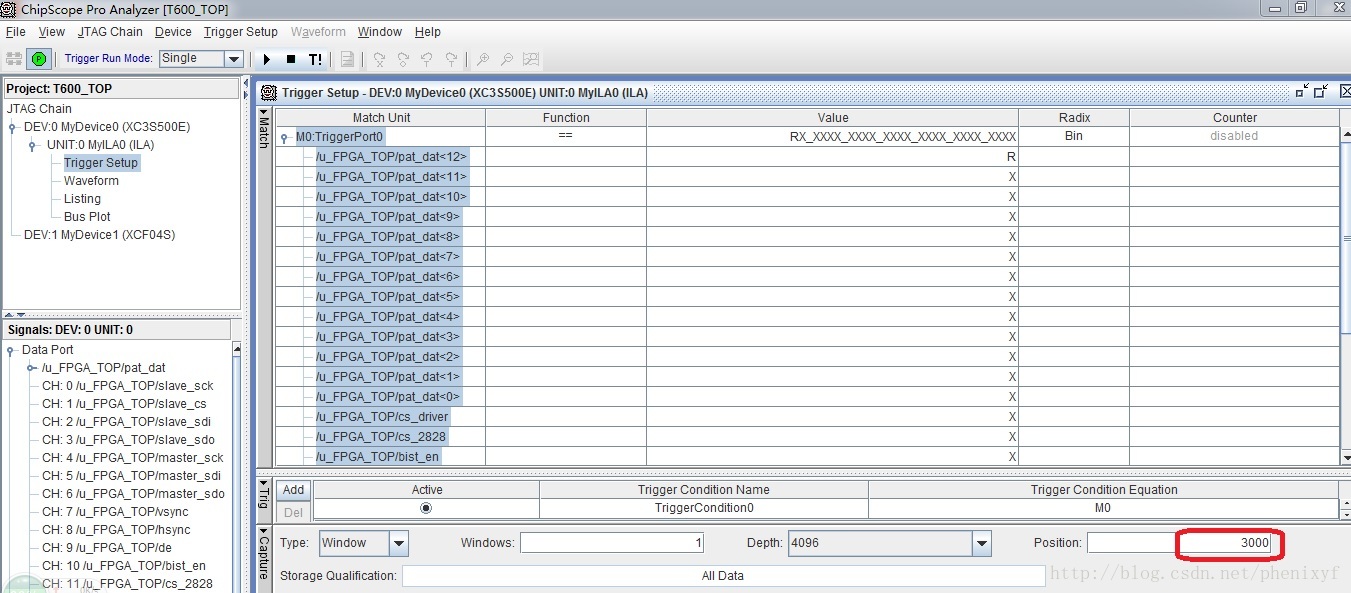

先点击Trigger Setup,然后在右边的观察信号组中,点击一下M0:TriggerPort0,将之前所选信号展开。

设置触发条件,在所选触发信号的Value栏中填写触发条件,R代表上升沿,F代表下降沿。

设置监测位置:下图中的值代表从触发位置往前的距离,整个监测宽度由2.2.2中设定,所以此值不能大于2.2.2中的设定值(本例为4096)

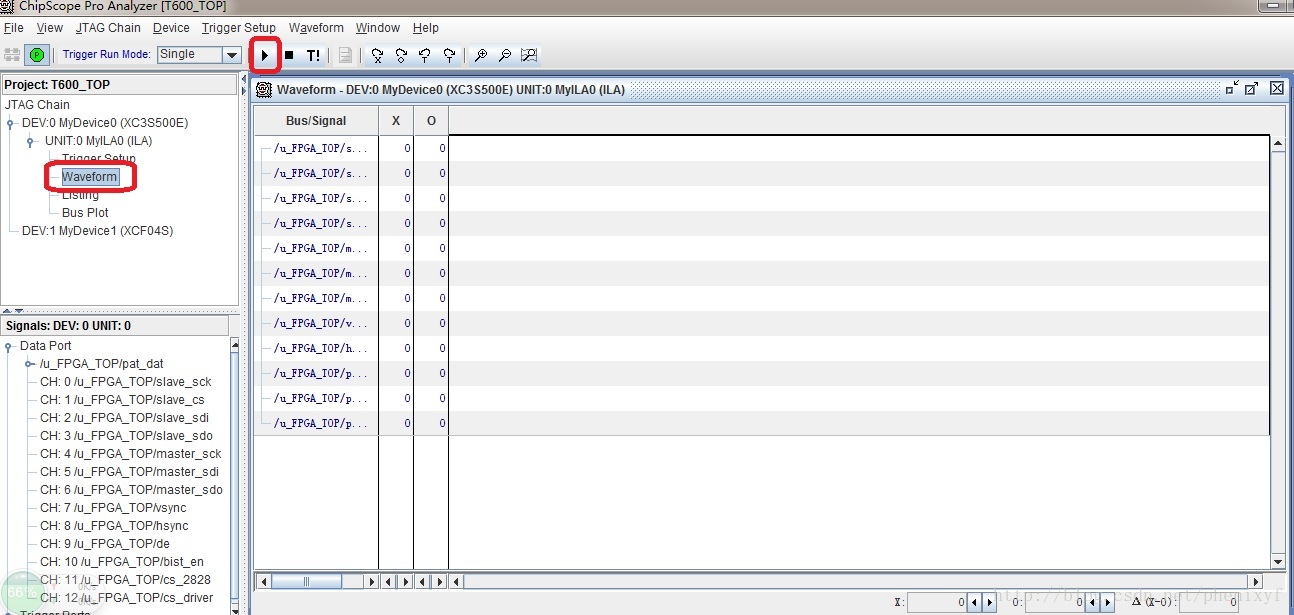

3.5 打开波形窗口,点击运行

当触发条件满足时,即产生相应波形

图中T!按钮代表实时触发,三角按钮代表触发一次。