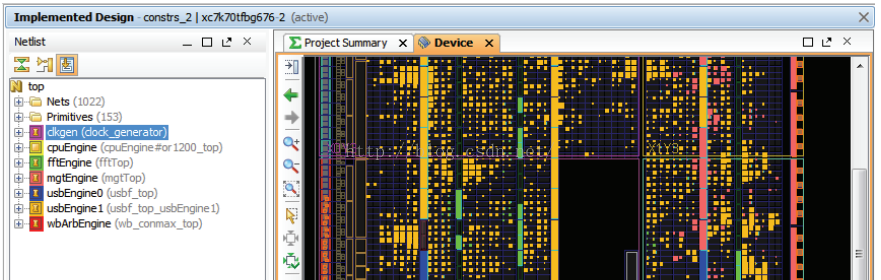

这个是高亮显示,找到clkgen点击右键,里面有一个选项,highlight primitive,就会把clkgen模块的相应逻辑变成一个颜色,这样就能知道这个模块的逻辑是怎么分布的了。

我毛华望QQ849886241。技术博客http://blog.csdn.net/my_share

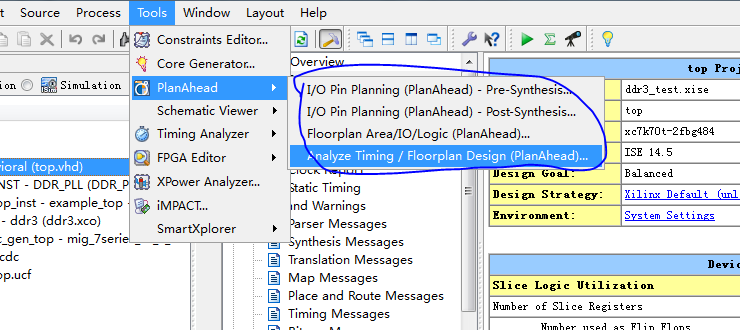

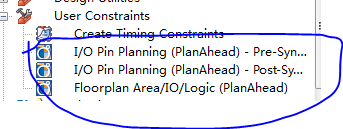

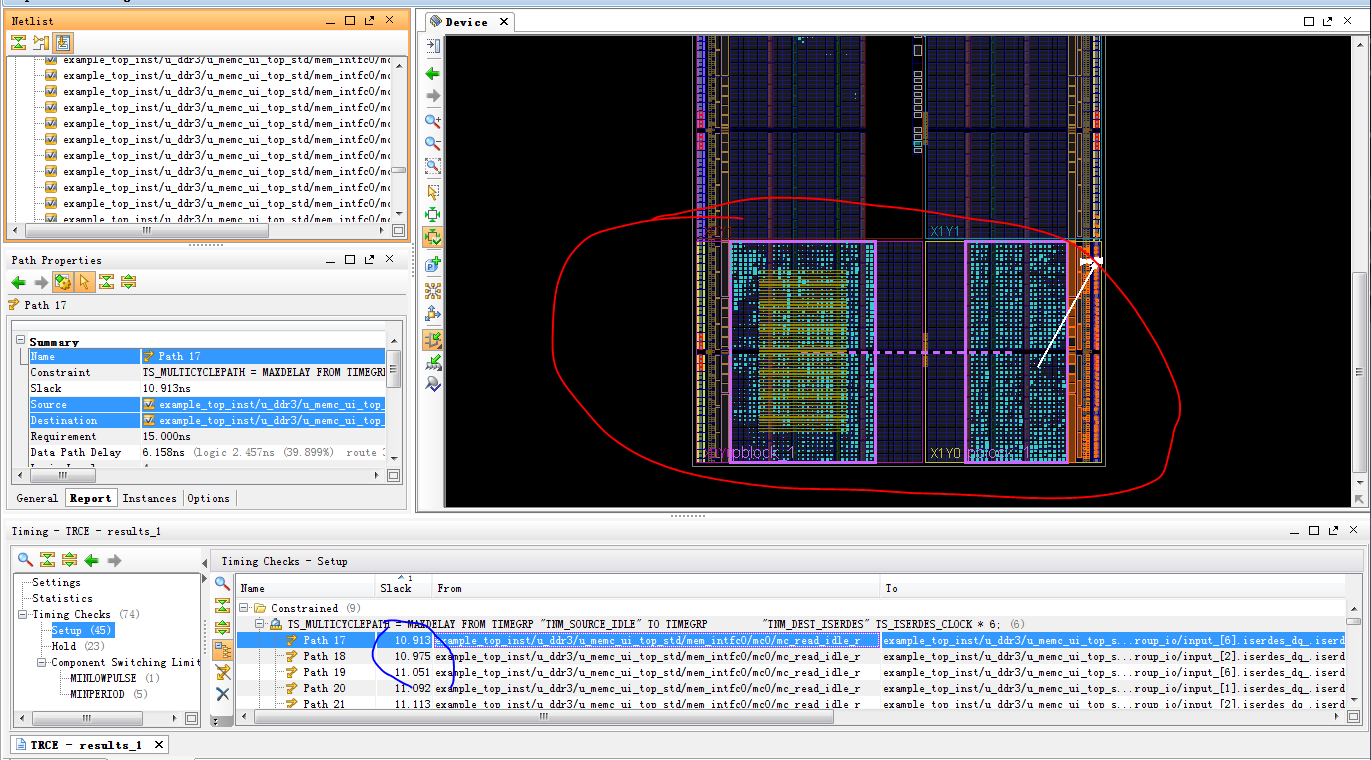

上面这两个方法,打开的界面都是同一个。我支持上面的方法,时序分析。

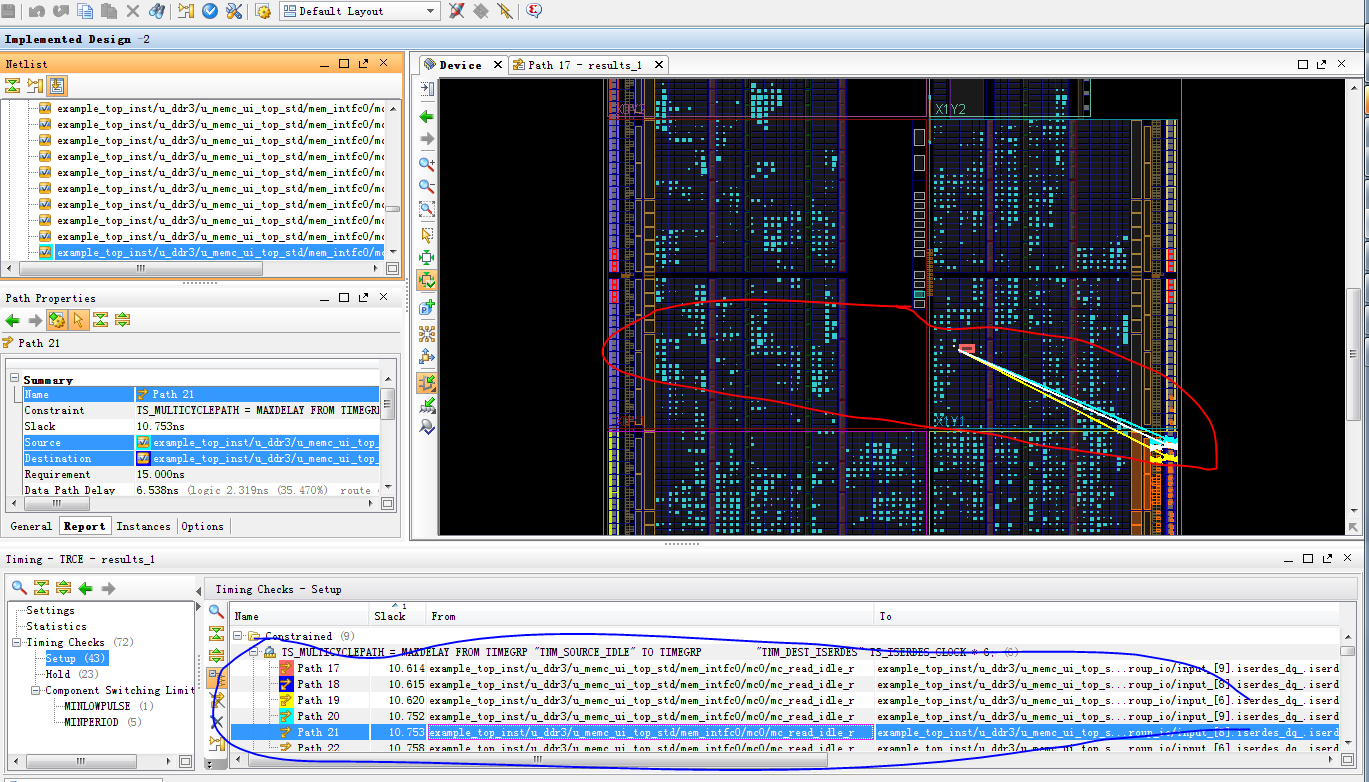

看清楚这两处,好像前面我写了一个高亮显示功能,好,我高亮一下。

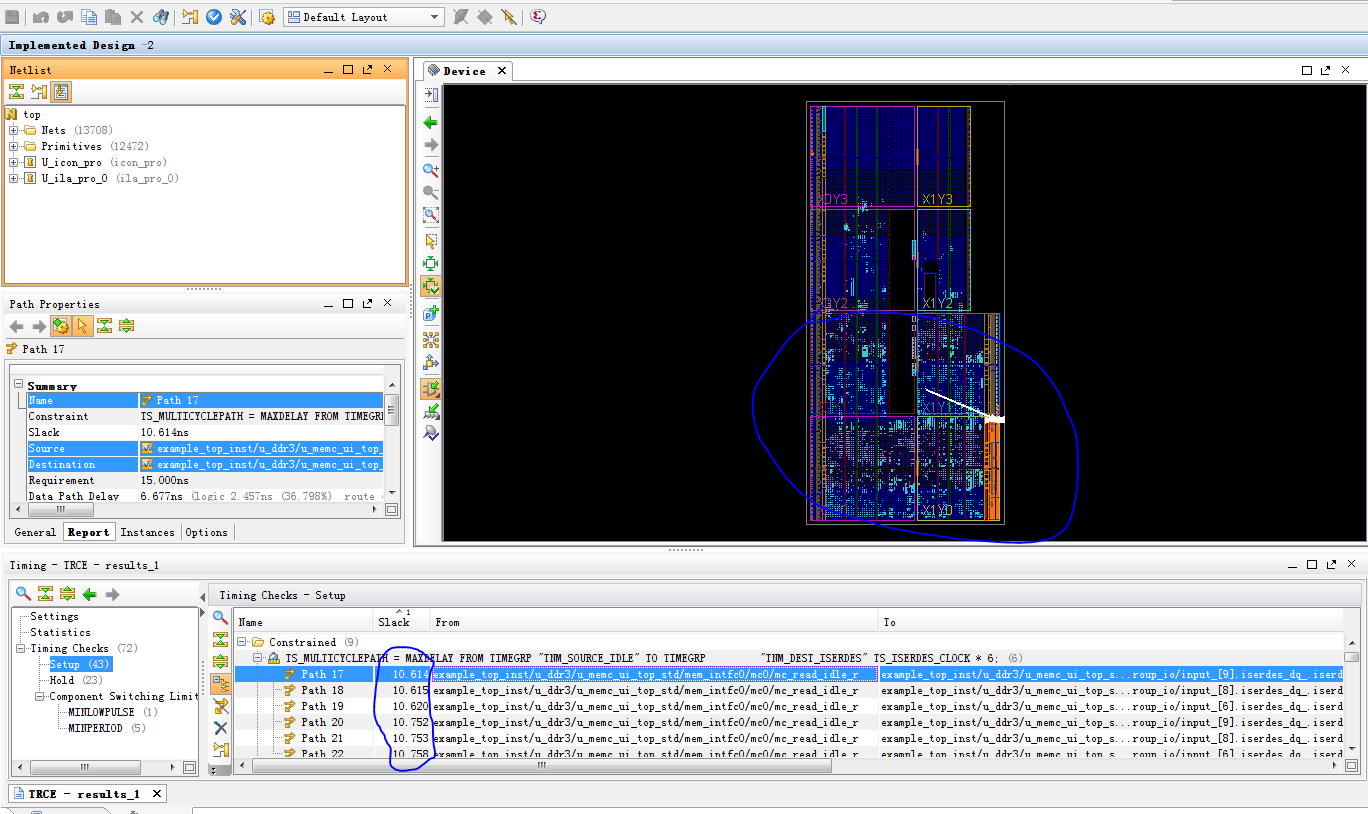

我对前面几个做了高亮显示。看出来了吧。来源都是同一点。整个元件的布局也好散。

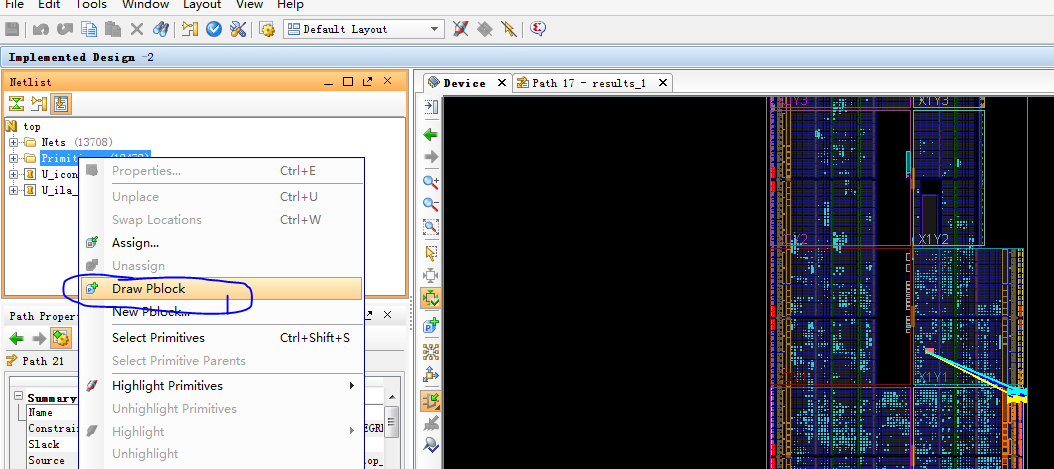

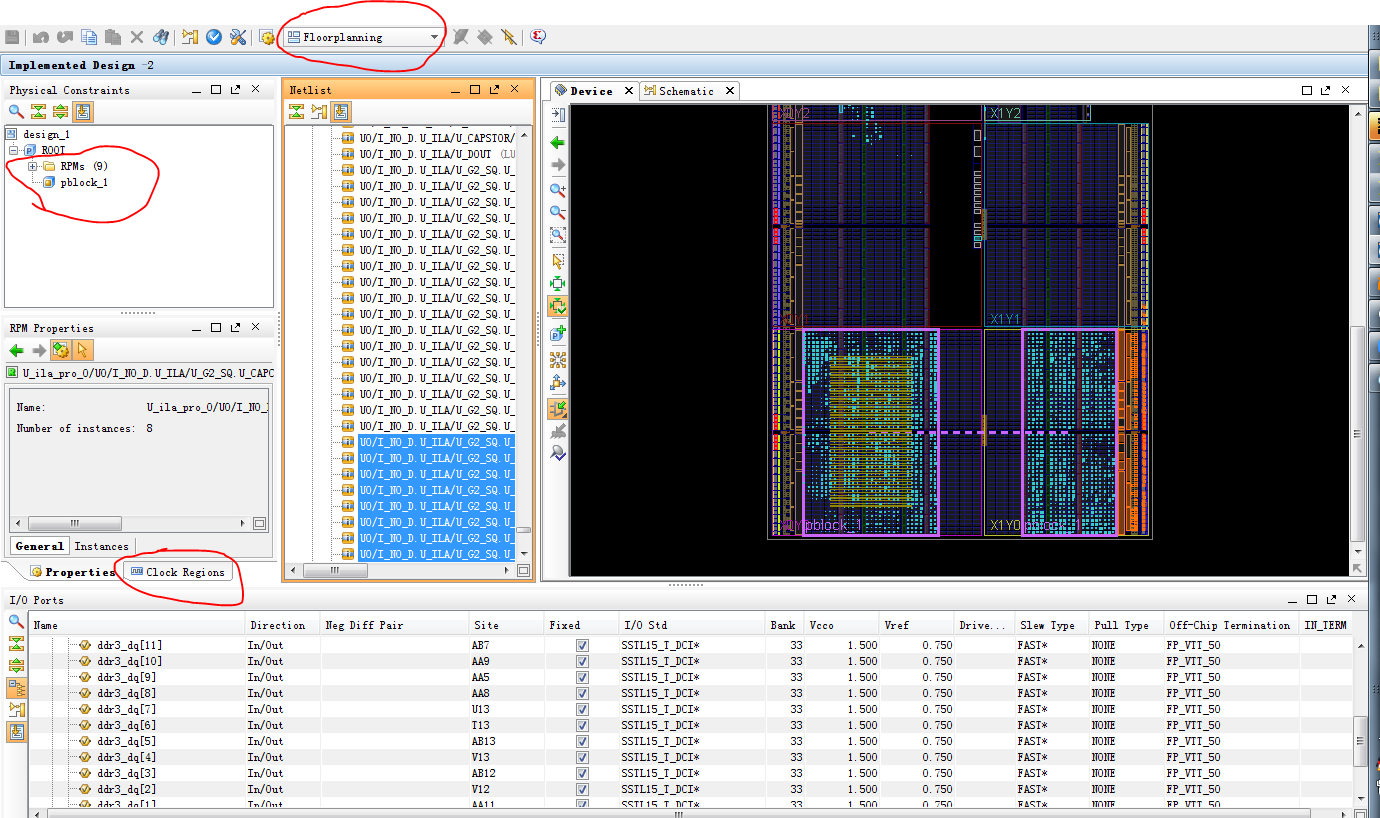

我来做一个区域锁定,

那一块区域是不够的,为什么把区域规划在那里,因为离引脚比较近。在添加一个区域。

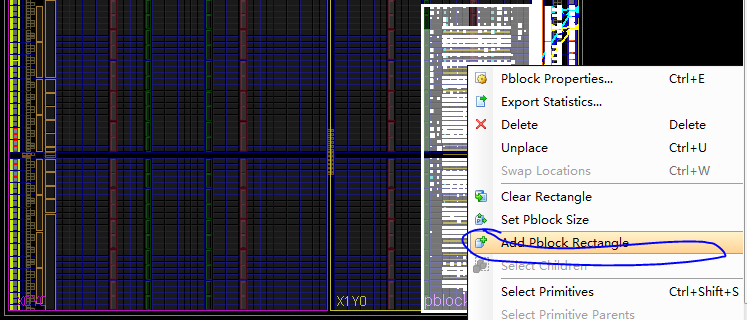

在添加一个最左侧的一块,

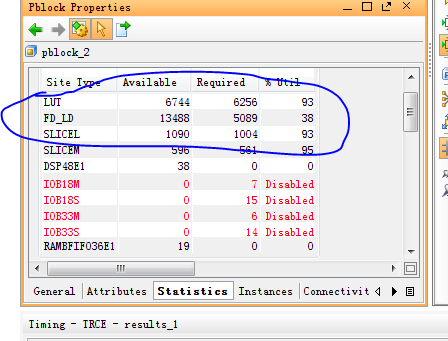

这个是区域划分报告,看来资源够了。至于下面那四个为何是红的,我还不了解。

当然了,图的下面还有几个栏,也都是目前的状态报告,自己看看。

保存,可以编译一下啦。

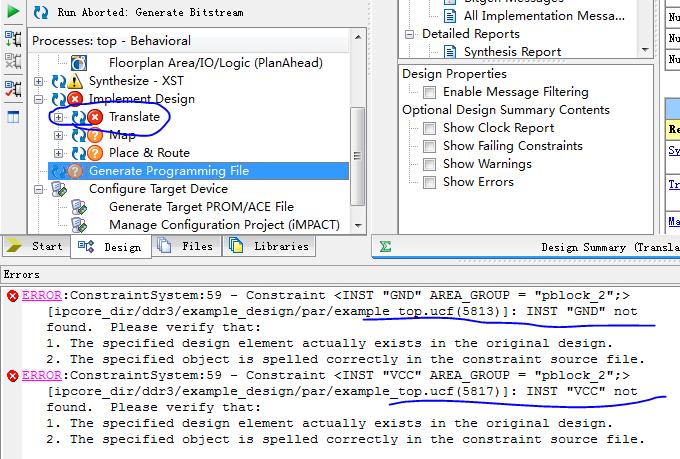

ERROR:ConstraintSystem:59 - Constraint <INST "VCC" AREA_GROUP = "pblock_2";>

[ipcore_dir/ddr3/example_design/par/example_top.ucf(5817)]: INST "VCC" not

found. Please verify that:

1. The specified design element actually exists in the original design.

2. The specified object is spelled correctly in the constraint source file.

报错嘛。有时候是难免的。查看ucf文件里面的那两行5817和5813.注释掉就可以了。

编译就可以通过了,有什么影响呢??能力有限还没看出多少影响。

如果给的地方太小了,就会编译不过去的。得留点空间。

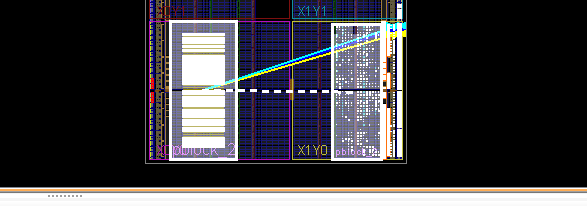

呵呵,富余量大了一点点吧。从图像上看,也离近了一些。我那些资源都集中在了我规划的地方。

当然了,随便规划一下,拿来学习用用而已啦。有点效果就好。

这个就是我更改的地方,界面就变成这样啦。引脚布局来着的。

planahead也就这么点好玩的了。随便点点左键右键。

我也就会这一点了。