参考文章链接:

https://blog.csdn.net/rill_zhen/article/details/8115756

http://www.cnblogs.com/liujinggang/p/9813863.html

http://www.eefocus.com/guoke1993102/blog/15-12/375730_3a621.html

一、软件平台

操作系统:windows 7

开发套件:ISE 14.7 ModelSim SE-64 10.1a

二、ChipScope Pro介绍

ChipScope Pro是一款在线调试工具,片上逻辑分析仪。她的主要功能是通过JTAG口,在线实时读取FPGA的内部信号。

ChipScope Pro的基本原理是利用FPGA中未使用的BlockRam,根据用户设定的触发条件将信号实时地保存到这些BlockRam中,然后通过JTAG口传送到计算机,最后在计算机屏幕上显示出时序波形。

ChipScope Pro工作时一般需要用户设计中实例化两种核:一是集成逻辑分析仪核(ILA core,Integrate Logic Analyzer core),该核主要用于提供触发核捕获的功能;二是集成控制核(ICON core,Integrated Contorller core),负责ILA core核便捷扫描端口(JTAG)的通信。一个ICON core可以连接1~15个ILA core。ChipScope Pro工作时,ILA core根据用户设置的触发条件捕获数据,然后在ICON core控制下,通过边界扫描端口上传到计算机,最后用ChipScope Pro Analyzerx显示信号波形。

ChipScope Pro有两种使用方法。第一种是由ChipScope Pro Core Generator根据设定条件生成在线逻辑分析仪IP核,包括ICON core、ILA core、ILA/ATC core 和IBA/OPB core等,之后在原HDL代码中实例化这些核,然后进行综合、布局布线、下载配置文件,就可以利用ChipScope Pro Analyzer设定的触发条件,观察信号波形。

第二种是原代码完成综合后,由ChipScope Pro Inserter工具插入ICON core和ILA core等核,它能自动完成在设计网表中插入这些核的工作,而不用手动在HDL代码中实例化这些核。本文主要讲解第二种方法。

三、方法二的使用流程

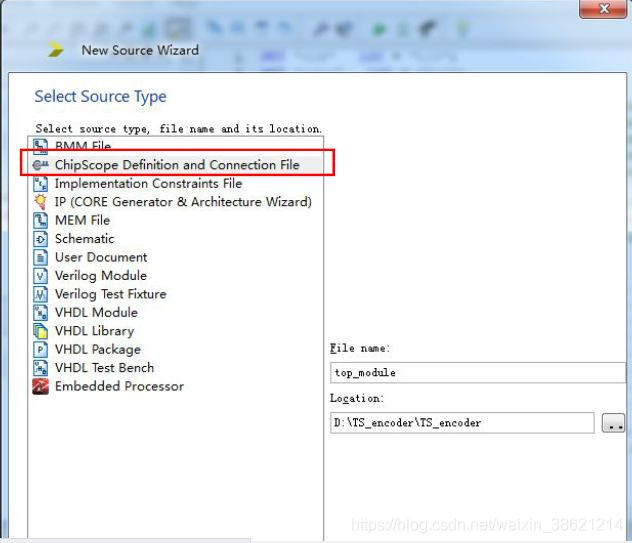

step1:new source->选择新建一个chipscope的核

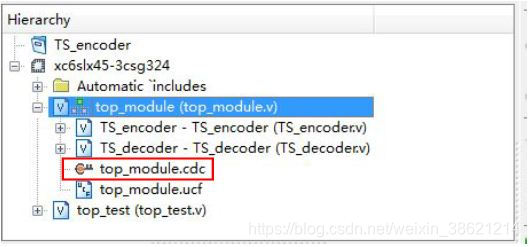

然后,可以看到在工程中有了chipscope的核.

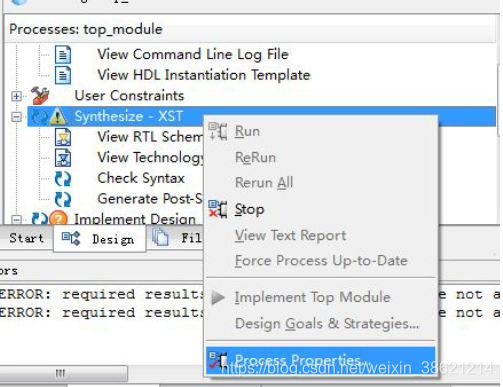

step2:打开.cdc文件。但在打开它之前,有一个很重要的操作,右键synthesize-XST,选择process properties.

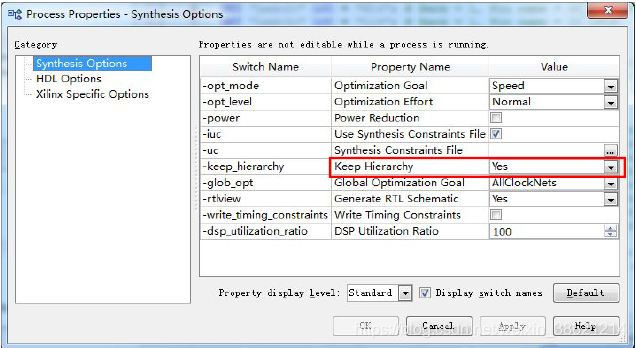

在keep hierarchy 中选择yes. 即设置综合时保持层次,这样在综合后的电路中会保持模块化,方便我们找到所想观察的信号。否则,很多信号会被优化掉,chipscope找不到想要的信号来观察。

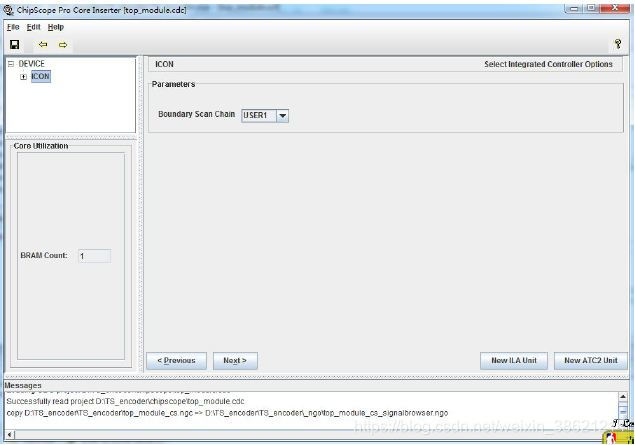

step3:设置chipscope,双击chipscope,会进入chipscope的操作界面,这个界面设置默认,点击next。

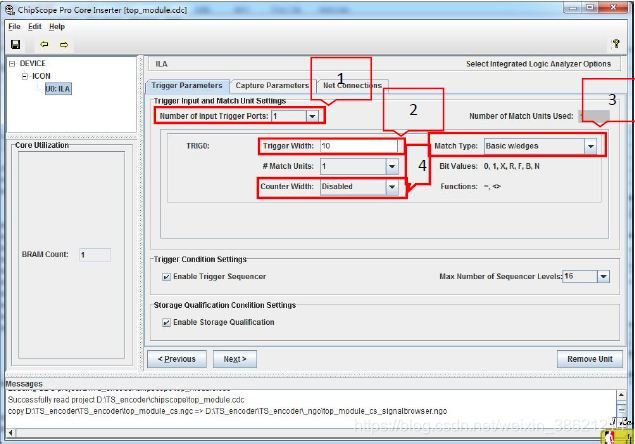

进入ILA的设置:

首先是trigger parameters:

标号1处表示触发端口个数,而每个触发端口又最大可以容纳下256位的数据(标号2处),也就是说大部分时候,只需要1个触发端口就够了。但是把需要观察的信号分布在几个触发端口里最好,不仅仅方便添加和删除。而且尤其对于一组总线信号来说,把他们单独放在一起,有利于观察信号时触发信号的设置(后面会提到)。

标号2处即该端口的信号宽度,最大为256位,这里设置的位数与后面的链接的信号数必须相符合,因此这里先填大一点,我一般直接写个32位,然后根据后面连接的信号数返回这里修改,不然当连接信号时发现位数不够又要先返回这里修改,再回去连接信号,比较麻烦。

标号3处设置触发条件,一般设置basic w/edges,这样可以设置当信号处于0,或1,或者上升,下降沿时触发。这里R代表上升沿,F代表下降沿,B应该代表只要发生变化就触发,N就不太清楚了,希望知道的可以告诉我,谢谢。

标号4处是计数器的设置,即同一触发条件发生多少次后,才开始触发,也可以设置为disable.

之后点击next.

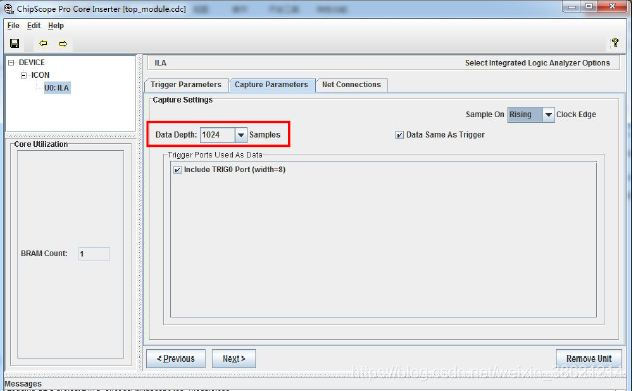

之后进入capture parameter, 这里主要设置的是取样深度,如果你需要一下取样到更多的信号,则将深度设置得大一点,当然,也更消耗资源就是。设置过多会造成FPGA的BRAM资源不足,提示错误。点击next。

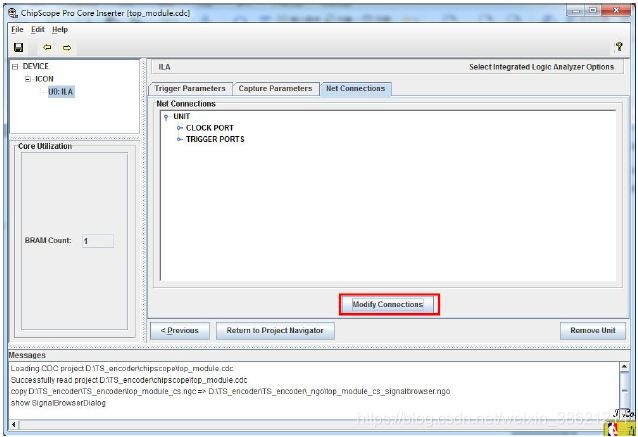

最后进入到net connections, 点击modify connections 来添加需要观察的信号。

进入到信号连接界面。

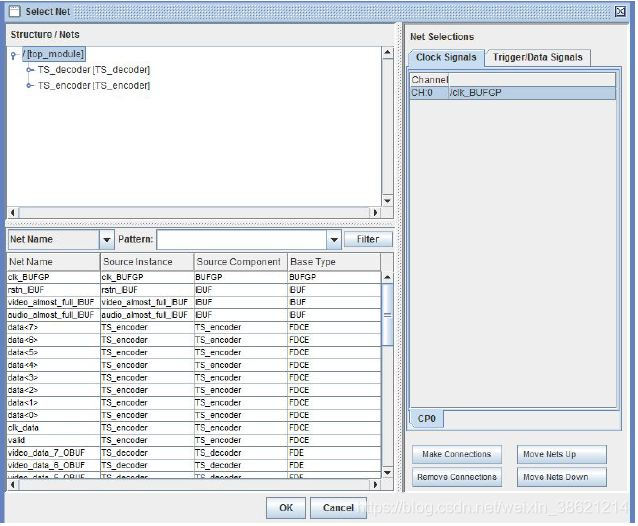

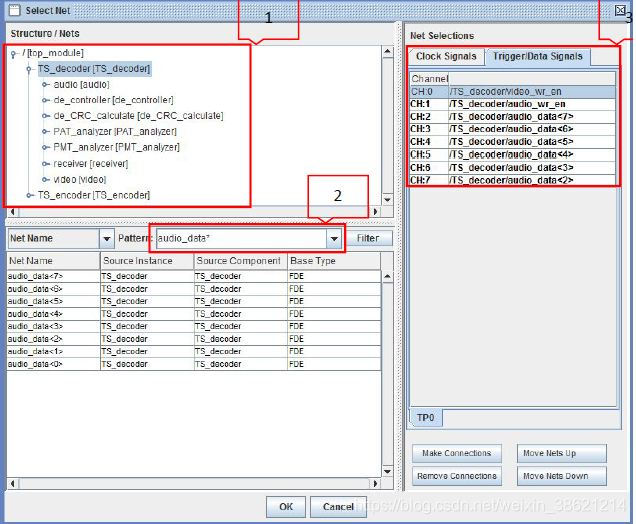

首要任务是添加采样时钟信号,一般是系统时钟,点击通道->选择信号->点击make connections即可。注意,这里连接的时钟输入都必须是带有buffer的信号,否则会报错。

然后就是其他信号的连接,但是这么多信号,如何找到自己需要的信号呢? 一就是可以在1处选择相应的模块,再寻找其中的信号,这就是为什么之前要设置保持层次的原因。

二就是可以使用的搜索功能,在2处输入信号名,后面需要带有*号!需有*号!需有*号!(重要的事说三遍),就可以找到选定模块里的对应信号了。

三处即为连接好的信号。点击OK。

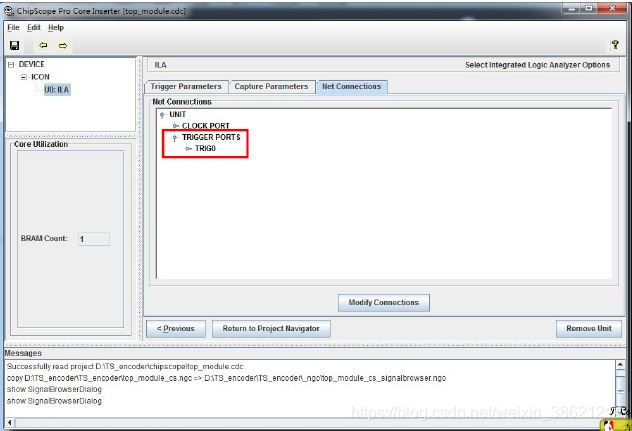

回到net connections. 如果连接的信号数与之前在trigger parameters中设置的宽度相同,则trigger port是黑色的。否则为红色,这时到trigger parameters中修改一下宽度即可。

保存后退出。

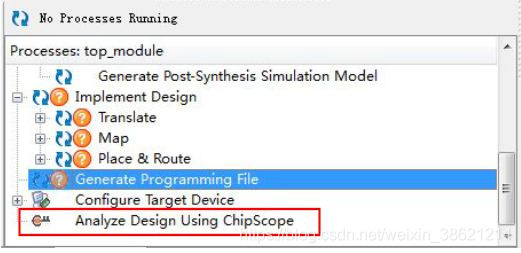

step4:生成bit文件。等待生成完毕后,点击下面的analyze design using chipscope.

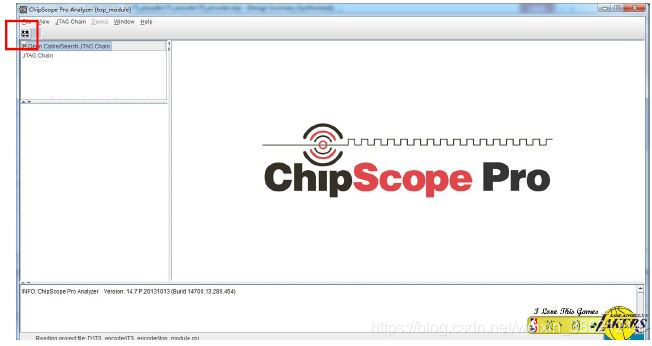

step5:点击左上角按钮,以跟开发板建立连接:

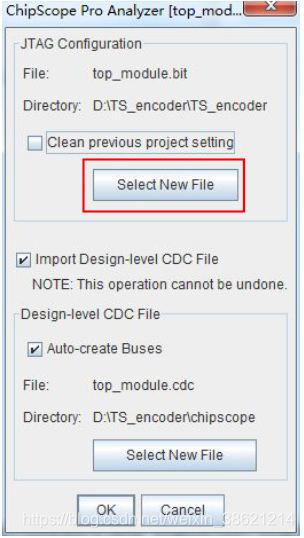

step6:连接好后,右键设备名称,点击configure……

点击select new file,选择需要下载的bit文件。

点击OK后,开始下载,右下角有进度条,就不贴图了。

然后有提示的话点击确认就好。

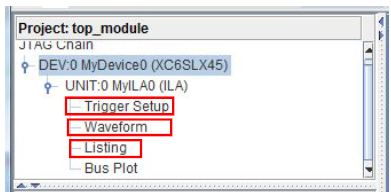

下载成功之后,软件会自动更新下面的窗口,这时可以看到下面出现触发端口,以及数据端口

step7:下面介绍下图窗口

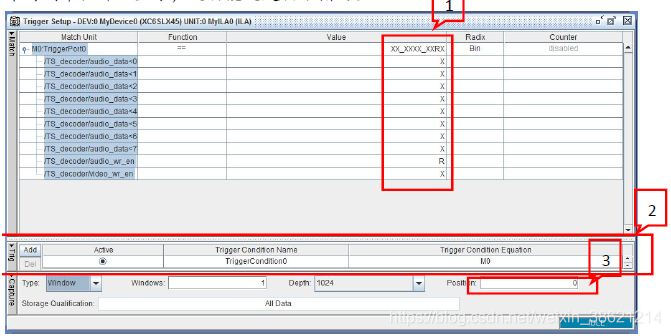

1,trigger setup, 即触发条件设置,点开右侧会出现如下窗口:

在1处设置高电平触发,低电平触发,上升沿触发,下降沿触发等,比如这里设置的就是在audio_wr_en上升沿的时候触发。另外,还可以设置整个触发端口为一个值时触发,这个对一组总线来说很有用,比如这里的audio_data, 这也就是为什么之前说把一组总线放在一个单独的触发端口比较好(这里没有单独放),就是为了这里更容易设置触发条件。

触发条件最好一次只设置一个,选择自己想观察的信号。

一般情况下,工程较大,需要查看的信号过多,但是取样深度设置的较小,这样会导致一次触发无法查看所有的信号。此时,可以选择不同的触发信号,只存储从触发信号开始的数据。

2处可以设置多组触发条件,方便改变触发条件

3处可以设置波形显示的位置,比如设置为100,则波形从触发条件的前100个时间单位开始显示,这功能还是挺不错的。

2, waveform, 波形窗口没什么好说的,大家应该都会用,提醒一下就是,右键信号可以选择信号颜色,这样方便突出重点信号,作为一个视觉动物,我觉得这个功能还是很nice的,毕竟chipscope实在太丑了,做项目有时候也挺枯燥的。

3,listing 这是一个和waveform同等的窗口,只不过它是通过表格来显示数据而已,因为有些数据用表格来看方便点。右键信号,是可以选择把它们添加到waveform或者listing的。而且listing中的数据还支持导出功能,在菜单栏的file中有导出选项,支持多种格式,这个就自己慢慢去玩了。

还有一个是bus plot,就是一个坐标图,看数据与时间的关系,以及数据与数据的关系,这里就不讨论了。

了解到了这些东西后,设置好触发条件,在trigger setup打开后,上面会有一个采样的控制台。可以选择单次触发,连续触发,实时触发。

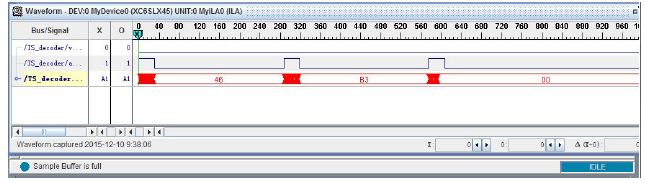

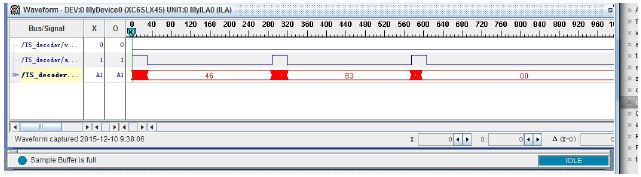

点击触发开始后,一旦触发条件满足,就可以看到采样到的信号了:

四、如何防止信号被优化

在一个复杂的设计中,我们往往会抓大量的信号,而ISE14.7编译代码的时候会把一些有相同逻辑的信号给优化掉,这会导致我们在选择信号的时候找不到想要抓取的信号,针对这种情况给大家提供两个解决办法。

方法一:

1、在你想要抓取的所有信号前面加上(*KEEP = “TRUE”*)

(*KEEP = "TRUE"*)reg [3:0] R_cnt;

方法二:

上面一种方法根据我的经验并不能100%的保证信号不被综合掉,所以还有另外一种方法是写一段冗余逻辑把信号进行运算然后赋值给一个输出,并把输出引到顶层绑定一个空闲的管脚,这种情况我的处理方法是:

假设要抓取的信号是(*KEEP = "TRUE"*)reg [3:0] R_cnt;

1、定义1个输出信号O_test;

Output O_test;

2、把要抓取的信号各位相或然后赋值给O_test

assign O_test = | R_cnt ;

R_cnt前面的“|”表示把R_cnt的每一bit按位相或,这行代码和

assign O_test = R_cnt[0] | R_cnt[1] | R_cnt[2] ;

综合出来的逻辑是一模一样的

3、把O_test引到顶层并在约束文件中分配一个空余管脚

通过这种增加冗余逻辑的方式,R_cnt信号一般不会被综合掉,我自己在平时的使用中会先使用第一种方法,如果发现第一种方法还是把我想看的关键信号综合掉了的话就采用第二种方法。