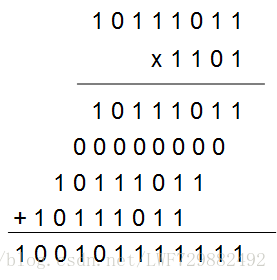

两个二进制数相乘的计算见下图1:

图1:二进制数相乘

实质是根据被乘数(1011_1011)根据乘数(1101)进行移位相加,具体来说,data_out[11:0] = 1011_1011<<3 + 1011_1011<<2 + 1011_1011。

相关:

1.用加法实现a*5/16功能(要求四舍五入),输入为a,10bit位宽,输出结果为result。请写出下面add_temp、result信号的位宽,完成下面的填空 [注:实质为下边所提及的浮点数乘法]。

wire[10:0] add_temp; //位宽判断时取a=10'b11_1111_1111带入时得到add_temp=11'b111_1111_1011

wire[6:0] result;

assign add_temp = a<<2 + a<<0; //左移n位=*2^n

assign result = add_temp>>4;2.进行一个运算单元的设计,实现A[7:0]*1111_1011,请尽量用最少的资源实现。

reg [7:0] A;

reg [14:0] B; //最大左移7位,故最高位为第[14]位

assign B = A;

wire [15:0] C; //直接加一位,或者令A=8'b1111_1111带入得C=16'b1111_1010_0000_0101故最大位宽为16

assign C = B<<7 + B<<6 + B<<5 + B<<4 + B<<3 + B<<1 + B<<0;---------------------------------------------------分----割----线------------------------------------------------------------

/*Ver. 2.0 在1.0“两二进制数相乘”的基础上补充“一个数与浮点数相乘”*/

今天群里讨论到一个数与浮点数0.0556相乘输出结果:浮点数0.0556 = A/B,其中,A为一个多项式,B为一个量化数,为2^n。

假设量化数B为128,则:A=0.0556*128=7,原理见下:

逻辑代码实现见下:

// *******************

// INFORMATION

// *******************

// 0.0556 ≈ 7/128 = (2^2 + 2^1 + 2^0)/(2^7)

// 0.0556 ≈ 14/256

// 0.0556 ≈ 28/512

// 0.0556 ≈ 57/1024 = (2^5 + 2^4 + 2^3 + 2^0)/(2^10)

module MULTI (

input [15:0] din ,

output [16:0] dout

);

//WIRES

wire [16:0] a;

wire [16:0] b;

wire [16:0] c;

wire [16:0] d;

//*********************

//MAIN CORE

//*********************

assign a = din << 2;

assign b = din << 1;

assign c = din << 0;

assign d = a + b + c;

assign dout = d >> 7;

//*********************

endmodule其实这样计算下来的精度还不是很理想,故提高量化精度,B取1024,则A=57,类似的,关键代码如下:

//*********************

//MAIN CORE

//*********************

assign a = din << 5;

assign b = din << 4;

assign c = din << 3;

assign d = din << 0; // 'd57=2'b11_1001

assign e = a + b + c + d;

assign dout = e >> 10; // 右移除以1024/*End for Ver. 2.0 2018-7-17 12:30:16*/

Reference:

1.基于FPGA的8位移位相加型硬件乘法器的设计_张建妮;