Achievement provides the only real pleasure in life.

有所成就是人生唯一的真正的樂趣。

通过xilinx vivado提供给implementment,可以看到实际情况(vivado 2017.4 kintex 7为例):

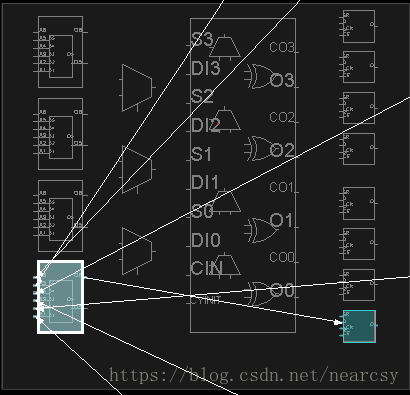

每个CLB包括两个slice(两个SLICEL或者一个SLICEM一个SLICEM·)---8个6输入LUTs(逻辑产生单元),16个FF,以及3个Multiplexer(F7AMUX/F7BMUX/F8MUX)和carry chain组成。

LUT:由6个独立的输入A1-A6和两个独立的输出组成O5、O6。

能够实现:

1. 任意的6输入布尔逻辑:A1-A6作为输入,O6作为输出。

2. 两个5输入或者更少的:A1-A5作为输入,A6高,O5和O6作为输出。

经过LUTs的信号可以:不做操作(直接出来slice)/从O6出来进入XOR专用门/从O5出来进入进位链/接入D触发器输入/从O6进入F7AMUX/F7BMUX。F7AMUX和F7BMUX作用是组合4个LUTs,在一个slice中产生任意的7或者8输入。对于大于8输入的逻辑,则需要多个slice。值得注意的是对于大于8输入的多个slice,没有直接连接在一起。

下面深入理解一下上面文档的含义:

always@(posedge sys_clk)

begin

case(key_in)

6'b000_001: key_edge <= 1'b1;

6'b000_010: key_edge <= 1'b0;

6'b000_100: key_edge <= 1'b1;

6'b001_000: key_edge <= 1'b0;

6'b010_000: key_edge <= 1'b1;

6'b100_000: key_edge <= 1'b0;

default:key_edge <= 1'b1;

endcase

end

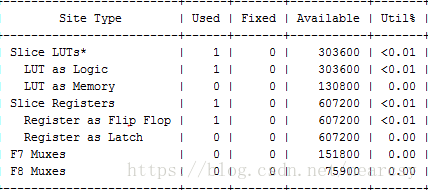

在资源报告中,只占用了一个LUT和1一个FF。可以看出,7series的fpga的确是6输入的LUT(A1-A6),输出O6,直接接在FF上。