XILINX 7系列FPGA_SelectIO篇

0.转载说明

FPGA适合数据的并发性处理,但是数据从何而来,这就是本文所要说的SelectIO——数据传输的先锋部队

Ultrascale+系列与7系列FPGA的SelectIO结构差别还是非常大的,后面有机会会总结出来。

原文链接:

xilinx 7系列FPGA之SelectIO 篇(1)_IO接口简介

xilinx7系列FPGASelectIO篇(2)_IO逻辑资源简介

xilinx 7系列FPGA之SelectIO(3)_高级IO逻辑资源简介

xilinx7系列FPGA之IO_FIFO篇简介

原文图片均参考自

7 Series FPGAs SelectIO Resources User Guide

1.IO接口简介

从本篇开始的接下来共三篇,咱们聊一聊xilinx 7系列FPGA的SelectIO。所谓SelectIO,就是I/O接口以及I/O逻辑的总称。SelectIO 篇可以分成3部分:第1部分介绍I/O的电气特性,第2部分介绍I/O逻辑资源,第3部分介绍高级的I/O逻辑资源(serializer/deserializer)。本篇咱们来说说xilinx 7系列FPGA的I/O的电气特性。

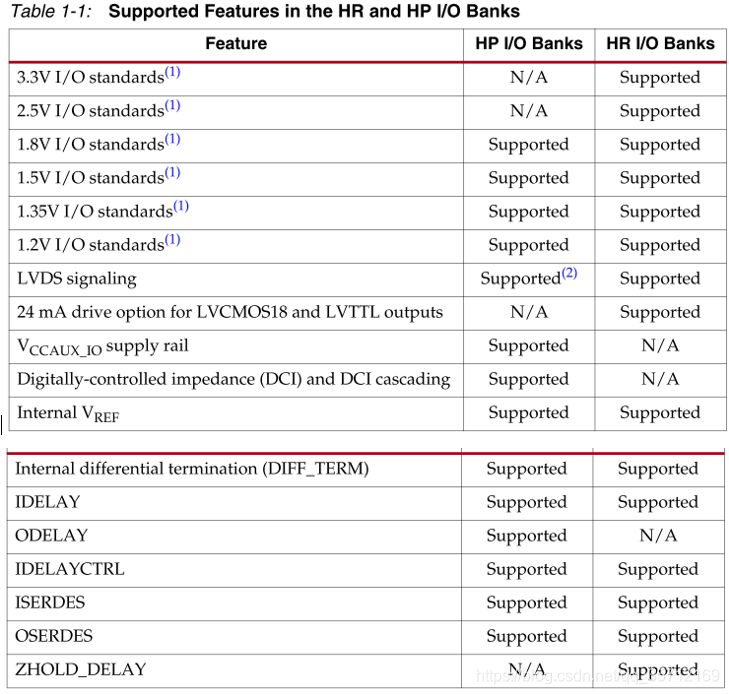

说到I/O,咱们必须先提到FPGA的BANK。在7系列的FPGA中,BANK分为HR(High-range)BANK和HP(High-performance) BANK。HP BANK只能支持小于等于1.8V电平标准的I/O信号,HR BANK则支持小于等于3.3V电平标准的I/O信号。HP BANK专为高速I/O信号设计,支持DCI(数控阻抗),而HR BANK则适合更大众化的所有I/O信号设计。下表列出了HP BANK 和HR BANK的特性。

无论是HR或者HP BNANK,每个BANK都包含50个I/O管脚,每个I/O管脚都可配置成输入、输出。每个BANK的首尾管脚只能作为单端I/O,其余48个I/O则可配置成24对差分I/O。

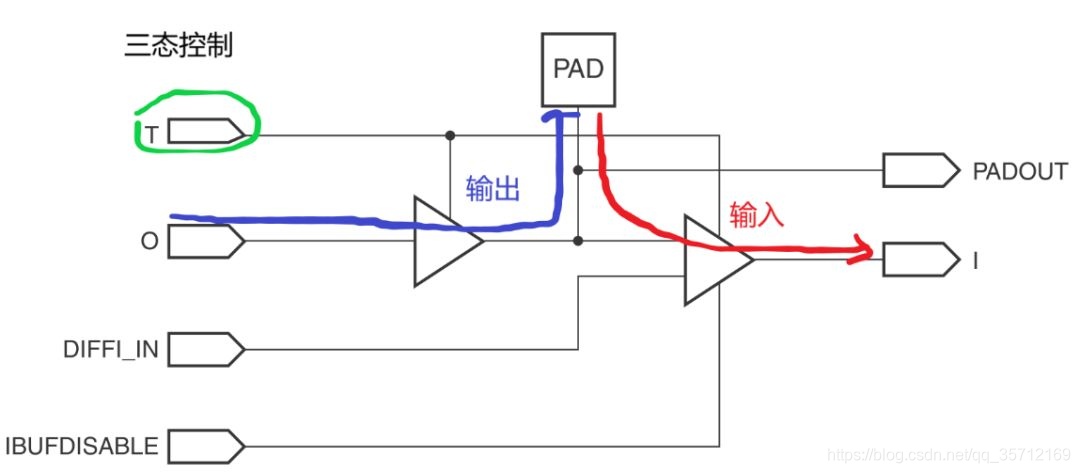

单端的I/O管脚支持LVTTL、LVCMOS、HSTL、PCI等等常用的电平标准。差分的I/O管脚则支持LVDS、差分HSTL等差分信号。但在其官方文档中,竟然没有描述支持很常用的LVPECL差分信号,甚是奇怪。如下图所示为1个I/O接口示意图(IOB):

总的来说,7系列FPGA同前几代相比,最大的区别就是:

- 多了专用于高速接口信号的HP BANK,该BANK最高只能支持1.8V电平。

- 每个BANK多达50个I/O。

其它电气性能基本保持一致,对咱们的使用不造成影响。

2.IO逻辑资源简介

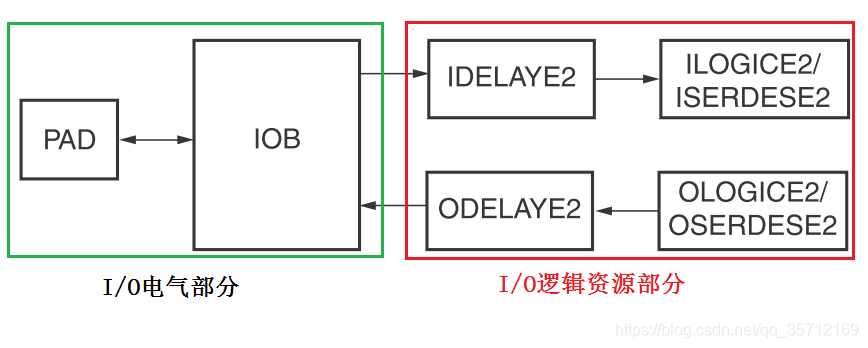

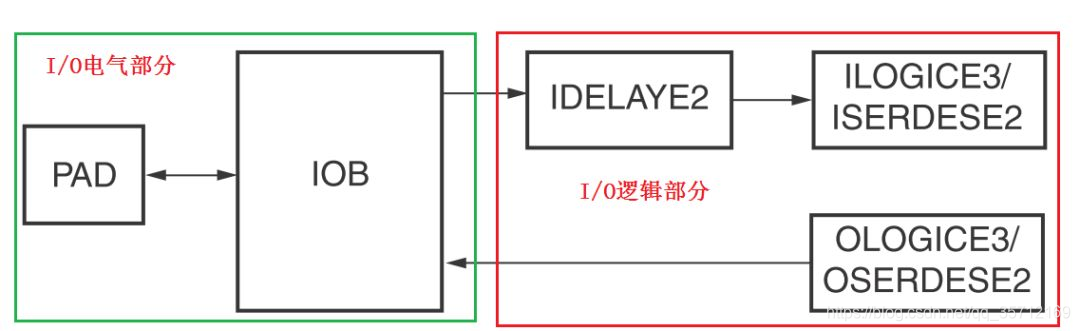

上篇咱们简单的说了I/O的电气特性,本篇咱们接着介绍I/O逻辑资源,先贴上两张图。图1为HPBANK的I/O模块,图2为HRBANK的I/O模块,两者区别在于后者无ODELAYE模块。

I/O逻辑资源主要包含5部分:

1, ILOGIC

ILOGIC即输入信号处理逻辑,紧挨着IOB,外界的输入信号最先经过的就是ILOGIC。ILOGIC是由许多的数据选择器和一个IDDR(input

Double data rate)触发器构成。该触发器既可以双沿捕获输入数据也可以拆分成普通单沿触发器。在HP BANK中,ILOGIC被称为ILOGICE2,在HR BANK中,ILOGIC被称为ILOGICE3。下图给出了ILOGICE3的示意图:

2, IDELAY

IDELAY被称为信号延迟模块,它的作用就是把信号延迟一段时间。对于一些需要对齐的输入信号来说,这至关重要。在7系列FPGA中,它被称为IDELAYE2。IDELAYE2可以将信号延迟0~31节,在这区间任意可调,并且每节的延迟精度约为78ps(1/(32×2×FREF),FREF为IDELAYCTRL的参考时钟)。下图为IDELAYE2例化框图。

3, IDELAYCTRL

IDELAYCTRL其实是个辅助模块,这么说吧,只要咱们使用了IDELAY或者ODELAY,IDELAYCTRL必须被使用,要不然就无法正常工作。因为IDELAY或者ODELAY的延迟精度是由IDELAYCTRL的输入时钟决定的,一般为200MHz。下图为IDELAYCTRL例化框图。

4, ODELAY

ODELAY和IDEALY的使用方式差不多,只不过ODELAY是用作输出信号的延迟。另外,HR BANK内没有ODELAY,HP BANK才有,被称为ODELAYE2。使用ODELAYE2时同样需要例化IDELAYCTRL。下图为ODELAYE2例化框图:

5, OLOGIC

LOGIC包括2个部分:一个用于配置输出路径。另外一个用于配置三态控制路径。输出路径和三态控制路径都可以独立配置成沿触发器、ODDR以及组合逻辑输出。

总得来说,I/O逻辑资源就是用来获取或者输出信号。对面一般的低速信号而言,I/O逻辑资源体现不出优势,用不用都不影响最终结果,但是对于高速信号而言,就必须使用I/O逻辑资源了,不能够正确使用它,整个FPGA逻辑代码完全无用。但是FPGA不就是用来处理高速信号的么?所以I/O这一块应该是整个FPGA的精华之处,当然也是使用最难的部分了。。。。。。

为了方便咱们使用I/O逻辑资源,xilinx公司专门将本篇介绍的几种模块集中起来,构成了功能强大的源语ISERDESE2和OSERDESE2,咱们只需要调用源语,正确使用源语就能够完成高级的I/O逻辑设计了,下篇咱们就聊聊高级逻辑资源ISERDESE2和OSERDESE2吧!

3.高级IO逻辑资源简介

上一篇咱们介绍了IO逻辑资源,本篇咱们来聊一聊高级的IO逻辑资源,即ISERDESE2模块和OSERDESE2模块。

所谓ISERDESE2模块,即Input serial-to-parallel converters。该模块的作用就是实现高速源同步输入数据的串并转换。

所谓OSERDESE2模块,即output parallel-to-serial converters。该模块的作用就是实现高速源同步输出数据的并串转换。

先说ISERDESE2。该模块接收外部输入FPGA的高速源同步串行信号,在FPGA内部将其转换为用户需要的并行数据信号。如图1所示为ISERDESE2的功能框图,咱们可以将按照功能分成5个部分:

1, 外部串行数据输入端

该部分接收外部输入的高速源同步数据,数据可以为SDR或者DDR。在SDR模式时,数据转换的位宽可以为2、3、4、5、6、7、8bit。在DDR模式时,数据转换位宽为4、6、8bit,当然如果是2个ISERDESE2级联使用,DDR模式可以支持10、14bit。

2, 时钟接口

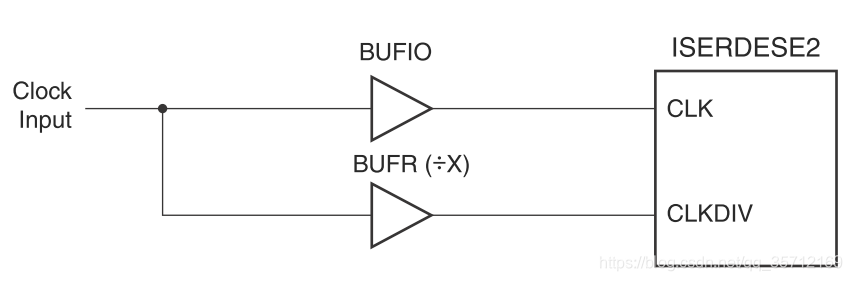

该部分提供ISERDESE2工作的高速源同步串行时钟、并行数据获取时钟以及控制时钟。如图2所示为源同步时钟接入ISERDESE2的用法。

3, 并行数据输出端

该接口就不用多说了,就是最终咱们需要的并行数据。SDR模式下为2、3、4、5、6、7、8bit,DDR模式下为4、6、8、10、14bit。

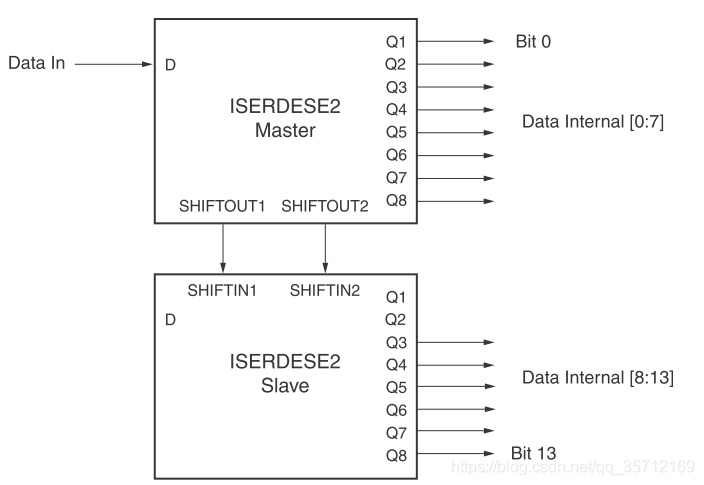

4, 级联接口

该接口是实现DDR模式下10bit、14bit位宽的关键接口,通过该接口与另外一个ISERDESE2级联,两者共同完成10bit、14bit数据的串并转换。如图3即为2个ISERDESE2的级联使用。

5, 数据对齐模块

该模块又称作Bitslip模块,用来实现并行数据的边界对齐。比如咱们外界串行输入的8bit的数据,经过串并转换后,能获取8bit的并行数据,但这并行数据可能存在前后8bit数据之间的错位,这是串并转换无法识别的,因此Bitslip就专门用来找到用户需要的并行数据边界。

图4给出了Bitslip是如何确定并行数据的边界:对于SDR模式,Bitslip使能1次,则数据会左移1次,对于8bit并行数据,移动8次完成一个循环,可以这样无止境的循环,直到找到用户定义的并行数据。对于DDR模式,Bitslip工作方式不同,Bitslip使能1次,数据会右移1次或者左移3次,两者交替进行,同样移动8次完成一个循环。

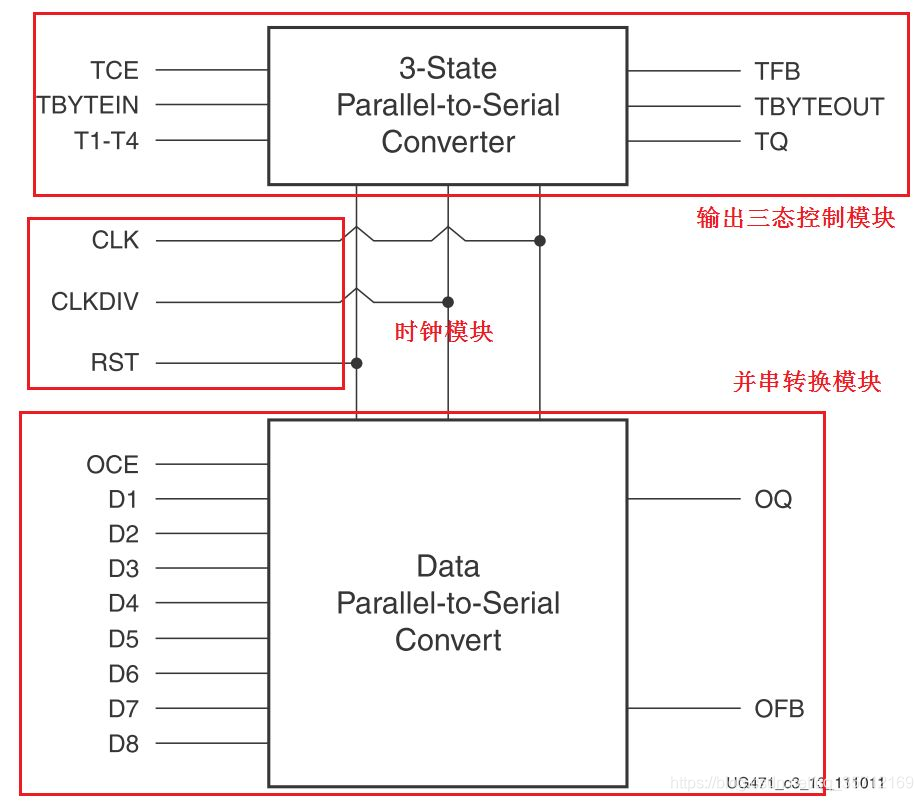

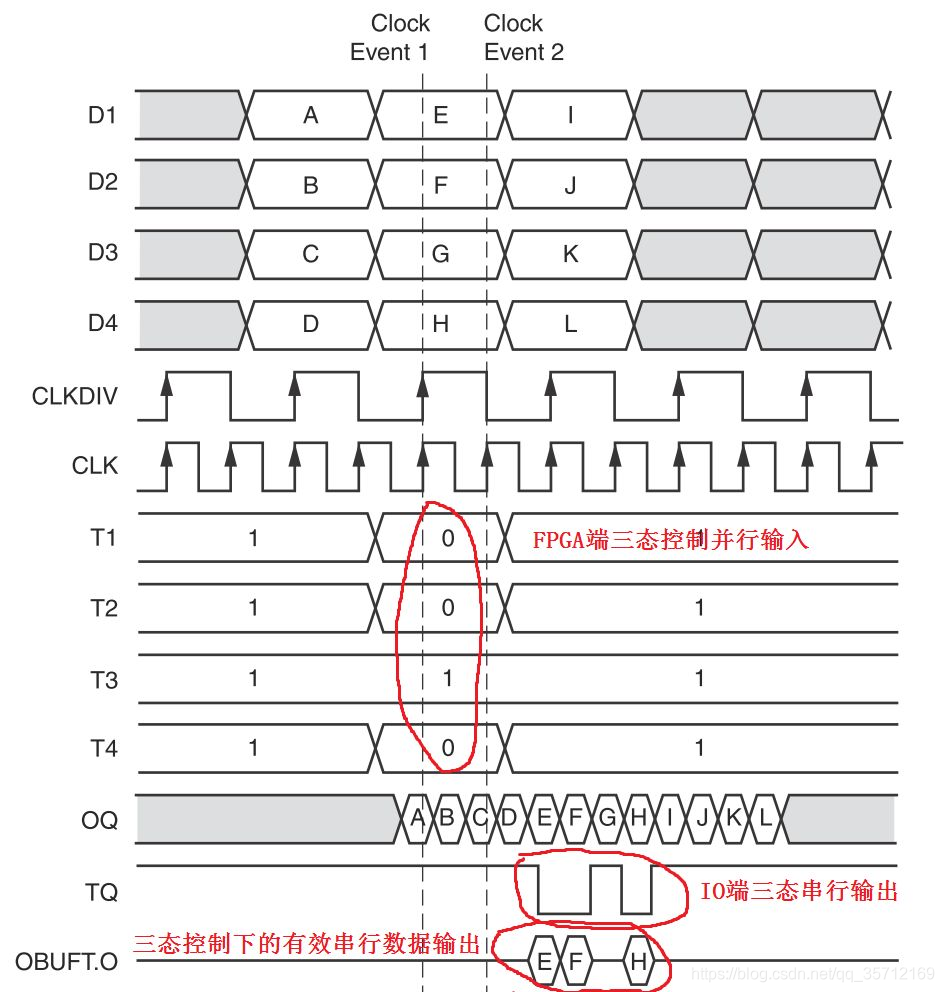

咱们再说OSERDESE2模块。该模块和ISERDESE2模块不同,少了Bitslip模块,多了一个三态控制模块,可以实现三态控制并串转换功能,数据的位宽和咱们介绍的ISERDESE2规则一样。如图5所示为其功能框图:

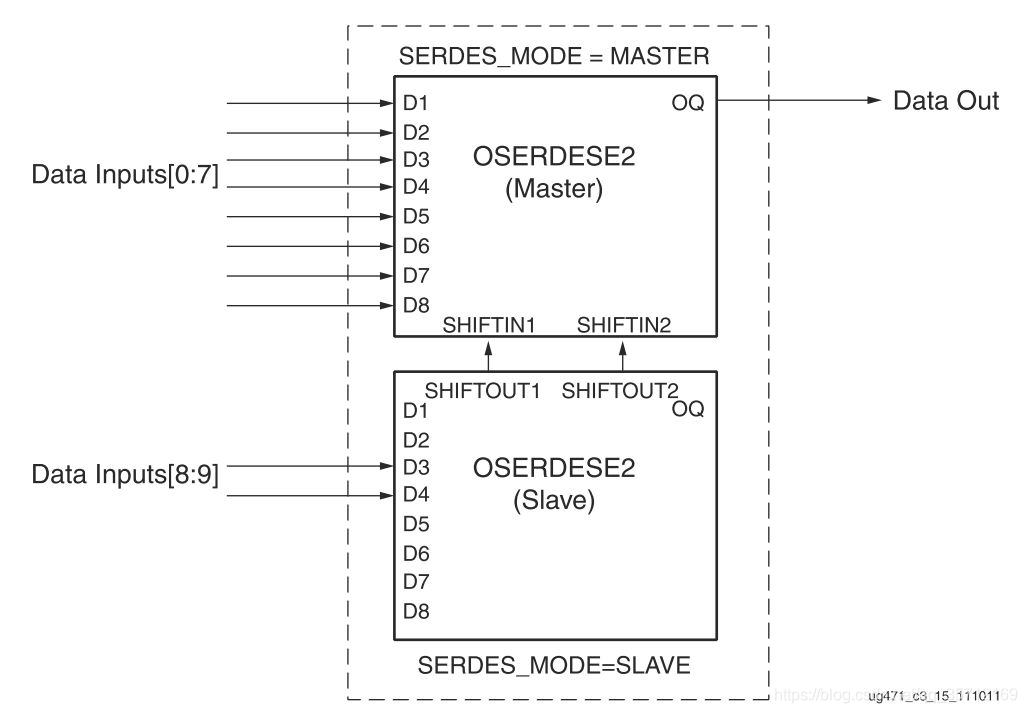

如图6所示为OSERDESE2的级联设计,实现10、14bit的并串转换功能:

OSERDESE2除了多出了一个三态控制模块,其它和ISERDESE2基本一样,只是数据流反相操作,因此咱们这里主要看一下三态控制模块,该模块主要功能就是实现串行数据流的三态输出,图7给出了三态控制的详细时序结构,从图上我们可以看到,三态控制下,串行数据流有选择性的输出E、F、H,实现了输出串行数据的三态控制。

本篇咱们很简要的介绍完了ISERDESE2和OSERDESE2,大家了解了吗?当然如果要实际使用的话,咱们还得看看具体数据手册啦!在上篇咱们就说过了,IO部分是FPGA内最复杂的部分,也是设计起来最难的部分,要熟悉使用它,咱们还得下功夫钻研!

4.IO_FIFO篇简介

前3篇咱们介绍了 SelectIO 逻辑资源,本篇咱们就聊一聊与SelectIO 逻辑资源水乳交融、相得益彰的另一个概念——IO_FIFO。

1个IO_FIFO包括1个IN_FIFO 和1个OUT_FIFO,它是7系列FPGA新设计的IO专用FIFO,主要用于IOLOGIC(例如ISERDES、IDDR、OSERDES或ODDR)逻辑功能的扩展。

FPGA的每个BANK有4个IN_FIFO和4个OUT_FIFO,相当于每12个IO对应1个IN_FIFO和1个OUT_FIFO。

IN_FIFO从ILOGIC接收4bit位宽的输入数据,但却可以输出4bit或者8bit位宽的数据到FPGA内部SLICE。OUT_FIFO正好相反,从OLOGIC接收4bit或者8bit位宽的输入数据,但却输出4bit位宽数据。

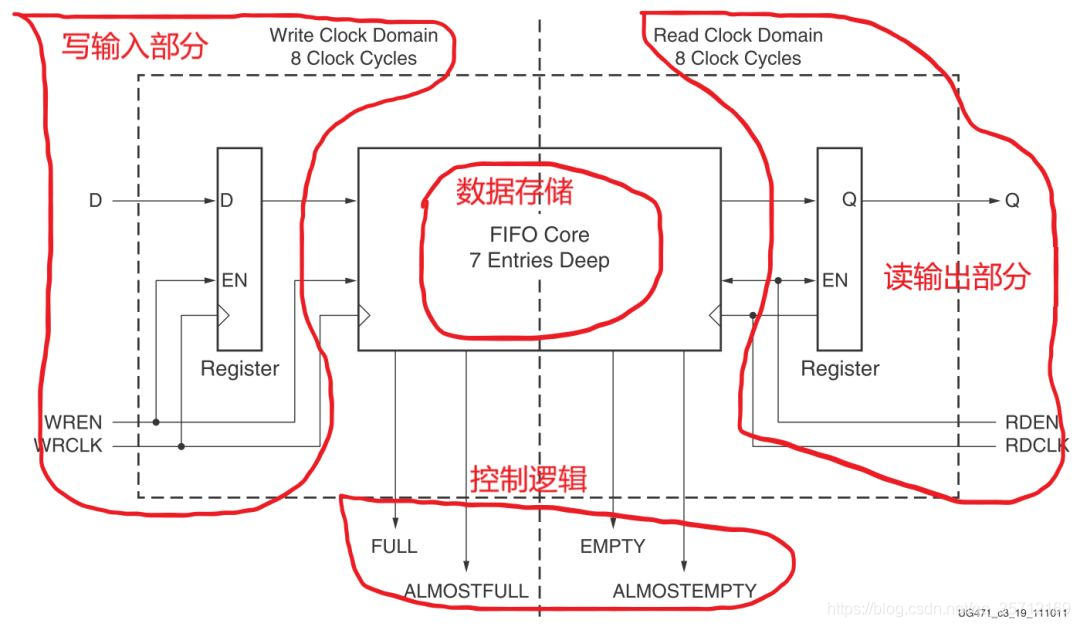

每一个IO_FIFO的存储大小为768bit,可以配置成12组4X4位宽数据的FIFO,也可以配置成10组4X8bit位宽数据的FIFO。每个IO_FIFO的深度为9。如图1所示为IO_FIFO的结构示意图:

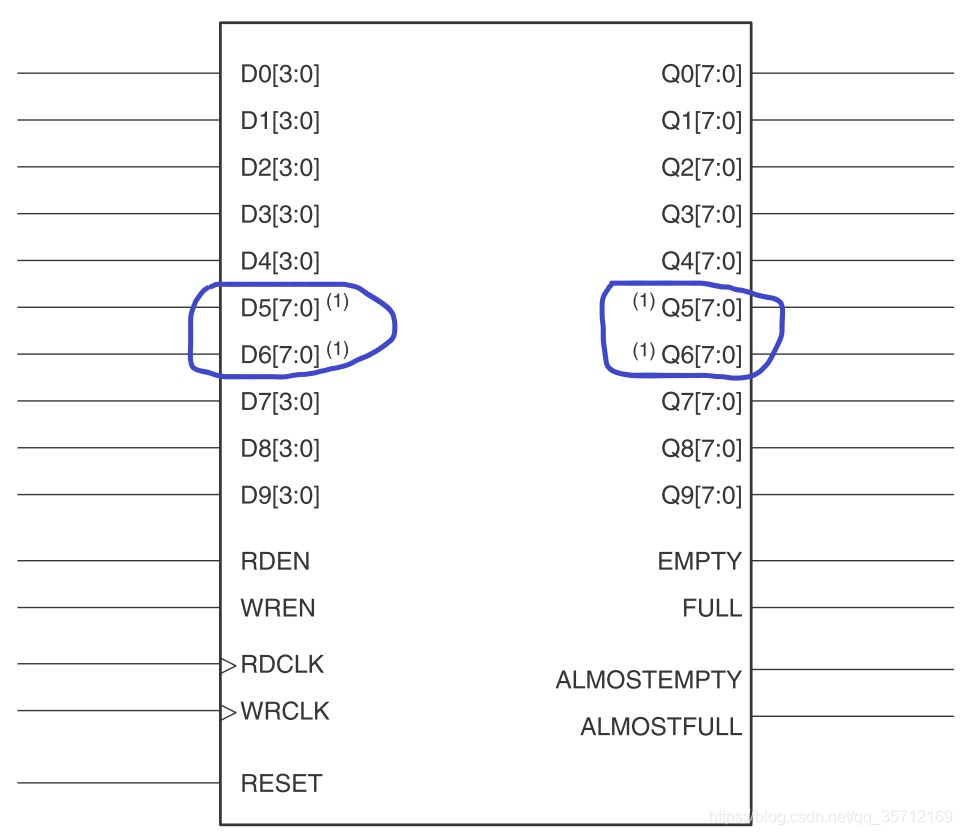

如图2所示为IN_FIFO的原语框图:

正如前面所说,当配置成12组的4bit位宽输入,4bit位宽输出时,输入D0[3:0]~ D9[3:0]对应输出Q0[3:0]~ Q9[3:0];输入D10[3:0]即为输入D5[7:4],对应输出Q5[7:4];输入D11[3:0]即为输入D6[7:4],对应输出Q6[7:4]。

当配置成10组4bit位宽输入,8bit位宽输出时,D0[3:0] ~ D9[3:0]对应输出Q0[7:0]~ Q9[7:0],此时写时钟频率是读时钟频率的2倍。OUT_FIFO和IN_FIFO操作过程正好相反,咱们这里就不罗嗦了。

总的来说,IO_FIFO其实就是存储深度比较小、位宽固定为4/8bit的普通FIFO ,7系列FPGA单独设计了这样的FIFO,更适用于IO接口处的字节\半字节数据缓存。

欢迎大家关注我创建的微信公众号——小白仓库

原创经验资料分享:包含但不仅限于FPGA、ARM、RISC-V、Linux、LabVIEW等软硬件开发,另外分享生活中的趣事以及感悟。目的是建立一个平台记录学习过的知识,并分享出来自认为有用的与感兴趣的道友相互交流进步。