浅谈XILINX FPGA CLB单元 汇总 (CLB、LUT、存储单元、Distributed RAM、移位寄存器、多路复用器、进位逻辑(Carry Logic))

一、概述

CLB可配置逻辑块是指实现各种逻辑功能的电路,是xilinx基本逻辑单元。

在Xilinx FPGA中,每个可配置逻辑块包含2个Slice。

每个Slice 包含查找表、寄存器、进位链和多个多数选择器构成。

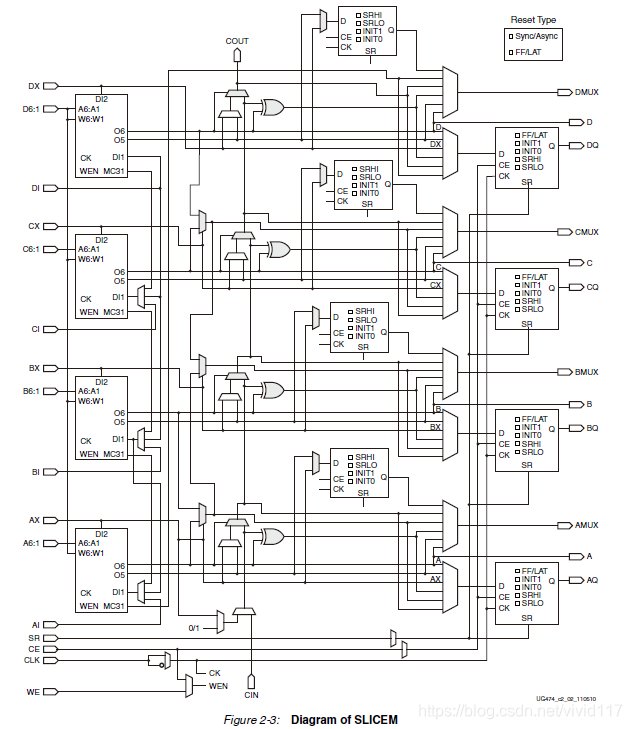

而Slice又有两种不同的逻辑片:SLICEM和SLICEL。SLICEM有多功能的LUT,可配置成移位寄存器,或者ROM和RAM。

逻辑片中的每个寄存器可以配置为锁存器使用。

本次主要介绍是掌握FPGA重要资源CLB、Slice、LUT。主要参考XILINX 官方文档“ ug474_7Series_CLB.pdf ”

二、CLB的介绍

1. CLB简述

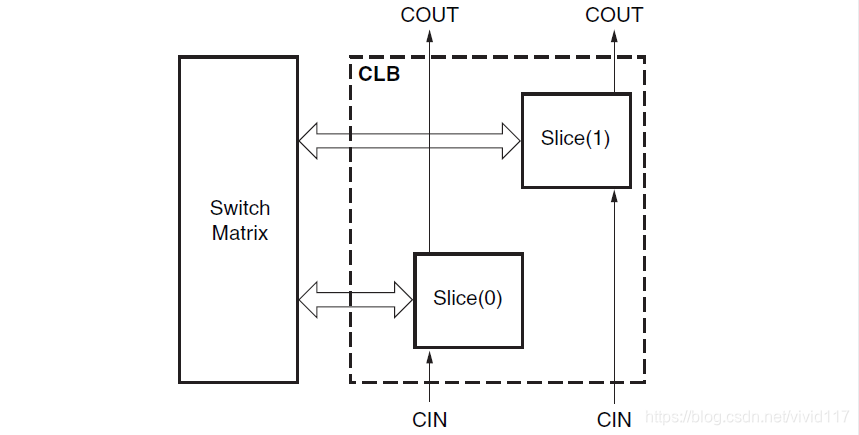

CLB是用于实现时序电路和组合电路的主要逻辑资源。 每个CLB元素都连接到一个交换矩阵,以访问通用路由矩阵(如下图所示)。 CLB元素包含一对Slice

2. CLB结构组成

7系列FPGA中的LUT可以配置为具有一个6输入LUT,或者两个5输入LUT(数据输入和地址相同,数据输出独立)。每个5输入LUT的输出都可以选择是否通过触发器(flip-flop)寄存。

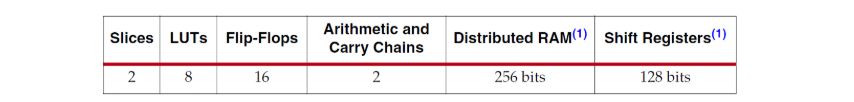

需要了解的是(下图是一个CLB的组成):

1)一个CLB 等于2个Slice

2)一个Slice等于4个6输入LUT+8个触发器(flip-flop)+算数运算逻辑 ——每个Slice的4个触发器(虽然有8个flip-flop,但是每个LUT分配一个flip-flop)可以配置成锁存器,这样会有4个触发器(flip-flop)未被使用。

3)这里还有一点需要特别注意的,XILINX FPGA 的slice还不都是长一样的,FPGA中三分之二的slice是SLICEL而剩余的是SLICEM。

注意:

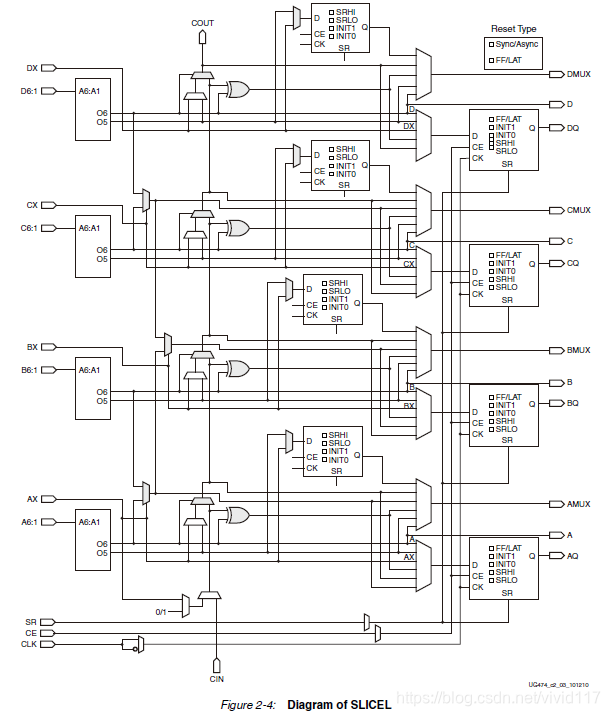

1)SLICEL 没有distributed RAM 和 shift registers

2)SLICEM是可以当作分布式64bit-RAM或者32bit的移位寄存器或者2个16bit移位寄存器。通过VIVADO软件或者原语的调用可以利用这些逻辑算数功能和存储功能。

所有slice均使用上面的元素来提供逻辑、算术和ROM功能。 此外某些slice还支持两个附加功能:使用分布式RAM存储数据和使用32位寄存器移位数据。 支持这些附加功能的slice称为SLICEM; 其他称为SLICEL。 SLICEM(下图所示)表示在所有slice中找到的元素和连接的超集。 SLICEL图下所示。 每个CLB可以包含两个SLICEL或一个SLICEL和一个SLICEM。

一个SLICEM类型的slice的结构

一个SLICEL类型的slice的结构

3. FPGA

我们经常说到FPGA容量是多少,FPGA器件的容量通常用逻辑单元来衡量,这在逻辑上等同于经典的4输入LUT和触发器。 7系列FPGA逻辑单元和6输入LUT的数量之比为1.6:1。所以,逻辑单元和Slice的数量比是6.4:1

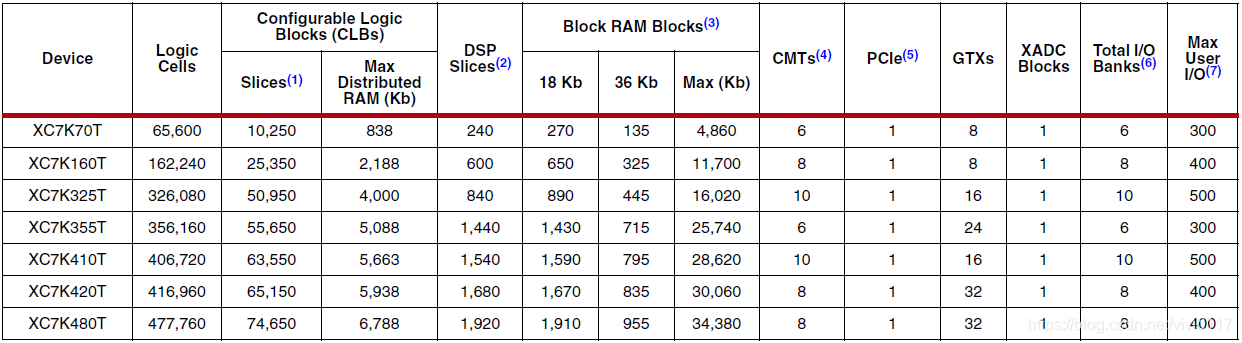

下图是ZYNQ xc2z020clg400-2器件的基本资源情况表:

三、CLB的各部分详细结构

1. CLB的功能

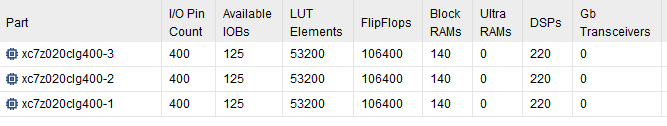

1)ASMBL体系结构

赛灵思创建了高级硅模块模块(ASMBL)架构,以使具有不同功能组合的FPGA平台能够针对不同的应用领域进行优化。

通过这种创新,Xilinx提供了更多的器件选择,使客户能够为他们的特定设计选择具有适当特性组合的FPGA。 下图提供了不同类型的基于列的资源的高级描述。

2)ASMBL体系结构的优点

ASMBL体系结构通过以下方式突破了传统的设计障碍:

•消除了几何布局约束,例如I / O数量与阵列大小之间的依存关系。

•通过允许将电源和地线放置在芯slice上的任何位置来增强芯slice上的电源和地线分布。

•允许彼此独立地扩展不同的集成IP块和周围资源。

2.查找表(LUT)

由于FPGA需要被反复烧写,它实现组合逻辑的基本结构不可能像ASIC那样通过固定的与非门来完成,而只能采用一种易于反复配置的结构。查找表可以很好地满足这一要求,目前主流FPGA都采用了基于SRAM工艺的查找表结构。

LUT本质上就是一个RAM。它把数据事先写入RAM后, 每当输入一个信号就等于输入一个地址进行查表,找出地址对应的内容,然后输出。

7系列FPGA中的函数发生器实现为六输入查找表(LUT)。slice的4个函数发生器(A,B,C和D)中的每一个都有六个独立输入(A输入A1至A6)和两个独立输出(O5和O6)。

1)函数发生器可以实现以下函数功能:

•任意定义的六输入布尔函数

•两个任意定义的五输入布尔函数,只要这两个函数共享公共输入

•两个任意定义的布尔函数(3个和2个或更少输入)

2)六输入功能使用:

•A1-A6输入

•O6输出

3)两个五输入或更少的函数使用:

•A1–A5输入

•A6驱动高

•O5和O6输出

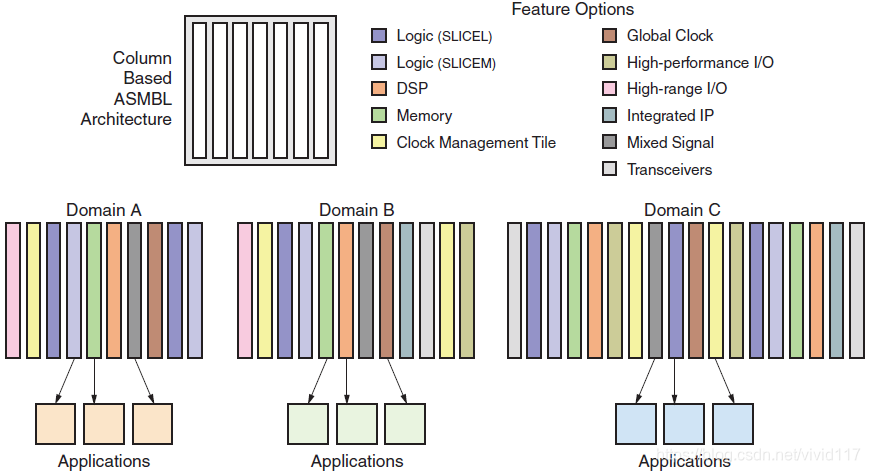

3.存储单元

每个slice有8个存储元素。

四个可以配置为边沿触发D型触发器或电平敏感锁存器。 D输入可以通过AFFMUX,BFFMUX,CFFMUX或DFFMUX的LUT输出直接驱动,也可以通过AX,BX,CX或DX输入绕过函数发生器的BYPASS slice输入直接驱动。 当配置为锁存器时,当CLK为低电平时,锁存器是透明的。对应如下右图

还有四个额外的存储单元,它们只能配置为边沿触发的D型触发器。 D输入可以由LUT的O5输出驱动,也可以由AX,BX,CX或DX输入的BYPASS slice输入驱动。 当原始的四个存储单元配置为闩锁时,这四个附加的存储单元将无法使用。对应如下左图

slice中的两种配置版本: 4个寄存器和4个寄存器/锁存器

4. Distributed RAM (Available in SLICEM Only)

关于Distributed RAM 在这篇博客有详细介绍

浅谈XILINX FPGA CLB单元 之 分布式RAM (Distributed RAM Available in SLICEM Only、RAM128X1D、Verilog原语描述)

5. 移位寄存器

关于移位寄存器 在这篇博客有详细介绍

浅谈XILINX FPGA CLB单元 之 移位寄存器(移位寄存器、SRLC32E、SRL16E)

6. 多路复用器(Multiplexers)

7系列FPGA中的函数发生器和相关的多路复用器可以实现以下功能:

•使用一个LUT的4:1多路复用器

•每片四个4:1 MUX

•使用两个LUT的8:1多路复用器

•每个slice两个8:1 MUX

•使用四个LUT的16:1多路复用器

•每片一个16:1 MUX

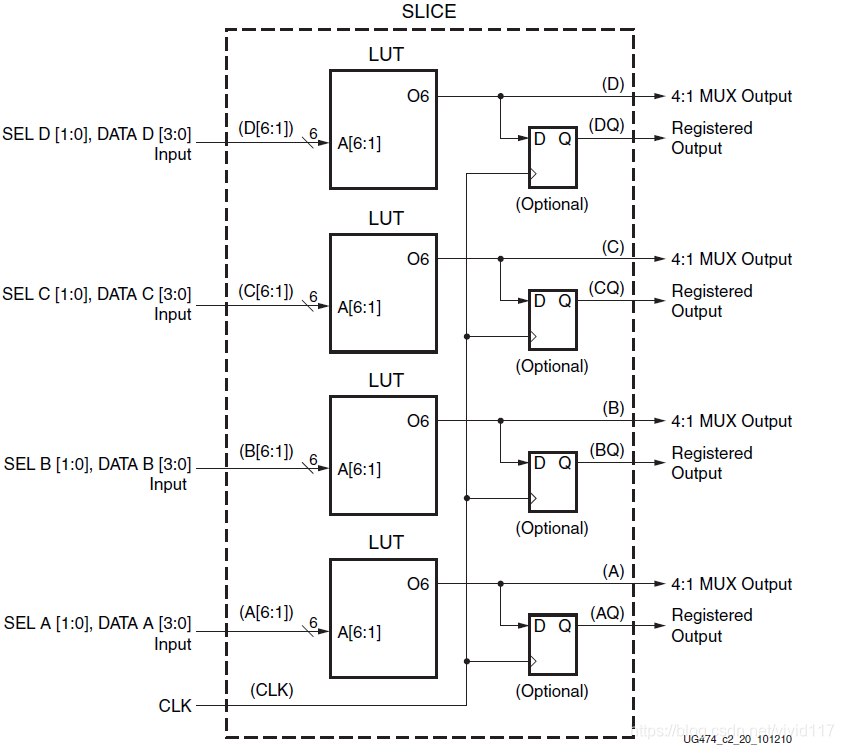

1)四个4:1 MUX

每个LUT可以配置为4:1 MUX。 4:1 MUX可以通过触发器在同一片中实现。 一个slice中最多可以实现四个4:1 MUX,如下所示:

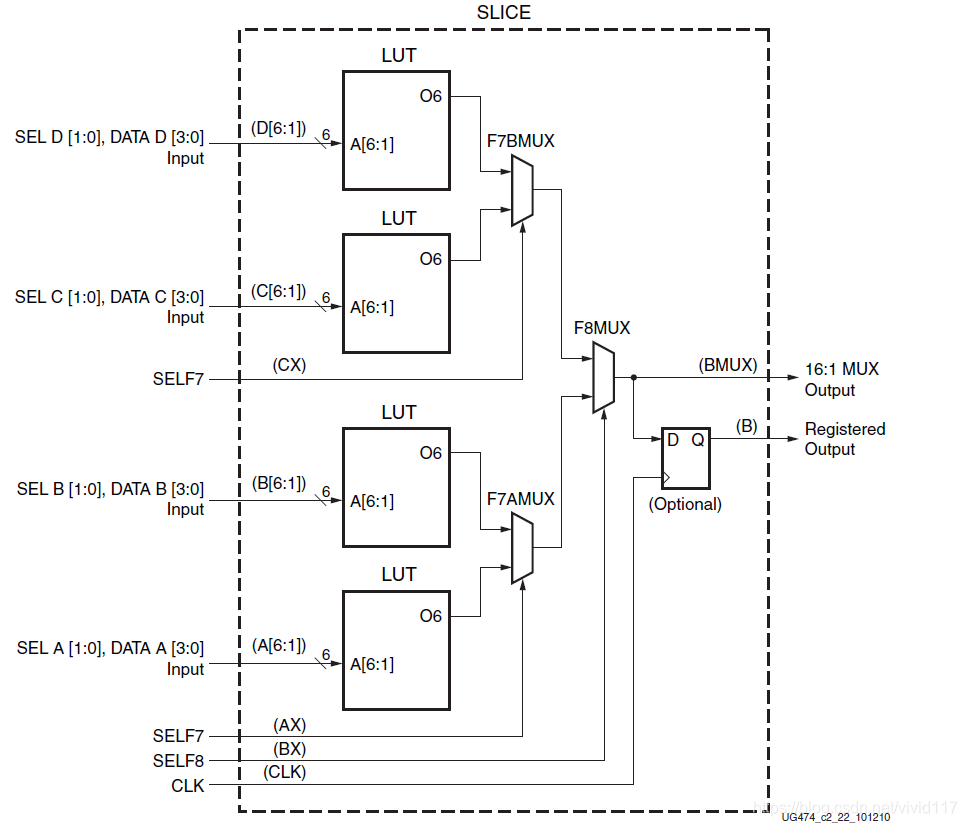

2)两个8:1 MUX

每个slice具有一个F7AMUX和一个F7BMUX。 这两个MUX组合了两个LUT的输出,以形成多达13个输入(或8:1 MUX)的组合功能。 一个slice中最多可以实现两个8:1 MUX,如图所示。

7. 进位逻辑(Carry Logic)

关于进位逻辑 在这篇博客有详细介绍

浅谈XILINX FPGA CLB单元 之 进位逻辑链(CARRY4原理分析,超前快速进位逻辑结构)