Achievement provides the only real pleasure in life.

有所成就是人生唯一的真正的樂趣。

LUT的一个重要功能是逻辑函数发生器。本质上,逻辑函数发生器存储的是真值表(Truth Table)的内容,而真值表则是通过布尔表达式获得。在vivado中,打开网表文件,选择相应的LUT,在property窗口中可以看到真值表。

从逻辑电路角度看,LUT是构成组合逻辑电路的重要单元,正因为如此,也成为了时序电路中,影响逻辑级数的重要因素。了解常规电路的逻辑级数对于设计初期时序评估是很有必要的。

以加法器为例:相应的RTL代码如下(因为verilog不支持二维输入输出,采用systemverilog语法)

module adder # (

parameter W = 16 // Width of the Adders

)

(

// Clock

input clk,

// First input

input logic signed [W-1:0] a,

// Second input

input logic signed [W-1:0] b,

// Output

output logic signed [W-1:0] out

);

logic signed [W-1:0] a_r;

logic signed [W-1:0] b_r;

always @ (posedge clk)

begin

a_r <= a;

b_r <= b;

out <= a_r + b_r;

end

endmodule逻辑级数如下所示:

可以看出逻辑级数3(LUT+carry+carry)。同理得到,对于32bit为6,48bit逻辑级数为8。【其实逻辑级数有点高了,对于跑300M+有点困难,后面的文章会有解决方案】。

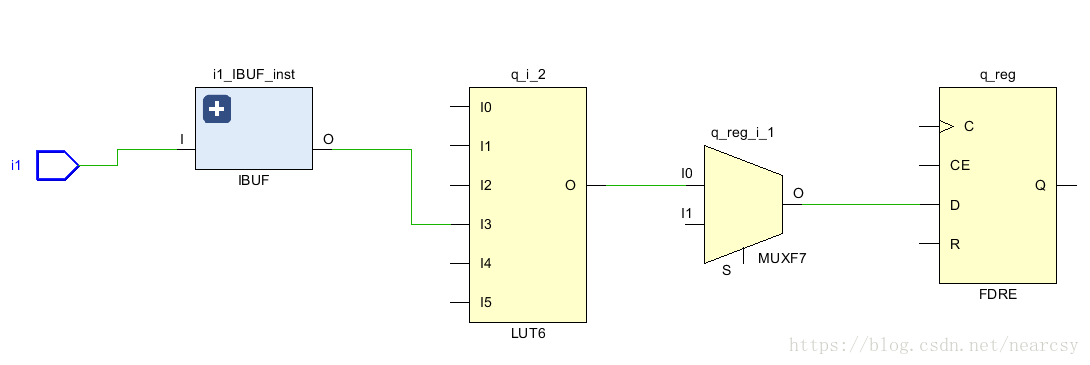

1个LUT6可以实现4选1的数据选择器(MUX),同时LUT6可以与SLICE中的F7MUX、F8MUX、F9MUX等一起构成更大MUX。对于8选1的MUX,其逻辑级数为2(1个LUT+1个F7MUX)。

对于16选1的MUX,其逻辑级数为3(1个LUT+1个F7MUX+1个F8MUX);

而32选1的MUX可在一个SLICE(针对UltraScale和UltraScale Plus芯片)中实现,消耗8个LUT6,4个F7MUX,2个F8MUX和1个F9MUX,因此,逻辑级数为4(1个LUT+1个F7MUX+1个F8MUX+1个F9MUX)。

module mux

(

// Clock

input logic clk,

// First input

input logic i0,i1,i2,i3,i4,i5,i6,i7,

// Second input

input logic [2:0] sel,

// Output

output logic signed q

);

always_ff@(posedge clk) begin

case(sel)

3'd0: q <= i0;

3'd1: q <= i1;

3'd2: q <= i2;

3'd3: q <= i3;

3'd4: q <= i4;

3'd5: q <= i5;

3'd6: q <= i6;

3'd7: q <= i7;

default: q <= 'd0;

endcase

end

endmodule从上图可以看出,8选1,2级逻辑级数(LUT + F7MUX)。同样,16选1是3级,32选1是4级。

还有一种常见的运算:比较运算关系。

module comparator

#(

parameter DW = 4

)

(

// Clock

input logic clk,

// First input

input logic signed [DW - 1 : 0]opa,

// Second input

input logic signed [DW - 1 : 0]opb,

// Output

output logic res

);

logic signed [DW - 1 : 0] opa_r = '0;

logic signed [DW - 1 : 0] opb_r = '0;

logic res_i;

assign res_i = (opa_r < opb_r);

always_ff@(posedge clk) begin

opa_r <= opa;

opb_r <= opb;

res <= res_i;

end

endmodulereport logic levels显示为3级逻辑级数。

总结表格如下:

| 8bit | 16bit | 32bit | |

| 有符号加法 | 3 | 6 | 8 |

| 数据选择 | 3 | 3 | 4 |

| 比较 | 3 | 3 | 4 |

通过以上总结可以看出,一些平常的操作,加法/数据选择/比较,逻辑级数都在5级左右。其实在高频(250M以上),其时序问题就会出现了。

【参考】:

1. 高亚军 《查找表用于组合逻辑》

2. UG474 7Series_CLB.pdf