STM32 NVIC 中断优先级管理

CM3内核支持256个中断,其中包含了16个内核中断和240个外部中断,并且有256级的可编程中断设置。

但STM32并没有使用CM3内核的全部东西,只用了一部分。

STM32有84个中断,包括16个内核中断和68个可屏蔽中断,具有16级可编程的中断优先级。

与NVIC相关的寄存器

typedef struct

{

__IOM uint32_t ISER[8U];

uint32_t RESERVED0[24U];

__IOM uint32_t ICER[8U];

uint32_t RSERVED1[24U];

__IOM uint32_t ISPR[8U];

uint32_t RESERVED2[24U];

__IOM uint32_t ICPR[8U];

uint32_t RESERVED3[24U];

__IOM uint32_t IABR[8U];

uint32_t RESERVED4[56U];

__IOM uint8_t IP[240U];

uint32_t RESERVED5[644U];

__OM uint32_t STIR;

} NVIC_Type;

ISER[8]:中断使能寄存器组。CM3内核支持256个中断,有8个32位寄存器来控制,每个位控制一个中断。

但STM32F103的可屏蔽中断只有60个,所以对我们来说,有用的就是两个ISER[0]和ISER[1],总共可以表示64个中断。

ISER[0]的 bit0~bit31 分别对应中断 0~31。ISER[1]的 bit0~27 对应中断 32~59;这样总共 60 个中断就分别对应上了。你要使能某个中断,必须设置相应的 ISER 位为 1,使该中断被使能(这里仅仅是使能,还要配合中断分组、屏蔽、IO 口映射等设置才算是一个完整的中断设置)。

ICER[8]:中断除能寄存器组。

ISPR[8]:中断挂起控制寄存器组,通过置1,将正在进行的中断挂起,而执行同级或更高级别的中断。写0是无效的。

ICPR[8]:全称是:Interrupt Clear-Pending Registers,是一个中断解挂控制寄存器组。其作用与 ISPR 相反,对应位也和 ISER 是一样的。通过设置 1,可以将挂起的中断接挂。

IABR[8]:全称是:Interrupt Active Bit Registers,是一个中断激活标志位寄存器组。对应位所代表的中断和 ISER 一样,如果为 1,则表示该位所对应的中断正在被执行。这是一个只读寄存器,通过它可以知道当前在执行的中断是哪一个。在中断执行完了由硬件自动清零。

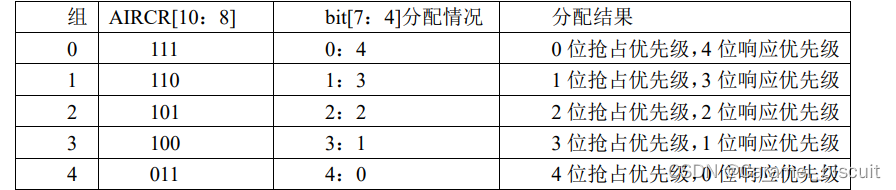

IP[240]:全称是:Interrupt Priority Registers,是一个中断优先级控制的寄存器组。这个寄存器组相当重要!STM32 的中断分组与这个寄存器组密切相关。IP 寄存器组由 240 个 8bit 的寄存器组成,每个可屏蔽中断占用 8bit,这样总共可以表示 240 个可屏蔽中断。而 STM32 只用到了其中的前 60 个。IP[59]~IP[0]分别对应中断 59~0。而每个可屏蔽中断占用的 8bit 并没有全部使用,而是 只用了高 4 位。这 4 位,又分为抢占优先级和子优先级。抢占优先级在前,子优先级在后。而这两个优先级各占几个位又要根据 SCB->AIRCR 中的中断分组设置来决定。

中断分组

STM32将中断分为5个组,组0~4.

例如组设置为3时,此时所有的60个中断,每个中断的中断优先级寄存器的高四位中的最高3位是抢占优先级,低1位是响应优先级。

每个中断,可以设置抢占优先级为0~7,响应优先级为1或0。

抢占优先级的级别高于响应优先级。而数值越小所代表的优先级就越高。

如果两个中断的抢占优先级和响应优先级都是一样的话,则哪个中断先发生就先执行。高优先级的抢占优先级可以打断正在进行的低抢占优先级中断的。而抢占优先级相同的中断,高优先级的响应优先级不可以打断低响应优先级的中断。