(1)在不影响逻辑功能的情况下,CMOS与非门的多余输入端可_____。

A.接高电平

B.接低电平

C.悬空

D.通过电阻接地

解析:

-

CMOS与非门:只要有一个输入是低电平,与运算之后均为低电平,取非输出高电平,影响结果,若接地或者悬空输出始终为1。

-

CMOS与门、与非门:多余输入端通过限流电阻(500Ω)接电源,即接高电平;

-

CMOS或门、或非门:多余输入端通过限流电阻接地,即接低电平;

-

TTL与门、与非门:

a:将多余输入端接高电平,即通过限流电阻与电源连接;

b:通过大电阻(大于1K)到地,相当于输入端接高电平;

c:把多余输入端悬空(相当于有大电阻),相当于输入端接高电平; -

TTL或门、或非门:通过接小于1KΩ的电阻到地。

答案:A

(2)欲产生序列信号11010111,则至少需要_____级触发器。

A.2

B.3

C.4

D.5

解析:

- 序列长度N=8,2^3=8,至少3级触发器;若用移位寄存器则至少需要5级触发器

答案:D

(3)一个8位二进制减法计数器,初始状态为00000000,问经过268个输入脉冲后,此计数器的状态为_____。

A.11001111

B.11110100

C.11110010

D.11110011

解析:

- 2^8=256,计数256次回到0000_0000,268-256=12,计数1次后0000_0000 - 0000_0001 = 1111_1111,计数11次后1111_1111 – 0000_1011 = 1111_0100

答案:B

(4)移位寄存器由8级触发器组成,用它构成的扭环形计数器具有_____种有效状态;用它构成的环形计数器具有_____种有效状态,构成线性反馈移位寄存器具有_____种有效状态。

A.16,8,511

B.4,8,15

C.16,8,255

D.8,16,127

解析:

- 扭环形计数器:每次变化时仅有一个触发器发生翻转,译码不存在竞争冒险,使用2n个状态;

- 环形计数器:所有触发器只有一个是1状态,计数N次需要N个触发器;

- 线性反馈移位寄存器:2^n – 1。

答案:C

(5)若要将一异或非门当做反相器(非门)使用,则输入端A、B端的连接方式是______。

A.A或B中有一个接“ 1”

B.A或B中有一个接“ 0”

C.A和B并联使用

D.不能实现

解析:

- 异或:与0异或是本身。取非后是输入的取反,相当于反相器。

答案:B

(6)实现同一功能的Mealy型同步时序电路比Moore型同步时序电路所需要的_____。

A.状态数目更多

B.状态数目更少

C.触发器更多

D.触发器更少

解析:

- Mealy:输出与当前状态和输入有关;

- Moore:输出与当前状态有关;

- Mealy比Moore(打一拍)超前一个时钟周期;Moore状态数目多一个。

答案:B

(7)假定某4比特位宽的变量a的值为4’b1011,计算下列运算表达式的结果:&a,{3{a}},~a,{a[2:0],a[3]},(a<4’d3) || (a>=a),!a

解析:

- &:按位与;

- &a:a中的各位相与,结果为1bit,a中有0,所有位与后输出1’b0;

- &&:逻辑与;

- ~:按位取反;

- !:逻辑取反;

(8)下面两段代码中信号in,q1,q2和q3的初值分别为0,1,2和3,那么经过1个时钟周期后,左侧程序中q3的值变成(),右侧程序中q3的值变成()。

解析:

- 阻塞赋值=:阻塞指等到当前赋值语句结束后才进行下一个语句的赋值,即in赋值q1,q1赋值q2,q2赋值q3;

- 非阻塞赋值<=:不同赋值语句之间不影响,在下一个时钟沿时将q2在上一个时钟周期的值2赋值给q3。

答案:0 , 2

(9)一个大型的组合电路总延时为100ns,采用流水线将它分为两个较小的组合电路,理论上电路最高工作频率可达()。

解析:

- 拆分每个时延是50ns,即20MHz。

答案:20MHz

(10)块语句有两种,一种是begin-end语句,通常用来标志()执行的语句;一种是fork-join语句,通常用来标志()执行的语句。

解析:

- begin-end :语句按顺序一条条执行;fork-join:并行块,块内语句同时执行。

答案:顺序 ,并行

(11)在高速系统设计中,下列哪种优化方案的目的不是为了提高系统的工作频率()。

A.流水线

B.树型结构

C.迟置信号后移

D.资源共享

解析:

- 面积优化,提高资源利用率以降低功耗:串行化,资源共享,逻辑优化;

- 速度优化,提高运行速度:流水线设计,寄存器配平,关键路径优化,迟置信号后移。

答案:D

(12)状态机的编码风格包括一段式、两段式和三段式,下列描述正确的是()

A、一段式寄存器输出,易产生毛刺,不利于时序约束;

B、二段式组合逻辑输出,不产生毛刺,有利于时序约束;

C、三段式寄存器输出,不产生毛刺,有利于时序约束;

D、所有描述风格都是寄存器输出,易产生毛刺,有利于时序约束。

解析:

-

二段式时序逻辑和组合逻辑分开,当前状态用组合逻辑输出,可能出现竞争冒险产生毛刺,而且不利于约束。

-

一段式和三段式都是寄存器输出。

-

三段式与二段式相比:在不插入额外的时钟节拍下实现了寄存器输出。

答案:C

(13)关于过程块以及过程赋值描述中,下列正确的是()

A、在过程赋值语句中表达式左边的信号一定是寄存器类型;

B、过程块中的语句一定是可综合的;

C、在过程块中,使用过程赋值语句给wire赋值不会产生错误;

D、过程块中时序控制的种类有简单延迟、边沿敏感和电平敏感。

解析:

- 过程赋值:有initial块和always块两种过程赋值块,两种语句都是并行执行,若与begin-end结合则是顺序执行。被赋值数据类型必须是寄存器类型变量(reg);

- 连续赋值:用于组合逻辑,任何一个输入的改变都立即更新输出。被赋值数据类型必须是wire类型变量,如assign out=a;

答案: A

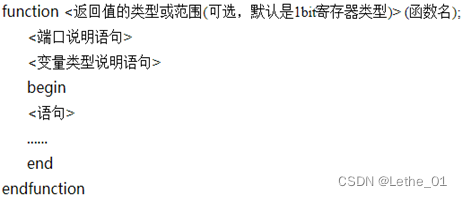

(14)关于函数的描述下列说法不正确的是()

A、函数定义中不能包含任何时序控制语句;

B、函数至少有一个输入,包含任何输出或双向端口;

C、函数只返回一个数据,其缺省为reg类型;

D、函数不能调用任务,但任务可以调用函数。

解析:

- A:函数定义不能包含任何控制语句(#、@、wait),任务中可以使用延迟、时间和时序控制结构;

- B:函数至少有一个输入,不能包含任何输出和双向端口,任务可以有多个输入、双向和输出变量;

- C:函数有一个返回值,缺省时默认返回1’bit寄存器reg数据,任务task没有返回值;

- D:函数不能启动任务,任务可以启动其他任务或者函数。

答案: B