优秀的验证工程师,需要掌握的技能有很多,兼备硬件和软件,可以说是更加触类旁通。所以还是需要循序渐进,从最基础的内容开始逐步掌握。

文内所有的学习资料,面试题目(文末可全领)

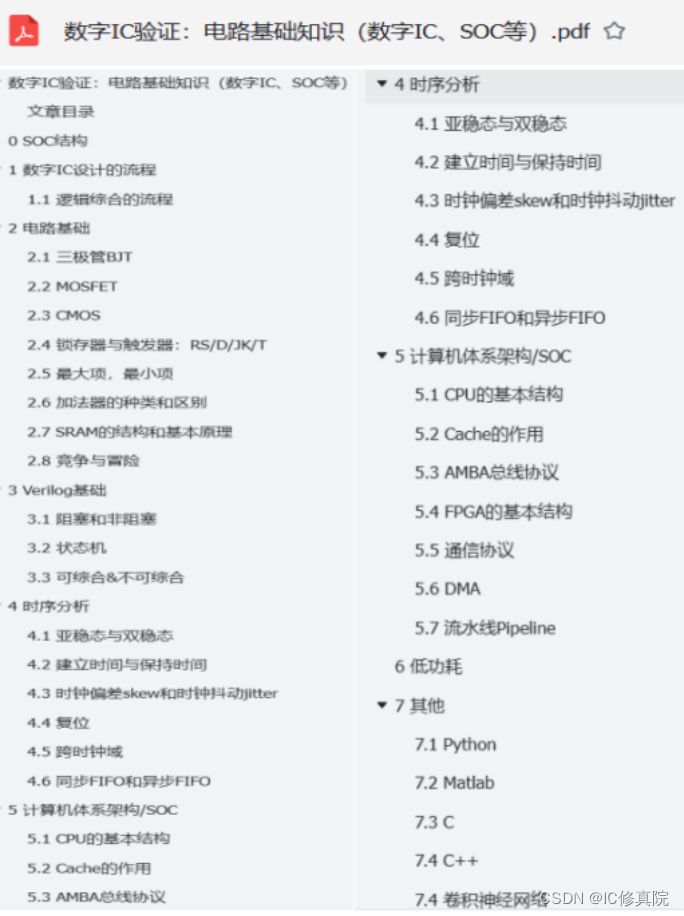

1.数电和verilog

数字电路的基础内容基本包括:数制和码制;逻辑代数基础;门电路;组合逻辑电路;半导体存储电路;时序逻辑电路;脉冲波形的产生和整形电路;数-模和模-数转换等。

在学完了数电基础之后就可以开始验证中Verilog的学习了,verilog语言和c语言还是有本质的区别的,因为verilog进行的是硬件设计,写出来的是实实在在电路,这时候之前学习的数电基础就派上用场了。

2、 SV和UVM

SV和UVM就这两本书,可以先找资源看一下,SV看第一遍看不懂没关系,再看看书就懂得差不多了,然后学习UVM,UVM是基于SV的验证方法学,把 UVM 的结构理清楚。

SV的基础学习大致包括以下内容:DataType;动态数组;队列;联合数组;数组的操作;语法等。

在SV之后,同学们可以进行UVM的学习。UVM是一个以SV为主体的验证平台开发框架,验证工程师利用其可重用组件可以构建具有标准化层次结构和接口的功能验证环境。

UVM是一个库,在这个库中,几乎所有的东西都是使用类(class)来实现的。同时,UVM也是验证方法学,指导你如何搭建验证平台,有哪些构成,如何连接与通信。

学习UVM需要了解UVM的构架,各种omponent, phase管理机制等。最好配合实例代码一边学习一边自己敲代码做练习。

3、脚本语言

验证常用的脚本语言是Python、Perl、Tcl、Shell,有的还需要C和C++。现在面试中常常会有要求同学们当面写代码实现一些比较简单的题。所以建议同学们除了shell、C和C++之外,python和perl至少要懂一个。

4、验证项目

做过项目和没做过项目,在面试官眼里有很大的差别。这里就建议大家尽可能多参与项目,从企业中获取项目,真正跟着公司做过事情的人面试时的表现是不同的。社招的话有无项目经历、项目的方向、项目完成度都是非常重要的。

尤其是社招,项目经验是岗位匹配度的一个重要参考标准。

项目需要重点关注:

DUT的功能和结构

根据DUT的功能及结构我们搭建的验证平台,为什么要这样搭建

验证平台的各个组件之间的通信,如何跟DUT相关联

分解测试点,都验了哪些功能,各个功能你是怎么验证的(这个可能有时候会问的比较细致)

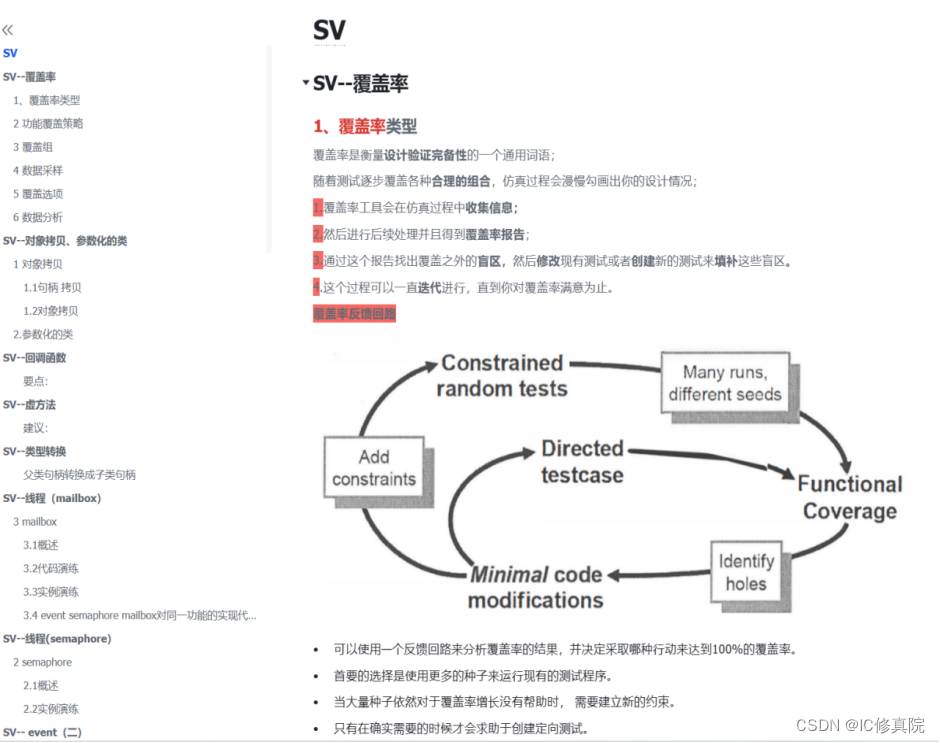

收集覆盖率,代码覆盖率,功能覆盖率为什么才90%?你是怎么收集的?达不到 100%怎么办?

本项目基于UVM验证平台。UART作为通用串行数据总线,用于异步双向通信,实现数据的串并传唤。此UART模块支持全双工数据传输和接收,数据位5-8bit,停止位1~2bit,奇偶校验,16个字节FIFO深度。

5、刷笔试题和面经

各家公司笔试题和面经一定要多刷刷。比如下面这些题目:

以上就是数字验证需要学习的东西了,大家还有哪里不懂的可以在评论区留言,秋招将至,大家一定要抓紧刷大厂面试题目~有需要上述资料的可以按需领!

这里放个入口:数字IC 验证学习资料