FPGA底层资源主要是Slices、IOBs、Memory、Multipliers、Global clock buffers等等,下面对各类资源进行详细的解读。

一.Slices

7系列FPGA的slice包含4个部分:

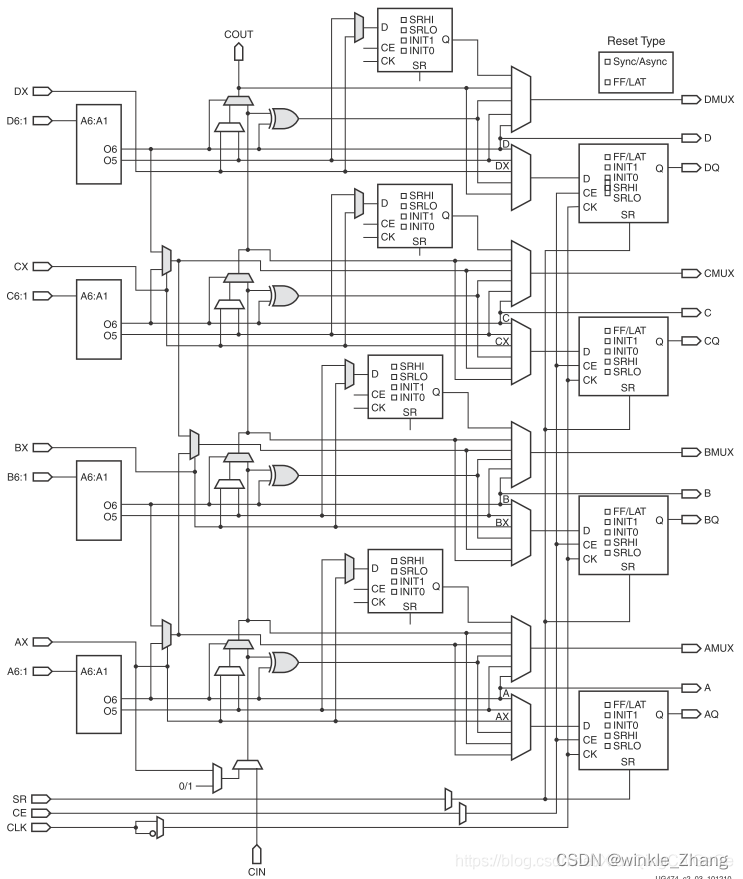

(1)

逻辑功能产生器,也就是咱们常说的查找表LUT,1个slice里包含4个6输入的查找表。

(2)

存储单元,也就是常说的触发器,1个slice里包含8个触发器。每4个触发器为一组,可配置成D触发器或锁存器。

(3)

多路复用器,也就是1位宽的数据选择器mux,数量非常多,足够使用。

(4)

进位逻辑(carry chain),另外这不是或门,而是异或门。这是FPGA中自带的进位链(Carry Chain)逻辑。一般当你实现诸如计数器这种可能有进位逻辑的设计可能会调用到这部分资源

因此,许许多多的slice相结合,再加上全局时钟就能实现复杂的数字功能!

sliceL的结构图:

二.IOBs

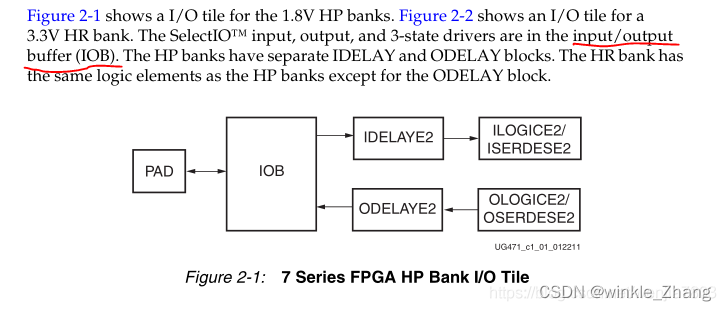

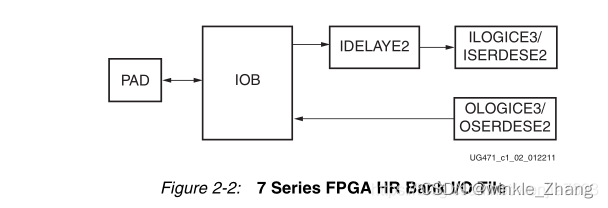

可编程IO的作用就是完成信号的采集和输出,引脚可以配置支持不同电气特性,上拉下拉或三态,差分或单端。IOB与附近的idelay、odelay、ilogic、ologic和可编程IO等资源,共同组成FPGA的IO_Bank。

三.Memory

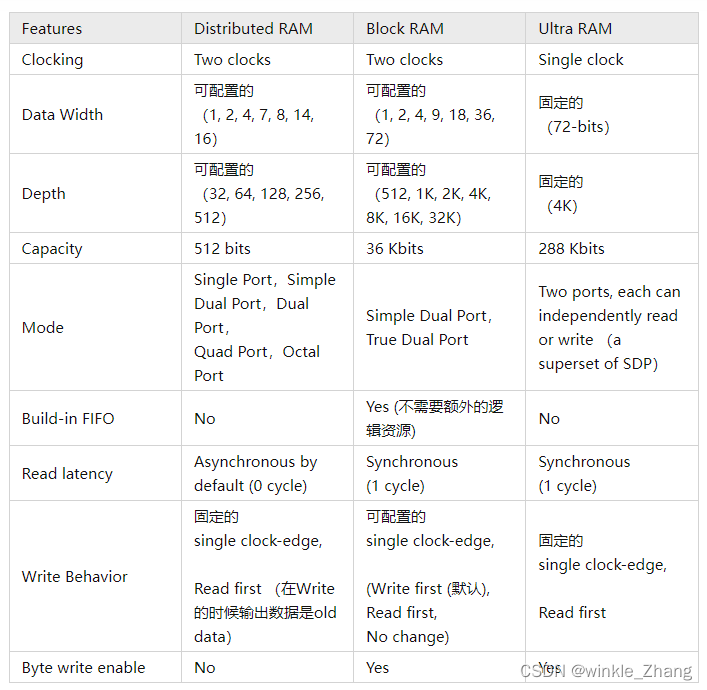

FPGA 的 on-chip memory 一般可以分成两种,即 Distributed RAM 和 Block RAM。DRAM 是由 LUT 实现的,Block RAM 则是专用的 mem 资源,容量比 DRAM 大一些。

在 UltraScale+ 系列,Xilinx 引入了一种新的专用 mem 资源,叫做 Ultra RAM,单个 URAM 的容量是 Block RAM 的6倍,能支持更大的数据处理需求。使用下面的表格来对比三种 Mem 资源。更细节的内容可以去阅读 Xilinx 的 Guide

存储同样的数据,使用 BRAM 可能会比 DRAM 消耗更少的资源,但是 BRAM 可能对 timing 的影响更大,如果这个时候 timing 是更重要的因素,那么只好牺牲掉一些资源使用 DRAM。

参考:《UltraScale Architecture Memory Resources》

《UltraScale Architecture Configurable Logic Block》

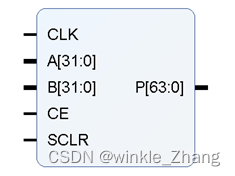

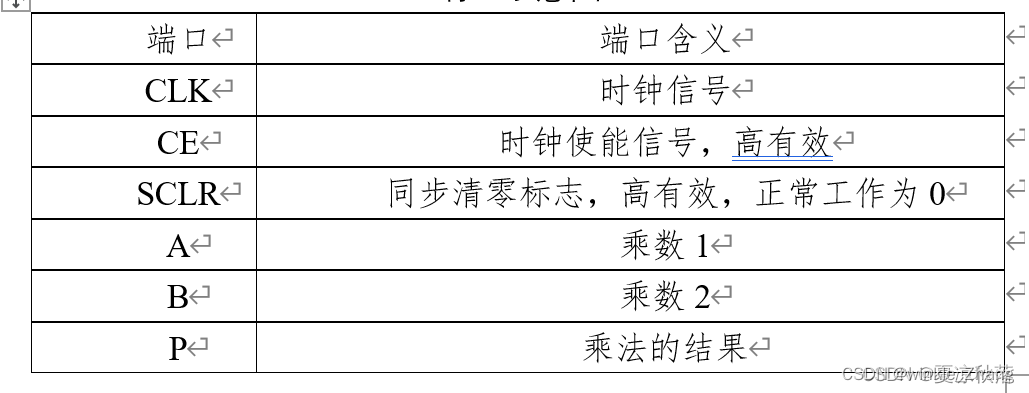

四.Multipliers

乘法器顾名思义,用来做乘法运算

五.

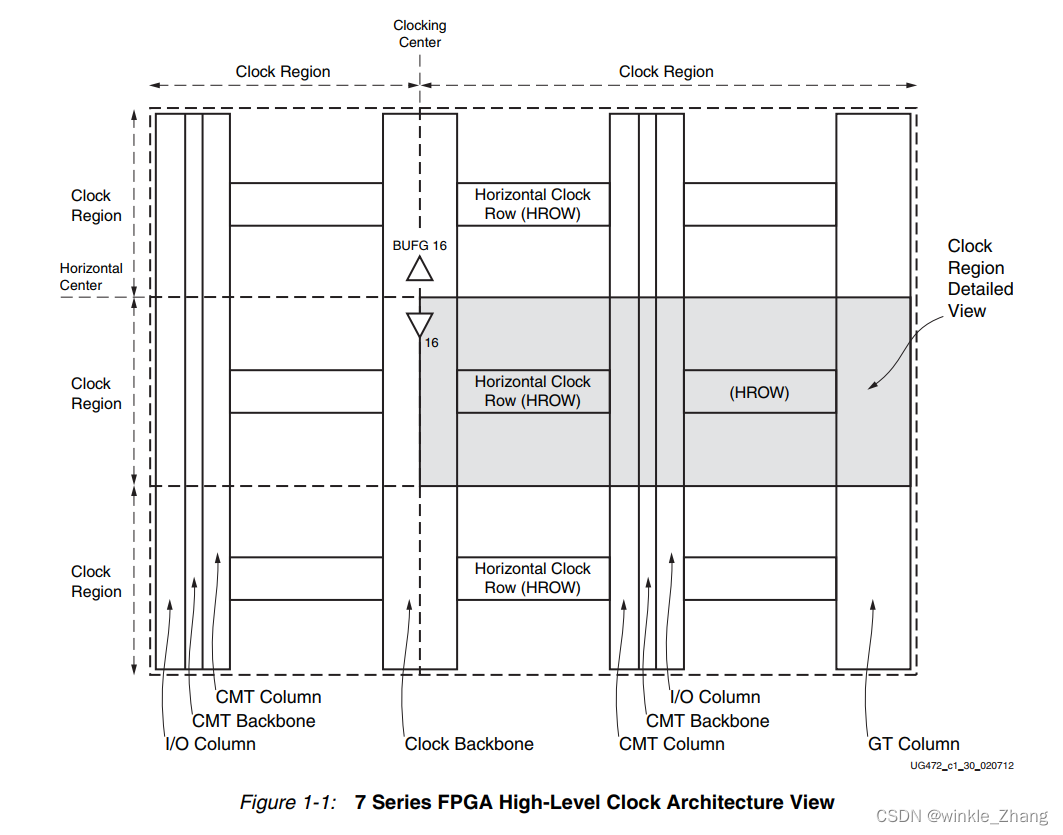

FPGA的时钟资源介绍主要分为三部分。第一部分是区域结构,第二部分是元件功能,第三部分是实现方式。

首先FPGA的时钟资源负责驱动所有的时序逻辑,生产商尽力使得时钟资源充分,可靠,为了达成这一目的,xilinx采取了结构化的时钟资源布局方式。

首先将整个板子分为左右两部分,宽度完全一致,中间是大动脉。也就是下图中的Clocking Center位置的Clocking Backbone,所有的BUFG(Global Clock buffers)也是包含在这里面。

顾名思义,BUFG是全局的Clock buffer。

BUFG能

1.作为时钟使能控制跨越了数个时钟域的时钟

2.作为无毛刺的多路复用器进行时钟二选一亦或是切换掉失效的时钟

3.被CMT驱动来消除时钟分发延迟,调整相对另一个时钟的延迟

一条动脉显然无法给整个人体供血,有限个数(7系列有32条布线资源)的BUFG也无法直接驱动所有的逻辑资源。虽然BUFG的驱动范围最广,但是所有资源都使用BUFG也不能获得最好的效果。

所以我们还需要横向的血管,也就是HROW(Horizontal Clock Row),它们等距水平分布,非常像模拟城市里建造道路时的棋盘式布局。但是HROW不同于Clock Backbone,它们主要负责相邻上下两个部分的时序逻辑资源驱动,具体实现则通过BUFH,BUFH相当于作用范围阉割版的BUFG。每个时钟域内有12条BUFH的布线资源,也就是说,一个时钟域最多能用12条BUFH布线资源引入12个BUFG的时钟。

在这里还要强调一点,所有的全局时钟信号线布线时都必须经过Clock Backbone,而当全局时钟信号线从Clock Backbone出来之后,要进入具体的时钟区域时,则必须通过HROW。那么我们可以这么总结,所有的全局时钟线布线时都必须经过Clock Backbone和HROW,BUFG和BUFH共享HROW中的布线资源。一条进入某个时钟域内的路径可以是一条BUFG的信号线从Clock Backbone中引出,再接到BUFH上,总共使用了一条BUFG的布线资源(1/32)和(1/12),当然,信号线是可以复用的。

时钟区域是什么?时钟区域是板子的划分,它的上下界限在两条HROW的中间处,也就是说,每个时钟区域的中间都有一条HROW横穿而过。而它的左右界限则是两条CMT Backbone的中间处,同理,每个时钟区域的中间都有一条CMT Backbone竖穿过去。根据板子的大小不同,时钟域数量从1到24不等。一个时钟域包括了所有的同步组件(CLB, I/O, serial transceivers, DSP, block RAM, CMT)。每个时钟域包括了50个CLB和1个I/O bank(50 I/Os)。

在横向的血管之外,我们还需要小血管和毛细血管,对应BUFMR和BUFR。BUFMR可以驱动本时钟域内所有的时序资源以及上下相邻的两个时钟域。当它驱动相邻时钟域时,布线需要经过CMT Backbone。而BUFR只能驱动本时钟域内的时序资源。

而BUFIO只能驱动本时钟域/本I/O域内的I/O部件。

参考:https://blog.csdn.net/weixin_43778388/article/details/122521139

https://zhuanlan.zhihu.com/p/336370365?utm_medium=social&utm_oi=47239162494976

http://t.zoukankan.com/aliothx-p-13398060.html

https://blog.csdn.net/dongdongnihao_/article/details/111354406

https://blog.csdn.net/wenjia7803/article/details/115339122