前言

FPGA(Flield Programmable Gate Array)作为一种可编程的芯片,其结构和开发方式都与传统的MCU或DSP不同。MCU或DSP的设计,是主要进行软件程序设计,用户主要使用C语言完成各种控制和算法的实现,各种功能是在CPU的控制下按照顺序依次来实现的。而FPGA设计,实质上是电路设计,是在一个可以现场编程的通用逻辑器件中去搭建各种具有一定功能的逻辑电路,各个逻辑电路之间是各自独立的,能够并行执行。同时各个功能电路之间又通过一定的控制和握手信号相互协调。所以,在开发和使用FPGA之前,需要对其有一定充分细致的认识,包括对其硬件资源结构,硬件电路设计和开发环境等。

硬件资源结构概述

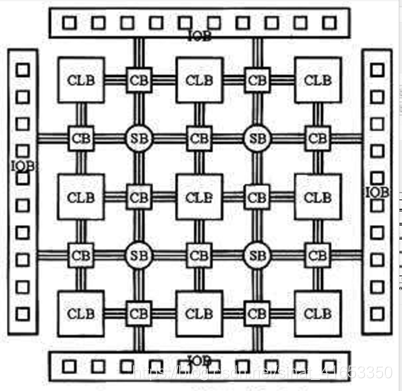

典型的FPGA通常包含三类基本资源:可编程逻辑功能块,可编程I/O块和布线资源。

1. 可编程逻辑功能块(CLB模块)

是实现用户功能的基本单元,多个逻辑功能块通常规则的排成一个阵列结构,分布于整个芯片。一个CLB模块通常包含若干个基本的查找表LUT,寄存器和多路选择器资源,因此FPGA的逻辑表达是基于LUT的。

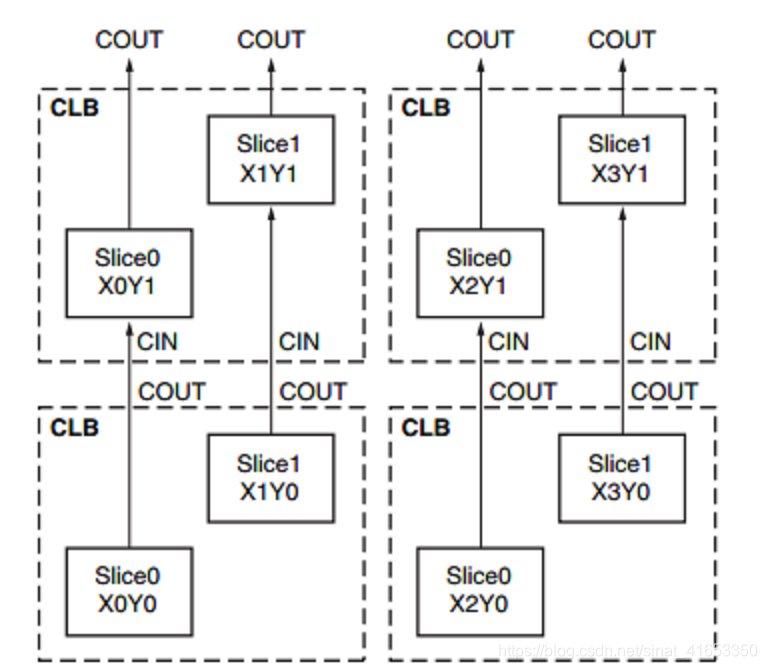

CLB在FPGA中资源最为丰富,由两个SLICE构成,其中SLICE又分为SLICEL(L:Logic)和SLICEM(M:Memory),因此CLB可分为CLBLL和CLBLM两类,其主要区别是SLICEM中含有能够把LUT资源重新整合为RAM或ROM的逻辑,这就是所谓的Distributed Ram,而SLICEL不具备该项功能,所以SLICEM比SLICEL多了存储器和移位功能。

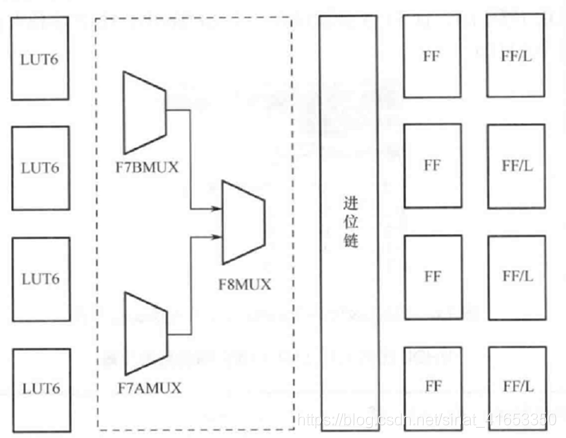

SLICEL和SLICEM内部包含4个6输入查找表(LUT6),3个数据选择器(MUX),1个进位链(carry chain)和8个触发器(Flip-Flop)。

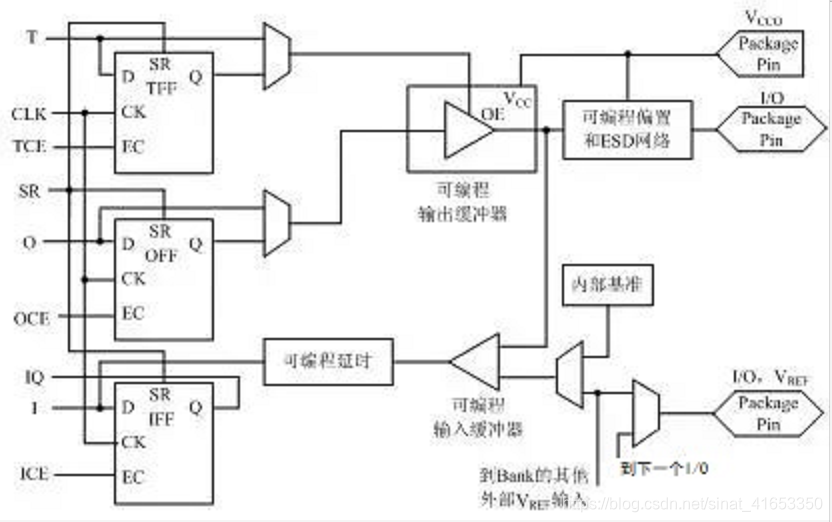

2. 可编程I/O块(IOB)

完成芯片内部逻辑与外部管脚之间的接口,围绕在逻辑单元阵列的四周,完成不同电气特性下对输入/输出信号的驱动和匹配要求,I/O按组分类,每组都能够独立地支持不同的I/O标准,每个组的接口标准由其接口电压VCCO决定的,一个组只能有一种VCCO,只有相同电气标准的端口才能连接到一起,VCCO电压相同是接口标准的基本条件。

3. 布线资源

包括各种长度的连线线段和一些可编程连接开关,它们将各个可编程逻辑块或I/O块连接起来,构成特定功能的电路,可以通过编程决定每个单元的功能以及它们的互联关系,从而实现所需的逻辑功能。

实际使用中FPGA器件都会在典型的架构上加入一些其他的常用资源,如时钟管理单元(PLL,DLL),嵌入式存储器单元和硬件乘法器单元,部分器件还加入了高速收发器甚至是嵌入式硬核处理器。