前言:

因为项目,需要对DDR做一个软核控制器,师傅帮我物色了Litex项目的外设:Litedram。

网上现有的教程,基本都是验整个Litex,因为缺少单独验证Litedram的资料,踩了不少坑,这里介绍一下单独验证Litedram的流程,本小节,只讲安装、配置及导出litedram_core.v文件,后续章节,再补充GTKWave仿真波形等。

一、关于Litex:

LiteX框架提供了一个方便高效的基础设施来创建FPGA核心/SOC,探索各种数字设计架构,并创建完全基于FPGA的系统。

LiteX是用Migen编写的,Migen是一个基于Python的工具,可以进一步自动化VLSI设计过程。Migen的核心是FHDL,即碎片化的硬件描述语言。FHDL本质上是一种基于Python的数据结构,由描述信号,寄存器,FSM,组合逻辑,顺序逻辑等的基本结构组成。

官网:Litex

部分中文论坛描述:用FPGA创建SoC如此容易

首先介绍 CPU 和 SoC 的区别:通常 CPU 大家比较熟悉,CPU 实现一些指令集 (ISA) 从而可以编程用作通用计算,常见的指令集有 x86, AMD64, ARM, MIPS, RISC-V。然而 CPU 不能独立运行,需要从外部存储加载代码、数据到内存 (RAM) 里执行。为了和外部世界交互,例如读写硬盘、传感器,连接显示屏,还会需要总线和一些外围设备 (Peripheral) ,这样各种总线、外围组件等一起组成了 SoC (System on Chip)。

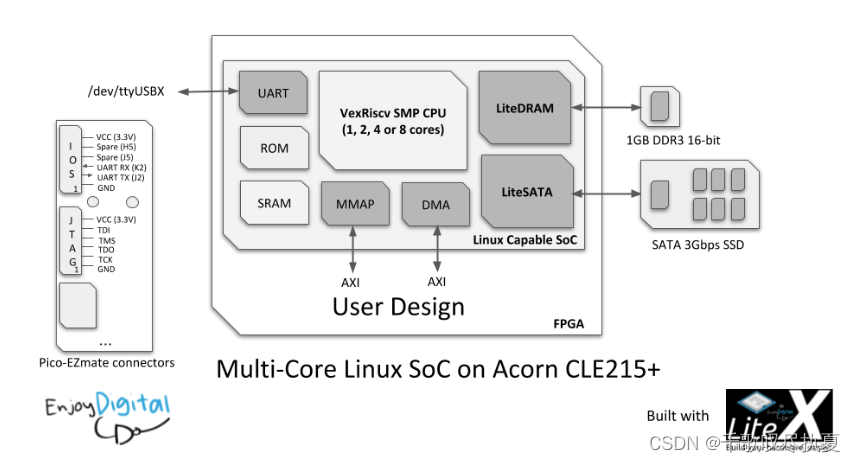

例如下面这个可以运行 Linux 的 SoC 包含了 8 核 RISC-V CPU, ROM, SRAM, LiteDRAM, LiteSATA 等组件,所以通常来讲 CPU 是 SoC 的一部分。

当然,现在很多时候模糊了 CPU 和 SoC 的界限,例如 Intel CPU 内部集成了 GPU、硬件加密等各种外设模块,其实算是 SoC,可能解释起来比较麻烦,商业宣传上依旧称之为 Intel CPU。

上面这段描述来自:LiteX 定制 SoC 上使用 C 和 Rust 嵌入式 (RISC-V),对RISCV有兴趣、想移植的到FPGA的,可以看看这篇文章。

二、前期工作

在验证之前,少不了得安装环境,对于大佬来说,这一步可能无关紧要,但是对于小白来说,这一关,可能就得卡两三天了。

首先安装虚拟机、Ubuntu、配置git等(这一步,可以看看正点原子的领航者的Linux开发教程)

值得一提的是,litex除了在Linux下开发,也能在Windows下开发,安装好Cygwin,并配置好环境就行。

安装Litex及其环境,我检索了几个优质的参考资料:

视频:

LiteX开发环境搭建及简单测试

VexRiscv开发环境搭建

安装文档:

要有速度较快的VPN(梯子),然后在下载litex并进行安装这一步的时候,执行litex_setup.py的时候,小概率会遇到解析不了,我就遇到了,多半是git的原因,到时候如果自己解决不了,可以私信我帮忙看看。

//--------------------------------------------------

//配置VPN

//--------------------------------------------------

//--------------------------------------------------

//安装vm-tools,解决无法复制粘贴的问题

//--------------------------------------------------

sudo apt-get install open-vm-tools-desktop

sudo reboot

//--------------------------------------------------

//安装必要的依赖和库文件

//--------------------------------------------------

sudo apt-get install python3-pip

sudo apt-get install libevent-dev

sudo apt-get install libjson-c-dev

pip3 install meson ninja

sudo reboot //重启系统

//--------------------------------------------------

//下载linux-on-litex-vexriscv

//--------------------------------------------------

sudo apt install build-essential device-tree-compiler wget git python3-setuptools

git clone https://github.com/litex-hub/linux-on-litex-vexriscv

//--------------------------------------------------

//下载litex并进行安装

//--------------------------------------------------

cd linux-on-litex-vexriscv

wget https://raw.githubusercontent.com/enjoy-digital/litex/master/litex_setup.py

chmod +x litex_setup.py

./litex_setup.py --init --install

./litex_setup.py --update

//--------------------------------------------------

//安装依赖和RiscV GCC.方法一,方法二,如果无法正常安装.可使用方法三.

//--------------------------------------------------

./litex_setup.py --gcc=riscv

//--------------------------------------------------

//安装RiscV GCC.方法二.

cd ../

wget https://static.dev.sifive.com/dev-tools/riscv64-unknown-elf-gcc-10.1.0-2020.08.2-x86_64-linux-ubuntu14.tar.gz

tar -xvf riscv64-unknown-elf-gcc-10.1.0-2020.08.2-x86_64-linux-ubuntu14.tar.gz

export PATH=$PATH:$PWD/riscv64-unknown-elf-gcc-10.1.0-2020.08.2-x86_64-linux-ubuntu14/bin/

//--------------------------------------------------

//方法三

从GitHub上下载对应Ubuntu版本的文件 https://github.com/sifive/freedom-tools/releases

//拷贝到/opt/,并解压

sudo cp riscv64-unknown-elf-toolchain-10.2.0-2020.12.8-x86_64-linux-ubuntu14.tar.gz /opt/

cd /opt

sudo tar -xzvf riscv64-unknown-elf-toolchain-10.2.0-2020.12.8-x86_64-linux-ubuntu14.tar.gz

//重命名文件夹

sudo mv riscv64-unknown-elf-toolchain-10.2.0-2020.12.8-x86_64-linux-ubuntu14 Riscv-toolchain

sudo chmod 777 -R Riscv-toolchain/

//添加到环境变量

echo 'export PATH=/opt/Riscv-toolchain/bin:$PATH' >> ~/.bashrc

//--------------------------------------------------

//安装JDK

//--------------------------------------------------

sudo add-apt-repository -y ppa:openjdk-r/ppa

sudo apt-get update

sudo apt-get install openjdk-8-jdk -y

sudo update-alternatives --config java

sudo update-alternatives --config javac

//--------------------------------------------------

//安装SBT环境(此方法不一定可用,公共key服务器无法正常连接上)

//可能需要手动安装SBT(由安装包安装)

//--------------------------------------------------

echo "deb https://repo.scala-sbt.org/scalasbt/debian all main" | sudo tee /etc/apt/sources.list.d/sbt.list

echo "deb https://repo.scala-sbt.org/scalasbt/debian /" | sudo tee /etc/apt/sources.list.d/sbt_old.list

sudo apt-get install curl

curl -sL "https://keyserver.ubuntu.com/pks/lookup?op=get&search=0x2EE0EA64E40A89B84B2DF73499E82A75642AC823" | sudo apt-key add

sudo apt-get update

sudo apt-get install sbt

//--------------------------------------------------

//方法二

//从GitHub上下载sbt的发布包,并解压到指定位置。

wget https://github.com/sbt/sbt/releases/download/v1.8.2/sbt-1.8.2.tgz

sudo tar -zxvf sbt-1.8.2.tgz -C /usr/local/

sudo chmod 777 -R /usr/local/sbt/

//创建可执行文件,并写入内容

sudo gedit sbt

//内容

#!/bin/bash

SBT_OPTS="-Xms512M -Xmx1536M -Xss1M -XX:+CMSClassUnloadingEnabled -XX:MaxPermSize=256M"

java $SBT_OPTS -jar /usr/local/sbt/bin/sbt-launch.jar "$@" # 注意对应路径

//

//修改权限

sudo chmod 777 sbt

//换镜像源

cd ~

mkdir .sbt

cd .sbt

gedit repositories

//写入如下内容

[repositories]

local

huaweicloud-maven: https://repo.huaweicloud.com/repository/maven/

maven-central: https://repo1.maven.org/maven2/

huaweicloud-ivy: https://repo.huaweicloud.com/repository/ivy/, [organization]/[module]/(scala_[scalaVersion]/)(sbt_[sbtVersion]/)[revision]/[type]s/[artifact](-[classifier]).[ext]

//

//配置环境变量

sudo gedit ~/.bashrc

//最后一行加入以下内容

export PATH=$PATH:/usr/local/sbt

//--------------------------------------------------

//安装Verilator

//--------------------------------------------------

sudo apt-get install git make autoconf g++ flex bison libz-dev

sudo git clone http://git.veripool.org/git/verilator //或使用{git clone https://github.com/verilator/verilator}

sudo chmod 777 -R verilator/

unsetenv VERILATOR_ROOT //命令无效果时可忽略

unset VERILATOR_ROOT

cd verilator

sudo git pull

sudo git checkout v4.216

autoconf

./configure

make

sudo make install

//--------------------------------------------------

//安装OpenOCD,配置使其支持DapLink.

//--------------------------------------------------

sudo apt install libtool automake pkg-config libusb-1.0-0-dev libz-dev

sudo apt-get install libtool automake libusb-1.0.0-dev texinfo libusb-dev libyaml-dev pkg-config

sudo git clone https://github.com/SpinalHDL/openocd_riscv.git

cd openocd_riscv/

sudo git submodule update --init --recursive

sudo chmod 777 -R ../openocd_riscv

sudo ./bootstrap

sudo apt-get install libhidapi*

./configure --enable-maintainer-mode --enable-usb_blaster_libftdi --enable-ftdi --enable-dummy

make

sudo make install

//--------------------------------------------------

//下载Litex所需的Linux系统镜像,并将其解压到images文件夹中.

//images download address: https://github.com/litex-hub/linux-on-litex-vexriscv/issues/164

//folder address: ../linux-on-litex-vexriscv/images/

//--------------------------------------------------

wget https://github.com/litex-hub/linux-on-litex-vexriscv/files/8331338/linux_2022_03_23.zip

unzip -o linux_2022_03_23.zip -d linux-on-litex-vexriscv/images

//--------------------------------------------------

//运行仿真

//--------------------------------------------------

cd /linux-on-litex-vexriscv

./sim.py

//--------------------------------------------------

//仿真花费的时间很长,请耐心等待,根据设备性能,一般在25分钟以上.

//--------------------------------------------------

//--------------------------------------------------

//如果安装遇到问题,一般是网络不好或没有安装相应的运行库造成的.

//--------------------------------------------------

//--------------------------------------------------

//上板测试(首先要仿真成功)

//--------------------------------------------------

//--------------------------------------------------

//编译

//--------------------------------------------------

cd /linux-on-litex-vexriscv

source /tools/Xilinx/Vivado/2020.2/settings64.sh

./make.py --board=nexys_video --cpu-count=2 --build

//-------------------------------------------------

//使用Litex命令或手动下载FPGA_Bit文件

//--------------------------------------------------

//第一次使用,需要使用Vivado,识别一次板卡,否则下载会出错.

./make.py --board=nexys_video --cpu-count=2 --load

//--------------------------------------------------

//使用Litex命令通过串口下载Linux系统镜像

//--------------------------------------------------

//Litex使用Jtag2Uart(只链接Jtag即可,设备一般为ttyUSB0.)

//--------------------------------------------------

sudo chmod 777 /dev/ttyUSB0

litex_term --images=images/boot.json /dev/ttyUSB0

//--------------------------------------------------

//下载完成后需要进行Reboot,之后进入系统.

//--------------------------------------------------

reboot

//--------------------------------------------------

//Litex Demo

//[Page]{https://github.com/enjoy-digital/litex/tree/master/litex/soc/software/demo}

//--------------------------------------------------

//Litex Demo 生成的SOC与运行linux生成的SOC存在差异,无法通用。

//需要使用物理串口进行程序下载(不支持Jtag2Uart)

//编译并下载SOC到FPGA

source /tools/Xilinx/Vivado/2020.2/settings64.sh

python3 -m litex_boards.targets.digilent_nexys_video --build --load

//编译Demo生成执行文件

litex_bare_metal_demo --build-path=build/digilent_nexys_video

//下载可执行程序到SOC

sudo chmod 777 /dev/ttyUSB1

litex_term /dev/ttyUSB1 --kernel=demo.bin

二、关于litedram

1、定义

官方解释:

LiteDRAM 提供占用空间小且可配置的 DRAM 内核。

LiteDRAM 是 LiteX 库的一部分,其目标是降低入门级 通过提供简单、优雅和高效的实现复杂的FPGA 内核。

当今 SoC 中使用的组件,例如以太网、SATA、PCIe、SDRAM 控制器…使用Migen来描述HDL可以使内核高度且易于配置。

LiteDRAM 可以用作 LiteX 库,也可以与您的标准集成 通过生成将用作标准内核的 Verilog RTL 来设计流程。

官网:LiteDram

litedram消耗的逻辑单元要比Xilinx的MIG减少50%,litedram:3016 个 LUT 和 2530 个寄存器,而 MIG:5673 个 LUT 和 5060 个寄存器。并且,litedram是开源的,支持配置多种接口,支持多种存储芯片,这就是你选择litedram的原因。

2、配置

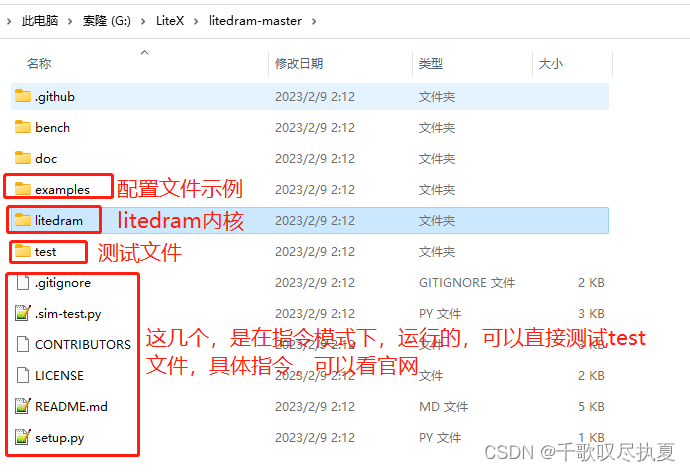

在安装完litex后,目录里面会有一个litedram的文件夹,这个文件夹是独立的,既可以单独运行,也可以配合litex运行。

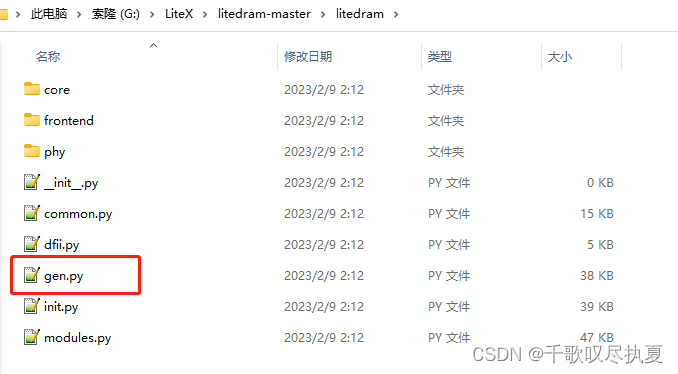

可以看一下他的结构:

这里只看litedram文件跟examples。

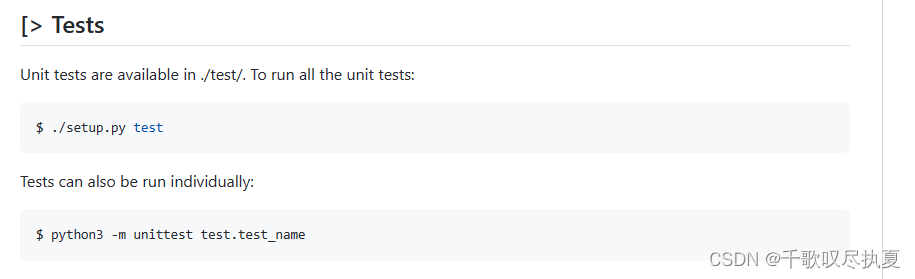

其他的,可以看官网介绍:安装完litex,运行者两条指令,就可以看到测试OK。

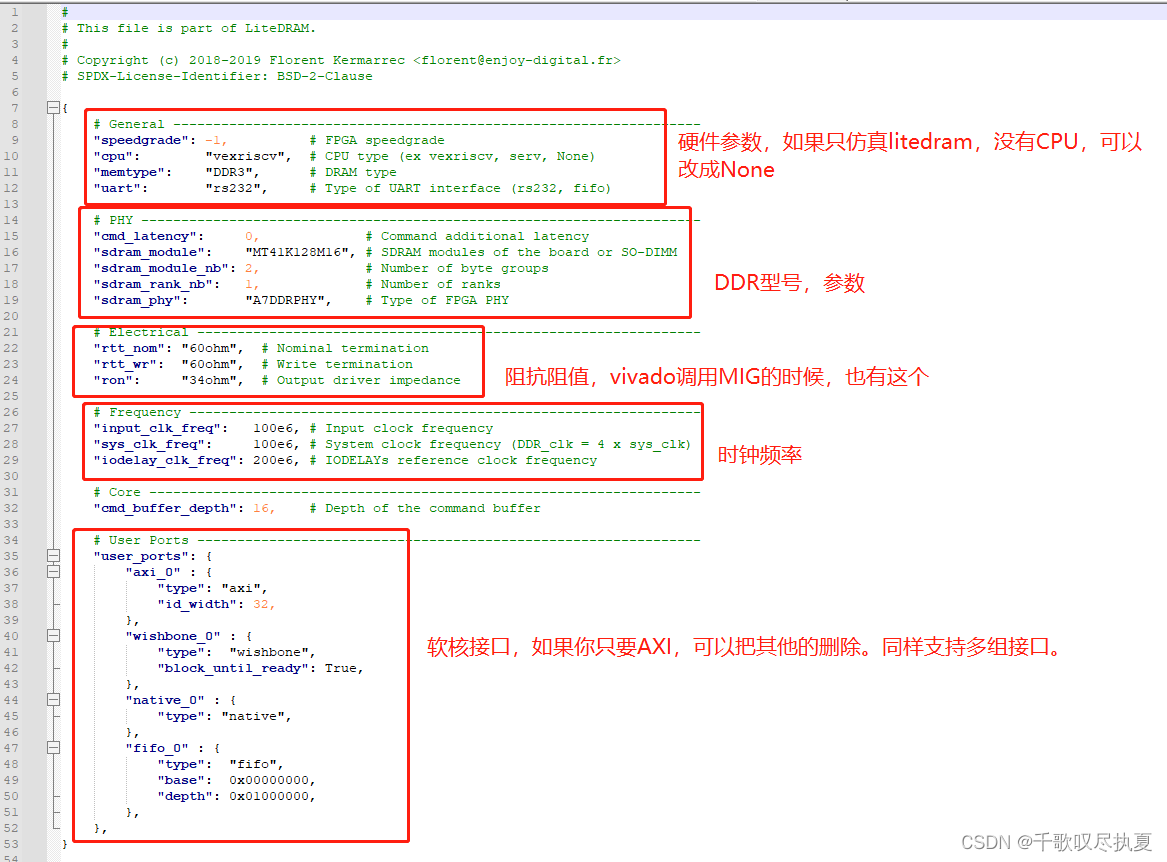

examples文件

官方对于litedram的配置资料没有说明,只给了范本,也没有说怎么导出Verilog文件,这里需要看examples文件夹下的yml文件:

这里面给了多个型号开发板的配置文件,我手上有arty-a7开发板,所以打开arty.yml文件看一下:

有个地方需要提一下:软核接口配置那里,如果你没有设置数据宽度,会被默认为128位。

设置方式:在type下面加一行代码"data_width": 32, #设置数据宽度为32。

litedram文件

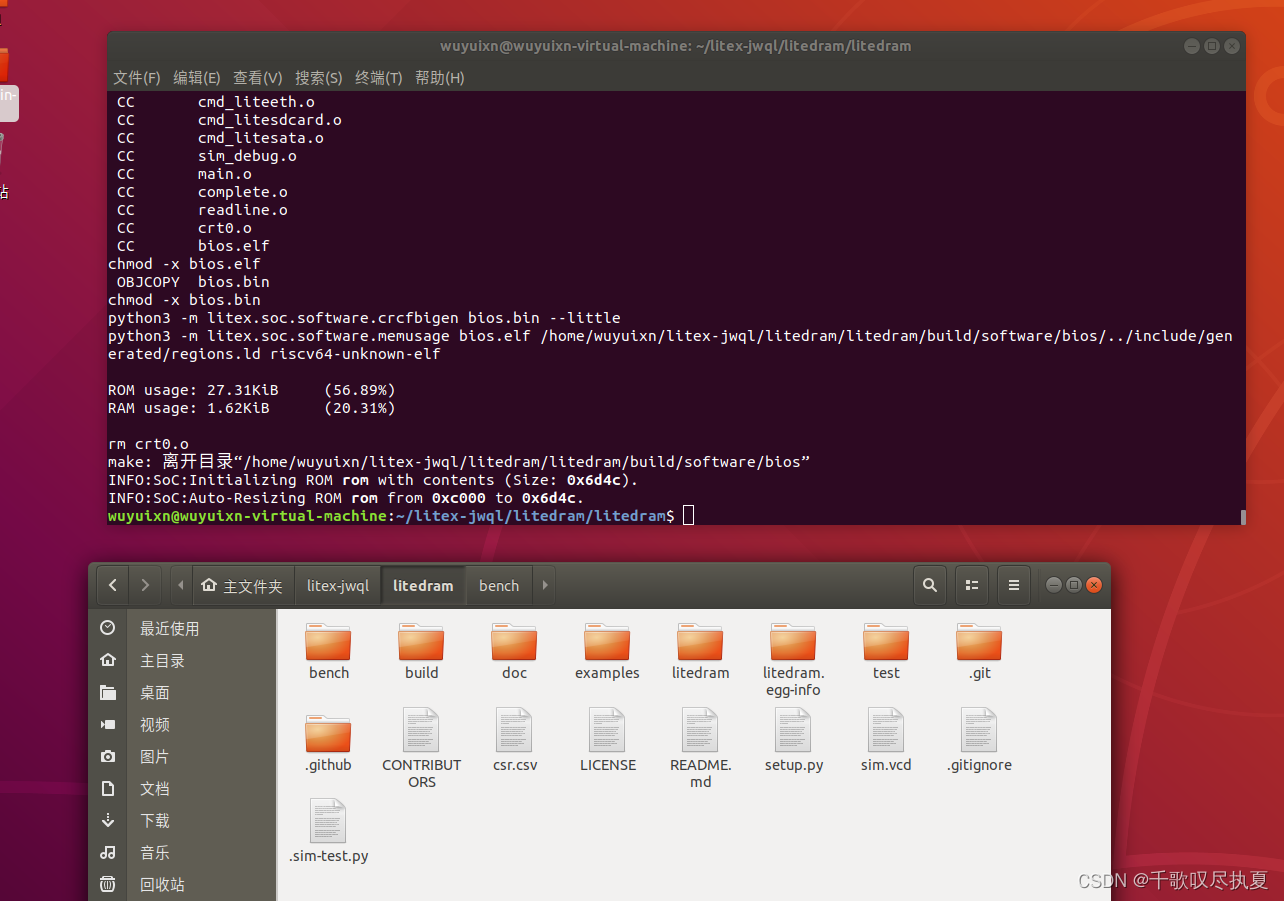

配置完yml文件,接下来就是运行脚本,产生Verilog文件。

先看一下litedram文件结构:

执行gen.py可以导出Verilog文件。

指令为:

Python3 gen.py arty.yml

配置好的yml文件跟gen.py需要放在同个目录下。

执行完,会有一个bulid文件夹,里面会有Verilog文件,及xdc约束文件。如果,你没有修改配置文件,使用默认文件,还会产生一个sin.vcd文件,这个文件可以用GTKWave软件打开,导入test测试文件,可以看到仿真波形。

其实,到这里就这一小节内容就结束了。但是秉着授人以鱼不如授人以渔的原则,我觉得有必要讲一下gen.py跟Python3 gen.py arty.yml是怎么来的(官网没有给,笔者也是琢磨了好久)

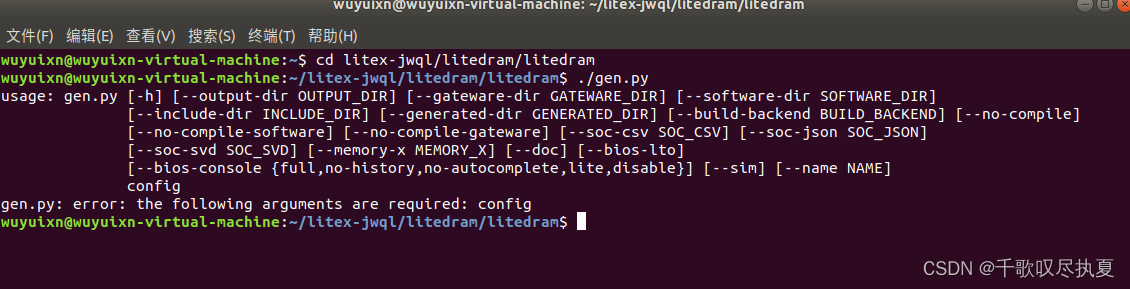

gen.py

如果,你直接运行./gen.py ,那么会报错:

这个错误,说的就是,这份文件缺少配置参数。

所以开看看gen.py,脚本里面,我框起来的,就是最重要的地方,配置参数,如果没读取参数,他会返回什么信息给你。

看到这行代码:读懂这行代码,就好办多了。

core_config = yaml.load(open(args.config).read(), Loader=yaml.Loader)

这里面涉及了Python几个语法:

1、yaml.load( ) 函数

作用:python通过open方式读取文件数据,再通过load函数将数据转化为列表或字典;(后面这段话什么意思,自己可以看一下,我后面的参考链接,有详细解释)

2、open xxxx .read()

打开yml文件,并读取

3、Loader=yaml.Loader

这个完整语法是:yaml.load(f, Loader=yaml.Loader)

作用:

Yaml 5.1 之后的版本为了加强安全性要求指定具体的 Loader,禁止执行任意函数。如果没加,会报错。

// An highlighted block

"""

1.

yaml.load(f, Loader=yaml.FullLoader)

2.

yaml.warnings({'YAMLLoadWarning': False}) # 全局设置警告,不推荐

Loader的几种加载方式

BaseLoader - -仅加载最基本的YAML

SafeLoader - -安全地加载YAML语言的子集。建议用于加载不受信任的输入。

FullLoader - -加载完整的YAML语言。避免任意代码执行。这是当前(PyYAML5.1)默认加载器调用

yaml.load(input)(发出警告后)。

UnsafeLoader - -(也称为Loader向后兼容性)原始的Loader代码,可以通过不受信任的数据输入轻松利用。

"""

``

4、argparse(这个最重要)

作用:argsparse是python的命令行解析的标准模块,内置于python,不需要安装。主要作用是通过命令行运行程序时可以直接向程序传入参数

怎么使用看下面参考。

看完这行代码,这个脚本的结构,你也就了解的差不多了。

参考:

Python YAML 配置文件

yaml.load()函数

yaml.load()报错

YAML配置文件和argparse模块的使用

python argparse 解析yaml文件

三、总结

接下来就是做RTL仿真了,到时候再更新。前面这三项,如果有遇到困难的,可以再私信我,有看到会回复。

AXI接口的litedram.v文件

链接:https://pan.baidu.com/s/1OHd4TJztLCA0AZqD2QHOBQ?pwd=32bx

提取码:32bx

–来自百度网盘超级会员V5的分享