| 芯片设计验证社区·芯片爱好者聚集地·硬件相关讨论社区·数字verifier星球 |

|---|

| 四社区联合力荐!近500篇数字IC精品文章收录! |

| 【数字IC精品文章收录】学习路线·基础知识·总线·脚本语言·芯片求职·EDA工具·低功耗设计Verilog·STA·设计·验证·FPGA·架构·AMBA·书籍 |

一、前言

本系列旨在提供100%准确的数字IC设计/验证手撕代码环节的题目,原理,RTL设计,Testbench和参考仿真波形,每篇文章的内容都经过仿真核对。快速导航链接如下:

1.奇数分频

2.偶数分频

3.半整数分批

4.小数/分数分频

5.序列检测器

6.模三检测器

7.饮料机

8.异步复位,同步释放

9.边沿检测(上升沿,下降沿,双边沿)

10.全加器,半加器

11.格雷码转二进制

12.单bit跨时钟域(打两拍,边沿同步,脉冲同步)

13.奇偶校验

14.伪随机数生成器[线性反馈移位寄存器]

15.同步FIFO

16.无毛刺时钟切换电路

应当说,手撕代码环节是面试流程中既重要又简单的一个环节,跟软件类的岗位相比起来,数字IC的手撕代码题目固定,数量有限,属于整个面试中必得分的一个环节,在这个系列以外,笔者同样推荐数字IC求职者使用“HdlBits”进行代码的训练

链接如下

HDLBits — Verilog Practice

二、题目

1.一个输入序列是8位([7:0])其中七位是数据位[6:0],一位是奇校验位[7],设计一个检测模块,其输入为result(result为0代表奇偶校验正确,result为1代表奇偶校验错误)

三、原理

-

奇偶校验也是电路设计中常用的一个电路或者说功能,它广泛的应用在串口通讯或者高速缓存中,以UART通讯协议为例,一个字符帧的最后一位的校验方式就可以设置成奇偶校验的方式。

-

奇偶校验位有两种类型:偶校验位与奇校验位。

以偶校验位来说,如果一组给定数据位中1的个数是奇数,补一个bit为1,使得总的1的个数是偶数。例:0000001, 补一个bit为1, 00000011。

以奇校验位来说,如果给定一组数据位中1的个数是奇数,补一个bit为0,使得总的1的个数是奇数。例:0000001, 补一个bit为0, 00000010。 -

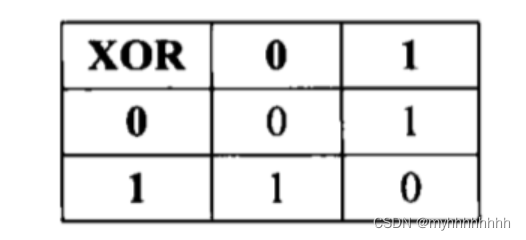

为了搞懂奇偶校验的原理,我们首先需要知道的是异或门,他的真值表如下

-

以这样的一个双输入异或门为例子,我们可以发现,两个输入,有一个为1的时候,输出为1,有0个1或者2个1的时候输出为零,这里其实异或门的概念与奇偶校验的概念就重叠起来了,0和2是偶数,输出是0,1是奇数输出是1,根据此,我们只需要使用缩位运算符“异或”去处理输入的数据数列,就可以去判断偶校验,异或后取反,就可以去判断奇校验位。

四、RTL设计

module oddtest (data,result);

input [7:0] data;

output result;

wire oventest;

assign oddtest = ^data[6:0];

assign result = (data[7] == oddtest ? 1 : 0 );

endmodule

五、Testbench

`timescale 1ns / 1ps

module oventest_tb();

reg [7:0] data;

wire result;

oventest u1(.data(data),.result(result));

initial

begin

data = 8'h01;

#100

data = 8'ha1;

#100

data = 8'h32;

#100

data = 8'he2;

#100

data = 8'hc4;

$stop;

end

endmodule

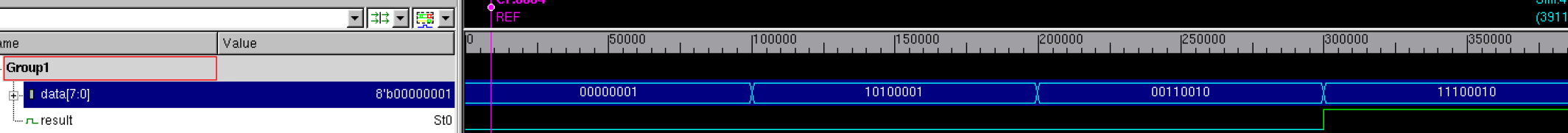

六、仿真分析

这里检测了四个数,可以发现,第三个检测数据有三个1,奇数位判断为0,结果正确,第四个检测数据也是三个1,奇偶位判断为1,结果错误。体现在result拉高上,设计成立。