| 芯片设计验证社区·芯片爱好者聚集地·硬件相关讨论社区·数字verifier星球 |

|---|

| 四社区联合力荐!近500篇数字IC精品文章收录! |

| 【数字IC精品文章收录】学习路线·基础知识·总线·脚本语言·芯片求职·EDA工具·低功耗设计Verilog·STA·设计·验证·FPGA·架构·AMBA·书籍 |

Verilog伪随机数生成器[线性反馈移位寄存器]

一、前言

本系列旨在提供100%准确的数字IC设计/验证手撕代码环节的题目,原理,RTL设计,Testbench和参考仿真波形,每篇文章的内容都经过仿真核对。快速导航链接如下:

1.奇数分频

2.偶数分频

3.半整数分批

4.小数/分数分频

5.序列检测器

6.模三检测器

7.饮料机

8.异步复位,同步释放

9.边沿检测(上升沿,下降沿,双边沿)

10.全加器,半加器

11.格雷码转二进制

12.单bit跨时钟域(打两拍,边沿同步,脉冲同步)

13.奇偶校验

14.伪随机数生成器[线性反馈移位寄存器]

15.同步FIFO

16.无毛刺时钟切换电路

本篇文章中的线性反馈寄存器,属于现代密码学的相关内容,简单来说,线性反馈寄存器的应用场景主要体现在密码学的加密上,线性结构搭配着非线性结构,共同完成加密过程,虽然说线性反馈寄存器属于伪随机数,选用不同的seed,伪随机数生成序列不同,但是同大多数密钥流产生器一样,序列足够长的时候,线性反馈寄存器也会体现其周期性,线性反馈移位寄存器(LSFR),具体可以细分为斐波那契LFSR,伽罗瓦LFSR,他们的具体结构相似,但面积或速度更优化。

二、题目

使用Verilog,设计如下电路,复位是q[4:0]的值为11110(改编自HDLBits Lfsr5)输出的位置在q[0]处。

三、原理

3.1 移位寄存器

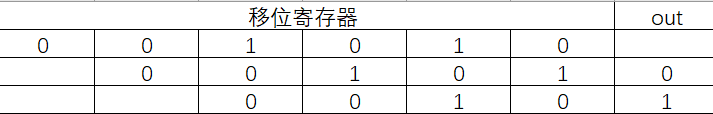

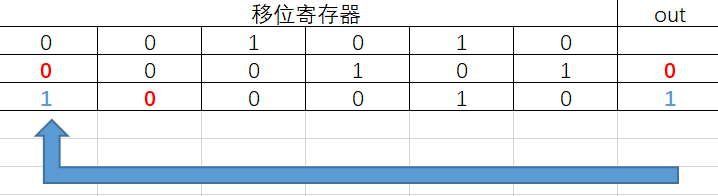

以上的图片显示了移位寄存器的数据移动,在reset信号到来时,移位寄存器复位成001010,之后随着clk上升沿,不断右移,输出结果为out,reset信号到来时,移位寄存器的初值为1或是0,决定了移位寄存器的seed,同样一个结构,seed不同,输出的out序列就不一样,这里的内容倒是与verilog中的系统函数$random(seed)添加种子生成随机数异曲同工,读者可以好好思考一下。

3.2 反馈回路

假如我们将out连接回移位寄存器的头部,就形成了一个反馈回路,新的移位寄存器的输出序列图如下所示,跟随clk信号打拍,这个序列可以一直输出下去。

3.3 Update反馈回路

不简单的进行移位,而是在移位的基础上加上异或门,如题目中所示,这就相当于每进行一次移位,寄存器中的值会发生改变,一直移动,一直改变,就形成了伪随机数。

四、RTL设计

module LSFR(clk,rst_n,out);

input clk;

input rst_n;

output out;

reg [4:0] shift_reg;

assign out = shift_reg[0];

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

shift_reg <= 5'b1_1110;

else

begin

shift_reg [4] <= shift_reg [0]^1'b0;

shift_reg [3] <= shift_reg [4];

shift_reg [2] <= shift_reg [3]^shift_reg[0];

shift_reg [1] <= shift_reg [2];

shift_reg [0] <= shift_reg [1];

end

end

endmodule

五、Testbench设计

`timescale 1ns / 1ps

module LSFR_Tb();

reg clk;

reg rst_n;

wire out;

LSFR u1(.clk(clk),.rst_n(rst_n),.out(out));

always #5 clk = ~clk;

initial

begin

clk = 0;

rst_n=1;

#4

rst_n = 0;

#25

rst_n = 1;

#40;

#1000

$stop;

end

endmodule

六、仿真分析

可以发现,从M1到M2与M2到M3的序列是重复的,印证了之前作者所说序列足够长时的伪随机数生成器的周期性。