电路图

链接:https://pan.baidu.com/s/1UF8STkWRZYxt0SMp7NsdrA?pwd=2333

提取码:2333

–来自百度网盘超级会员V5的分享

以下为电路连接图

电路图直接下载打开即可:

链接:https://pan.baidu.com/s/12iHIjwQfdnJ6voyIzGDAJQ?pwd=2333

提取码:2333

上面的图片中对线路的连接和每个组件的名称都有明确的说明。

以下为检验步骤

2.进行电路预设置,具体步骤如下:

1)将ALU - BUS设为高电平,关闭 ALU 输出端的三态门;

将ALU - BUS拨到向上

2) 将两片 74LS273 的MR都设为高电平,否则 74LS273 会一直处于清零状态。

将MR拨到向上

3. 打开电源开关。

4. 设置 SW7~SW0 向 DR1 和 DR2 置数。以 DR1=65H, DR2=A7H 为例,具体步骤如下:

1) 将SW - BUS置 0,打开数据输入端的三态门;

将SW - BUS拨到向下

2) 将数据开关的 SW7~SW0 置为 01100101;

根据上1下0的规则设置

3) 发出 P1 单脉冲信号,在 P1 的上升沿,数据打入寄存器 DR1;

点击P1

4) 将数据开关的 SW7~SW0 置为 10100111;

根据上1下0的规则设置

5) 发出 P2 单脉冲信号,在 P2 的上升沿,数据打入寄存器 DR2。

点击P2

6) 将SW - BUS置 1,关闭数据输入端的三态门;

将SW - BUS拨到向上

5. 检验 DR1 和 DR2 中存的数是否正确。其具体操作如下:

1) ALU - BUS=0,打开 ALU 输出端的三态门;

将ALU - BUS拨到向下

2) 设置 Cn=1, ALU 无进位输入;

将Cn拨到向上

3) 将 S3、 S2、 S1、 S0、 M 置为 00000,指示灯应显示 DR1 中数据 01100101;

根据上1下0的规则设置

4) 将 S3、 S2、 S1、 S0、 M 置为 10101,指示灯应显示 DR2 中数据 10100111。

根据上1下0的规则设置

检测图

小灯泡对亮了对应1,没亮对应0,判断自己电路是否正确即可。

具体的实验测量仿照根据上述过程即可。

报告

实验1运算器实验

1.1实验目的

(1)掌握算术逻辑运算单元的工作原理。

(2)熟悉简单运算器的电路组成。

(3)熟悉4位运算功能发生器(74LS181)的算术、逻辑运算功能。

1.2实验要求

(1)做好实验预习,看懂电路图,熟悉实验中所用芯片各引脚的功能和连接方法。

(2)按照实验内容与步骤的要求,认真仔细地完成实验。

(3)写出实验报告。

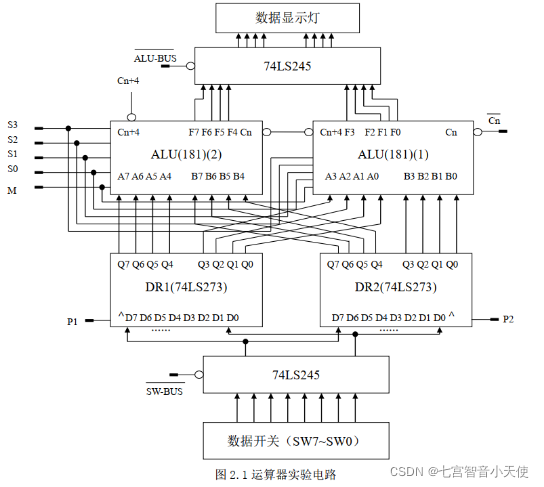

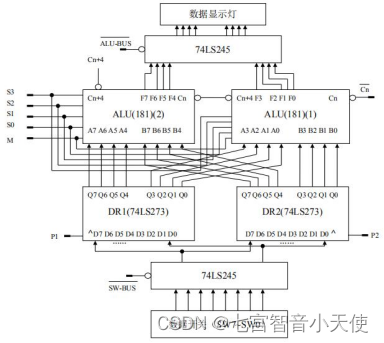

1.3实验原理

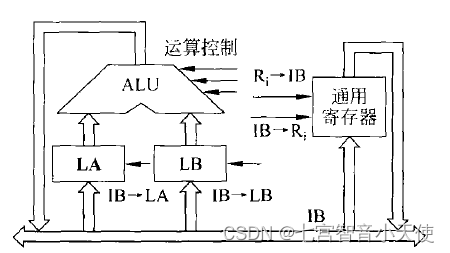

运算器实验电路如图1.1所示。两片4位的74LS181构成8位字长的ALU。其中74LS181(1)做低4位算术逻辑运算,74LS181(2)做高4位算术逻辑运算,74LS181(1)的进位输出信号Cn+4与74LS181(2)的进位输入信号Cn相连,两片74LS181的控制信号S3S0、M分别相连。74LS181(2)的进位输出信号Cn+4可另接一个指示灯,用于显示运算器进位标志信号状态。两个8位的74LS273作为工作寄存器DR1和DR2,用于暂存参与运算的操作数。参与运算的数据由数据开关通过三态门74LS245送入工作寄存器,ALU的运算结果也通过三态门74LS245发送到数据显示灯上。参与运算的操作数由SW7SW0共8个二进制开关来设置,当=0时,数据通过三态门74LS245输出到DR1和DR2。DR1接ALU的A输入端口,DR2接ALU的B输入端口。在P1的上升沿将数据打入DR1,送至74LS181的A输入端口;在P2的上升沿将数据打入DR2,送至74LS181的B输入端口。

另外,图1.1中尾巴上带加粗标记的线条为控制信号线,其余为数据线。实验电路中涉及的控制信号如下:

1)M:选择ALU的运算模式(M=0,算术运算;M=1,逻辑运算)。

2)S3,S2,S1,S0:选择ALU的运算类型,例如在算术运算模式下设为1001则ALU做加法运算,详见74LS181功能表1-1。

3):向ALU最低位输入的进位信号,=0时有进位输入,=1时无进位输入。

4)Cn+4:ALU最高位向外输出的进位信号,为0时有进位输出,为1时无进位输出。

5)P1:脉冲信号,在上升沿将数据打入DR1。74LS273触发器在时钟输入为高电平或低电平时,输入端的信号不影响输出,仅仅在时钟脉冲的上升沿,输入端数据才会发送到输出端,并将数据锁存。

6)P2:脉冲信号,在上升沿将数据打入DR2。

7)芯片74LS273的清零信号,低电平有效。当为电平时,74LS273的数据输出引脚被置零。

8):ALU输出三态门使能信号,为0时将74LS245输入引脚的值从输出引脚输出,从而将ALU运算结果输出到数据总线。

9):开关输出三态门使能信号,为0时将SW7~SW0数据送到数据总线。

图1.1 运算器实验电路

1.4实验内容与步骤

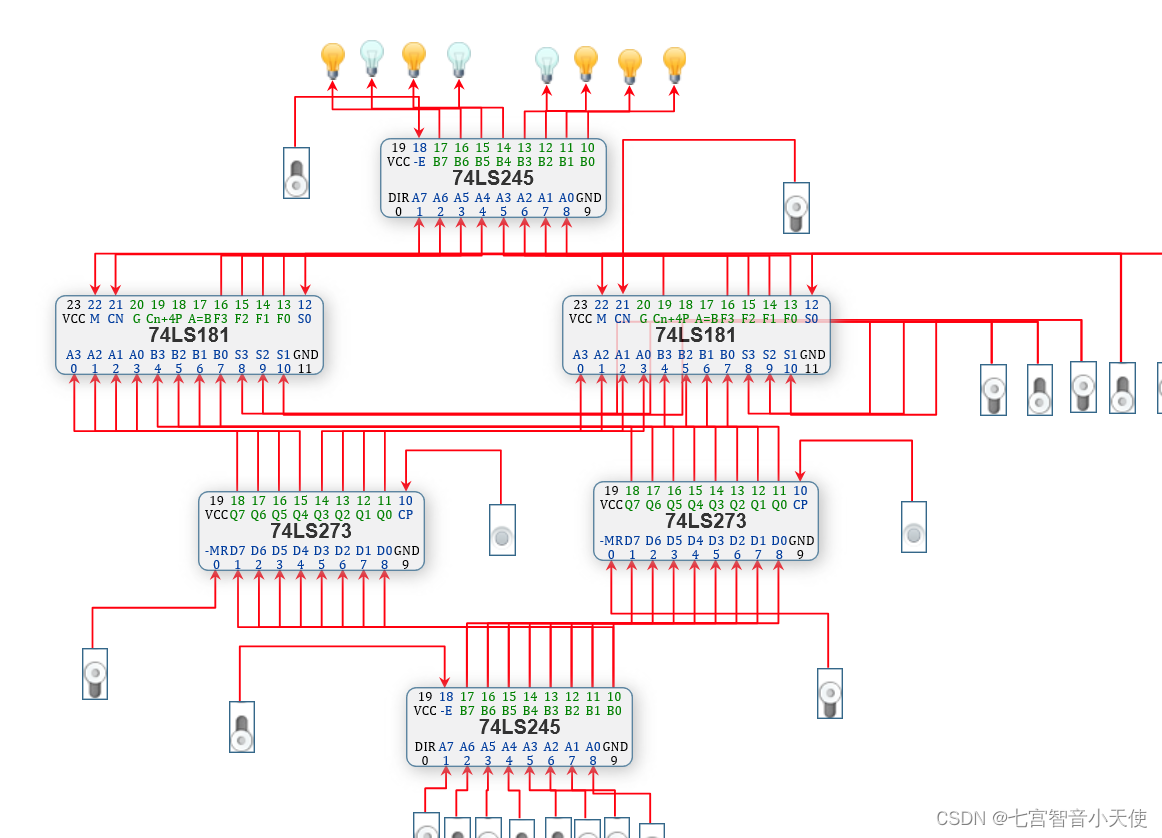

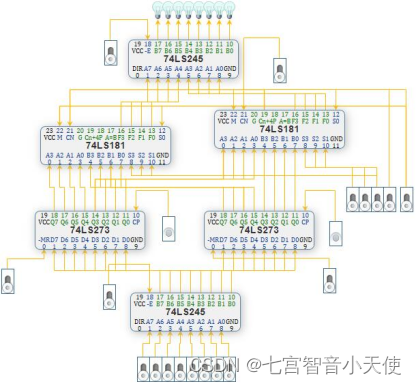

1.运行虚拟实验系统,按照图1.1绘制运算器实验电路,生成实验电路如图1.2所示:

图1.2 运算器虚拟实验电路

2.进行电路预设置,具体步骤如下:

(1)将设为高电平,关闭ALU输出端的三态门;

(2)将两片74LS273的都设为高电平,否则74LS273会一直处于清零状态。

3.打开电源开关。

4.设置SW7~SW0向DR1和DR2置数。以DR1=65H,DR2=A7H为例,具体步骤如下:

(1)将置0,打开数据输入端的三态门;

(2)将数据开关的SW7~SW0置为01100101;

(3)发出P1单脉冲信号,在P1的上升沿,数据打入寄存器DR1;

(4)将数据开关的SW7~SW0置为10100111;

(5)发出P2单脉冲信号,在P2的上升沿,数据打入寄存器DR2。

(6)将置1,关闭数据输入端的三态门;

5.检验DR1和DR2中存的数是否正确。其具体操作如下:

(1)=0,打开ALU输出端的三态门;

(2)设置Cn=1,ALU无进位输入;

(3)将S3、S2、S1、S0、M置为00000,指示灯应显示DR1中数据01100101;

(4)将S3、S2、S1、S0、M置为10101,指示灯应显示DR2中数据10100111。

6.验证74LS181的算术运算和逻辑运算功能(采用正逻辑)。在给定DR1=65H,DR2=A7H

的情况下,改变运算器的功能模式,观察运算器的输出,并填入表1-1,并和理论值进行比较、验证。

1.5 实验结果

1.6 思考与分析

-

运算器主要由哪些器件组成?这些器件是怎样连接的?

运算器是由算术逻辑单元(ALU)、累加寄存器、数据缓冲寄存器和状态条件寄存器组成。

-

芯片 74LS181 没有减法:A minus B 的指令,怎样实现减法功能?

在减法运算时,可用减法取反码运算后用加法器实现。