实验一 CPU指令运算器设计

- 实验目的

- 掌握QuartusII等实验工具的输入、综合、仿真、下载的使用方法

- 掌握DE2开发版的器件功能特性和使用方法

- 掌握Verilog HDL组合逻辑系统设计的主要方法和技术

- 掌握并应用设计的方法和流程

- 预习要求

- 了解QuartusII等管教分配、下载的方法和流程

- 了解开发板输入、输出显示资源的工作特性

- 了解开发板设计、开发和测试的方法和流程

- 实验要求

设计一个简单的CPU指令运算器,指令格式如下。

操作类型1

操作数1

操作类型2

操作数3

操作数4

完成的具体功能定义如下:

- 操作类型1:将操作数1作为一个无符号二进制数,在七段管以十进制显示二进制序列等效值。

- 操作类型2:实现操作数3、操作数4之间相加、减、乘的操作,在七段管以十/十六进制进制显示操作数和结果。操作数3和4为BCD码表示的2位十进制数(表示的值为00-99)。

注意:

- 操作类型2中,减法逻辑中出现负数,则显示“-”,正数可以不显示符号

- 操作类型2中,加、减、乘操作数和结果都用十进制显示,可以在七段管上进行循环显示来实现。

- 注意操作数3、4以BCD码输入,超过9的BCD码输出处理问题。

- 尝试加法运算采用流水线方式实现。注意有效位数。

- 如果感觉七段管显示能力弱,可以查询LCD1602的控制模块代码,采用LCD显示。

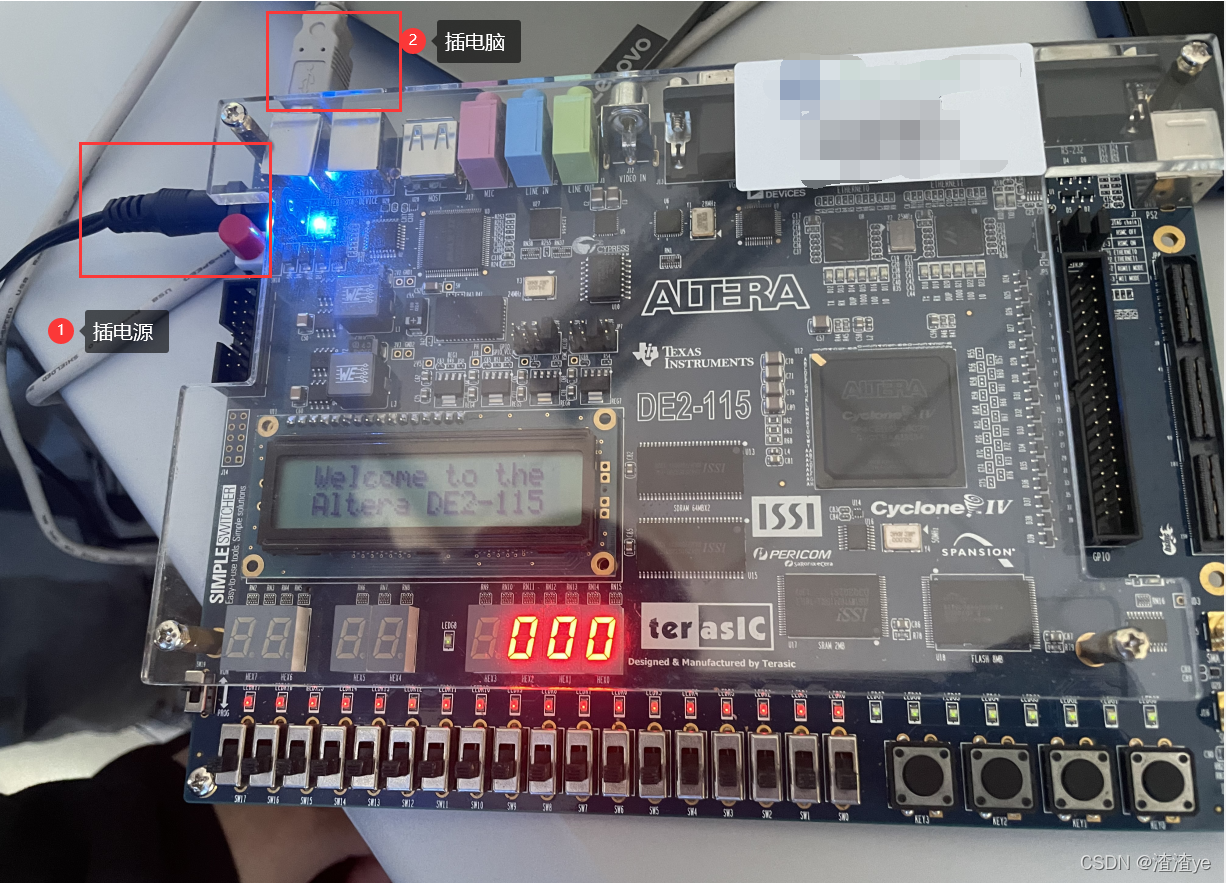

1.先把板子插到电脑上(黑线电源,白线电脑)

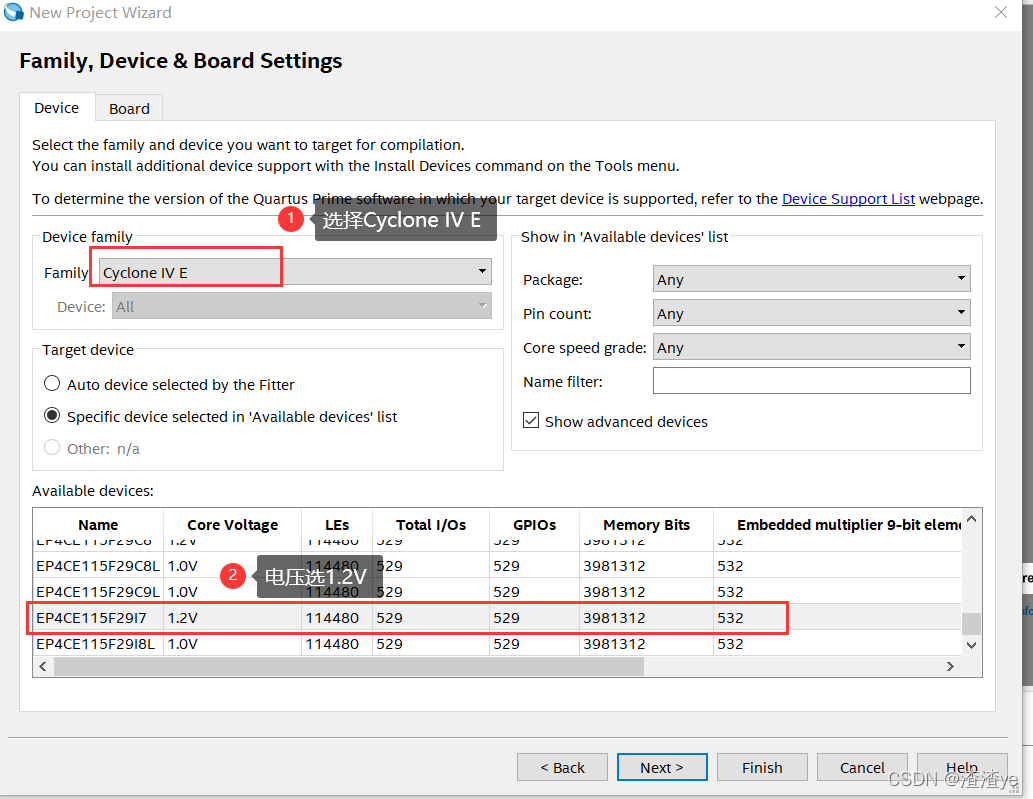

2.在开始设置板子内,选择Cyclone IV E,随后下方电压选择1.2V(ce115f29系列的板子)的即可

3.完成板子的配置后,输入主文件代码:

module zhiling(key,x2,x3,Hex0,Hex1,Hex2,Hex3,Hex4,Hex5,Hex6,Hex7,x);

input [7:0] x2,x3;

input key;

reg[7:0] x1;

input [1:0] x;//表示七段管的显示模式

output reg[6:0] Hex0,Hex1,Hex2,Hex3,Hex4,Hex5,Hex6,Hex7;

reg[11:0] add;

reg[7:0] sub;

reg[13:0] mul;

wire[7:0] n3,n2;

integer flag;//符号标志位

//加法变量

reg cout1,cout2;

reg [6:0] fh;

reg [3:0] low,low0,mid,mid0;

reg [3:0] a1,a2,a3,a4;//乘法各位表达

reg [3:0] t1,t2,t3;//x1的值

reg [3:0] s1,s2;

assign n2=x2[7:4]*10+x2[3:0];

assign n3=x3[7:4]*10+x3[3:0];

always@(*)

begin

if(key==1)

begin

x1=x2;

t1=x1%4'b1010;

t2=x1/4'b1010%4'b1010;

t3=x1/4'b1010/4'b1010;

end

end

//加法,二级流水线方式

always@(*)

begin

{cout1,low0}=x2[3:0]+x3[3:0];

if(cout1==1) begin low=low0+4'b0110; end

else if(low0>9&&cout1==0) begin {cout1,low}=low0+4'b0110;end

else begin low=low0;cout1=0;end

end

always@(*)

begin

{cout2,mid0}=x2[7:4]+x3[7:4]+cout1;

if(cout2==1) begin mid=mid0+4'b0110; end

else if(mid0>9&&cout2==0) begin {cout2,mid}=mid0+4'b0110;end

else begin mid=mid0;cout2=0;end

add={cout2,mid,low};

end

//减法

always@(*)

begin

flag=0;

if(n2>=n3) sub=n2-n3;

else begin flag=1;sub=n3-n2;end

fh=(flag==1)?7'b0111111:7'b1111111;

s1=sub%4'b1010;

s2=sub/4'b1010;

end

//乘法

always@(*)

begin

mul=n2*n3;

a1=mul%4'b1010;

a2=mul/4'b1010%4'b1010;

a3=mul/4'b1010/4'b1010%4'b1010;

a4=mul/4'b1010/4'b1010/4'b1010;

end

always@(x)

begin

case(x)

2'b00:begin {Hex2,Hex1,Hex0}={show(t3),show(t2),show(t1)};Hex3=7'b1111111;Hex4=7'b1111111;Hex5=7'b1111111;Hex6=7'b1111111;Hex7=7'b1111111;end

2'b01:begin {Hex7,Hex6}={show(x2[7:4]),show(x2[3:0])};{Hex5,Hex4}={show(x3[7:4]),show(x3[3:0])};

{Hex2,Hex1,Hex0}={show(add[11:8]),show(add[7:4]),show(add[3:0])};Hex3=7'b1111111; end

2'b10:begin {Hex7,Hex6}={show(x2[7:4]),show(x2[3:0])};{Hex5,Hex4}={show(x3[7:4]),show(x3[3:0])};

{Hex2,Hex1,Hex0}={fh,show(s2),show(s1)};Hex3=7'b1111111; end

2'b11:begin {Hex7,Hex6}={show(x2[7:4]),show(x2[3:0])};{Hex5,Hex4}={show(x3[7:4]),show(x3[3:0])};

{Hex3,Hex2,Hex1,Hex0}={show(a4),show(a3),show(a2),show(a1)}; end

endcase

end

function [6:0]show;

input[3:0] a0;

reg[6:0] b;

begin

case(a0)

4'd0:b=7'b1000000;

4'd1:b=7'b1111001;

4'd2:b=7'b0100100;

4'd3:b=7'b0110000;

4'd4:b=7'b0011001;

4'd5:b=7'b0010010;

4'd6:b=7'b0000010;

4'd7:b=7'b1111000;

4'd8:b=7'b0000000;

4'd9:b=7'b0011000;

default:b=7'b1111111;

endcase

show=b;

end

endfunction

endmodule

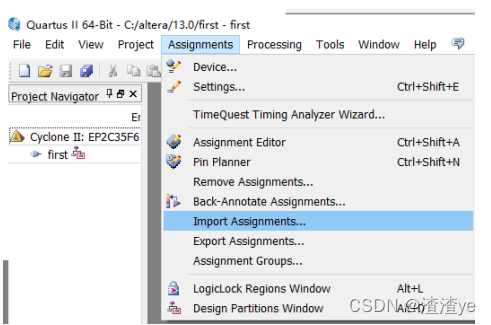

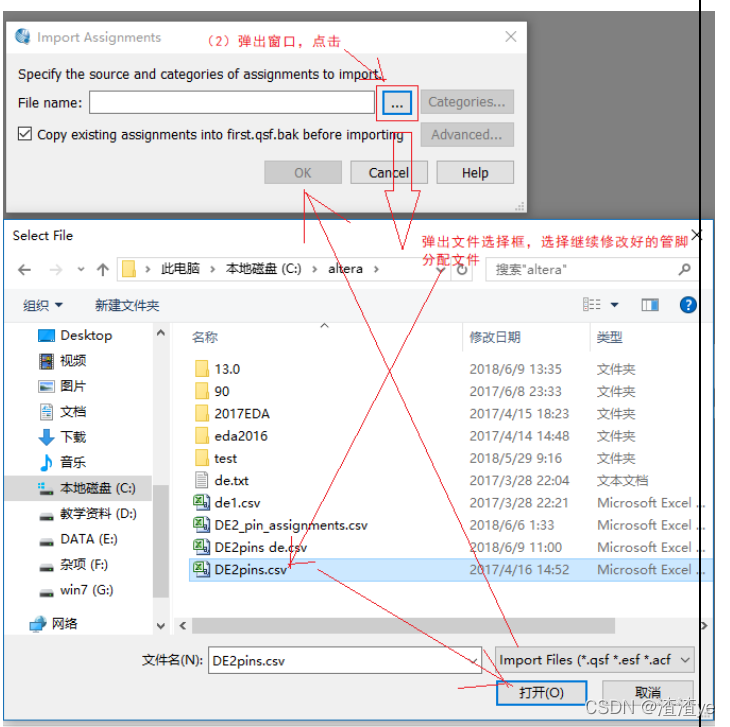

4.点击import assignment

5.导入管脚分配,实验一的数据集下载链接:

fpga硬件实验一CPU指令运算器设计管脚配置-数据集文档类资源-CSDN下载

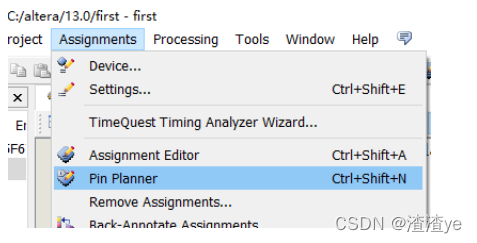

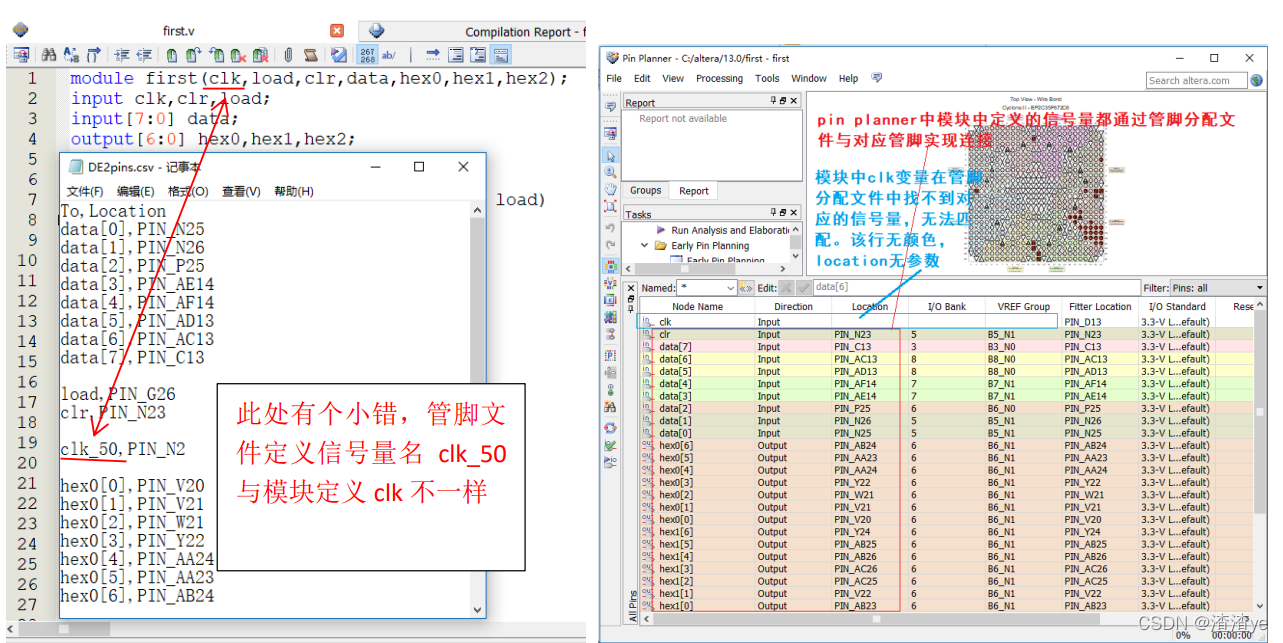

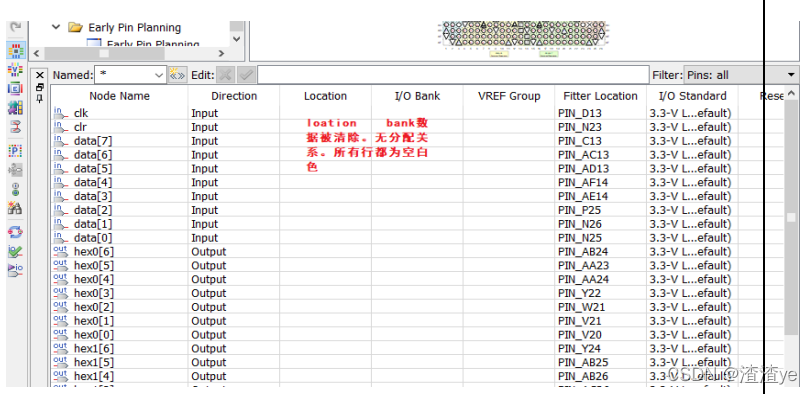

6.随后打开 Pin Planner,查看管脚是否连接正常

7.first模块定义的接口和管脚分配文件对应。导入管脚分配文件后,查看 pin planner 中管脚连接情况。如果出现空白行,说明管脚文件出错,需要修改,重新导入。(已测试过,若用上述链接导入管脚,可正常运行,这一步可省略)

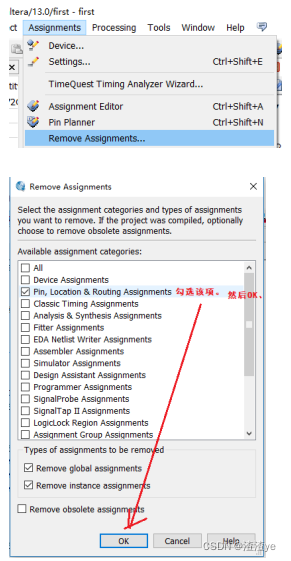

8.若修改管脚分配文件,需要将原来导入的管脚文件移除,remove assignments。重新打开 pin planer 会发现连接清楚,所有行都变为无色。(已测试过,若用上述链接导入管脚,可正常运行,这一步可省略)

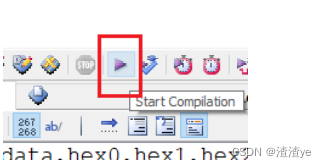

9.正确导入管脚分配表,无错误后。重新综合整个工程

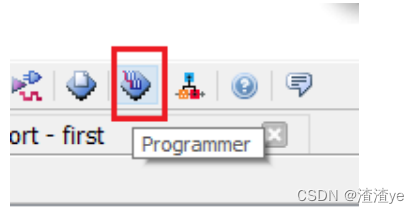

10.综合完毕,无错误后。连接好开发板,开启电源,准备下载。

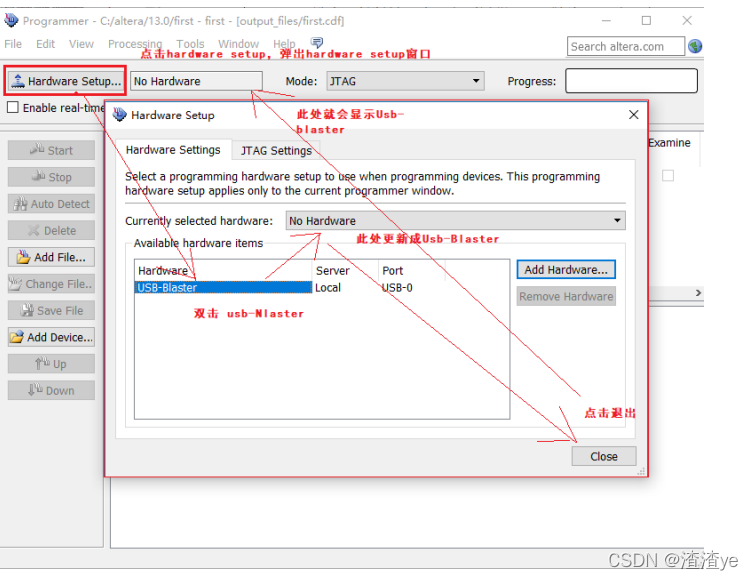

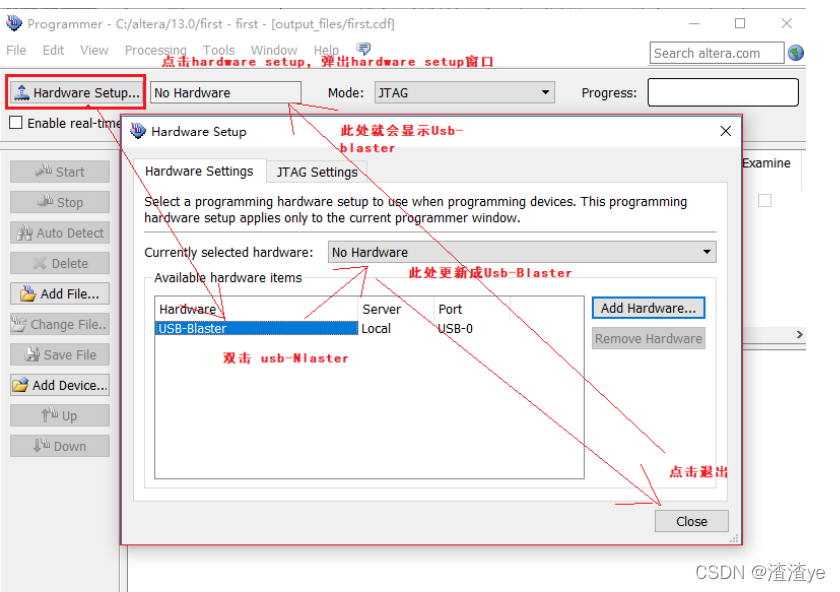

在 programmer 窗口,可能如框中显示 no hardware,没有硬件。点击 hardware setup 功能。 弹出 hardware setup 窗口,添加硬件。

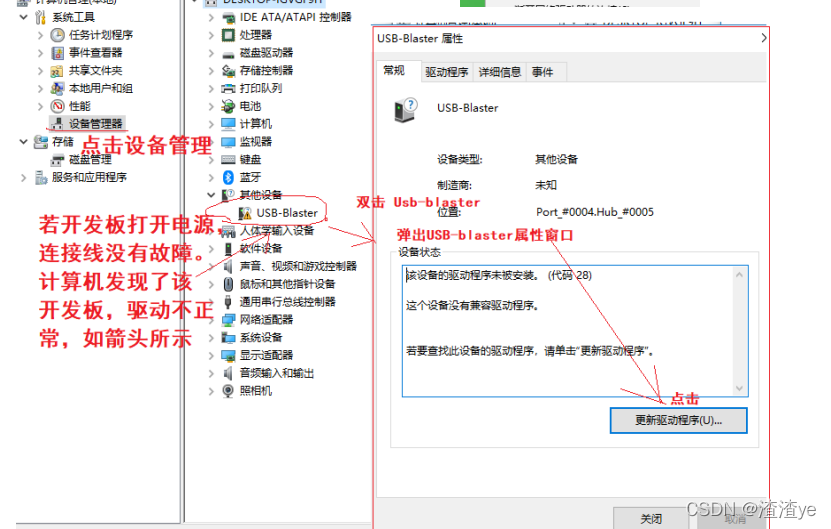

11.若没有USB驱动,则需要手动更新驱动

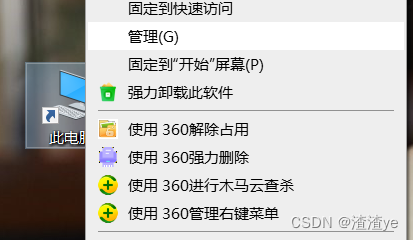

右击“我的电脑”图标,选择“管理”

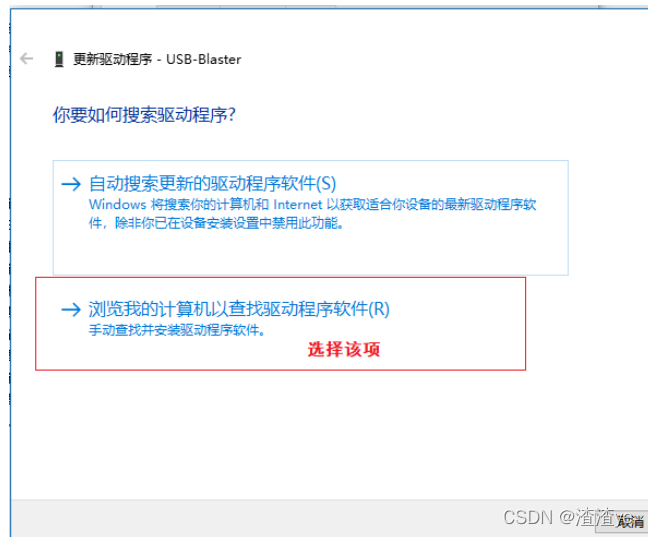

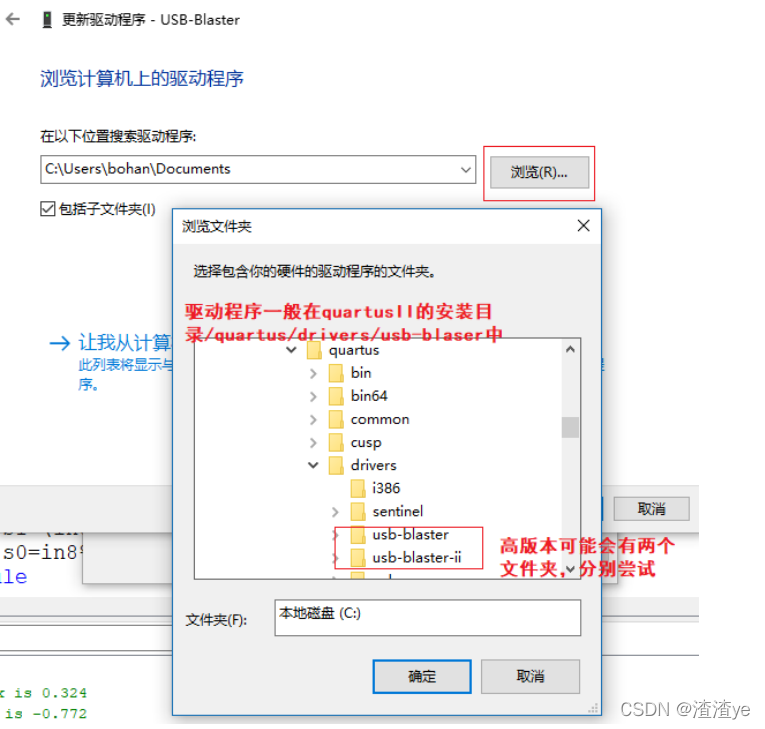

12.选择“手动搜索”,进入Quartus prime安装目录文件,找到“USB”

13.两个“USB”任选一个即可(到时候在硬件115板的插口上选一个插就行)

14.安装完成后,即可

15. 完成驱动更新后,再次点击Programmer 窗口,点击 hardware setup 功能。 弹出 hardware setup 窗口,添加硬件

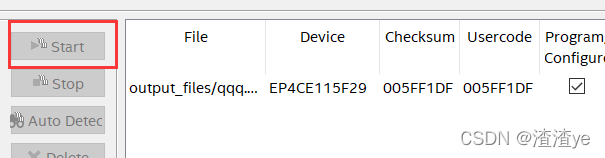

16.配置完成后直接点击Start即可

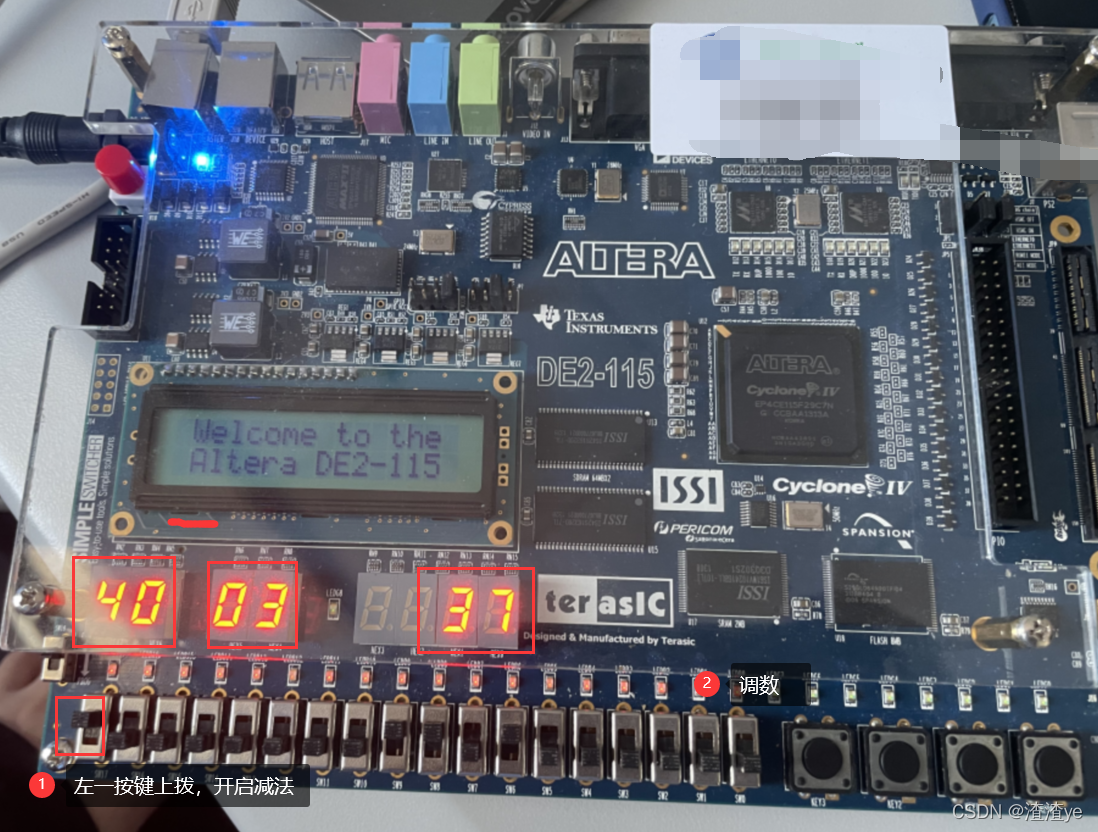

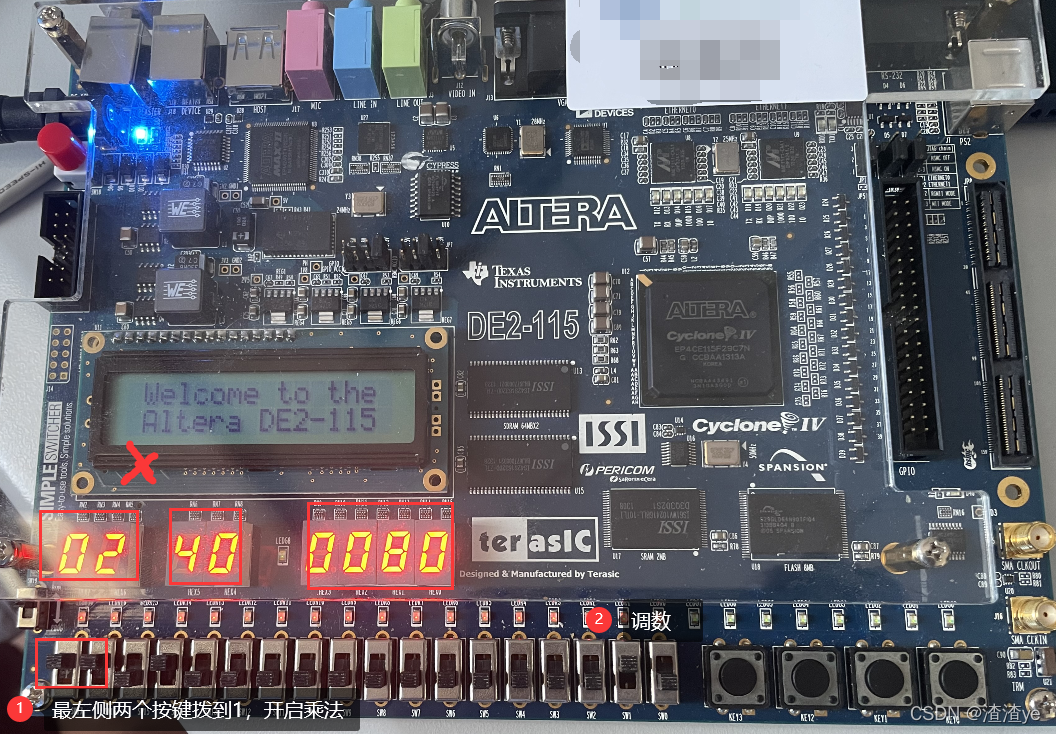

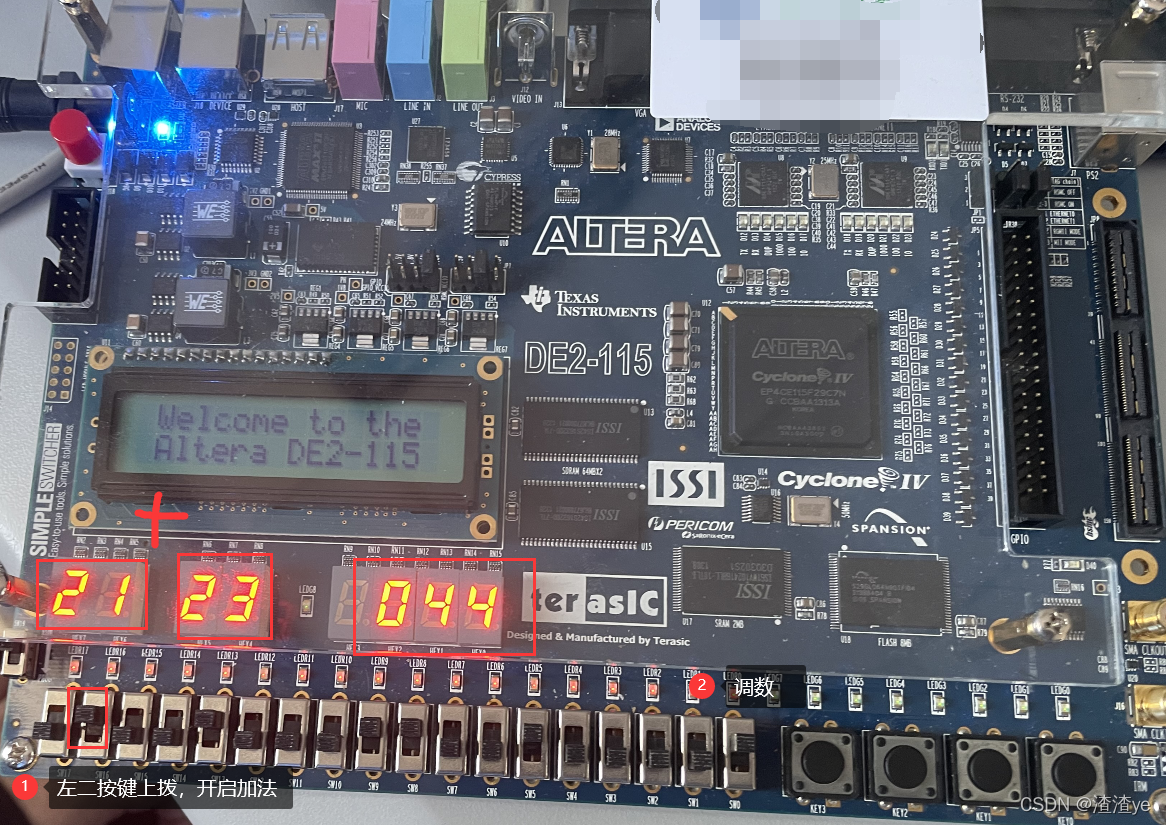

随后开始硬件测试,实验一是CPU指令运算器,加减乘的运算

乘法:

加法:

减法: