实验一:FPGA实验项目创建,编译和下载

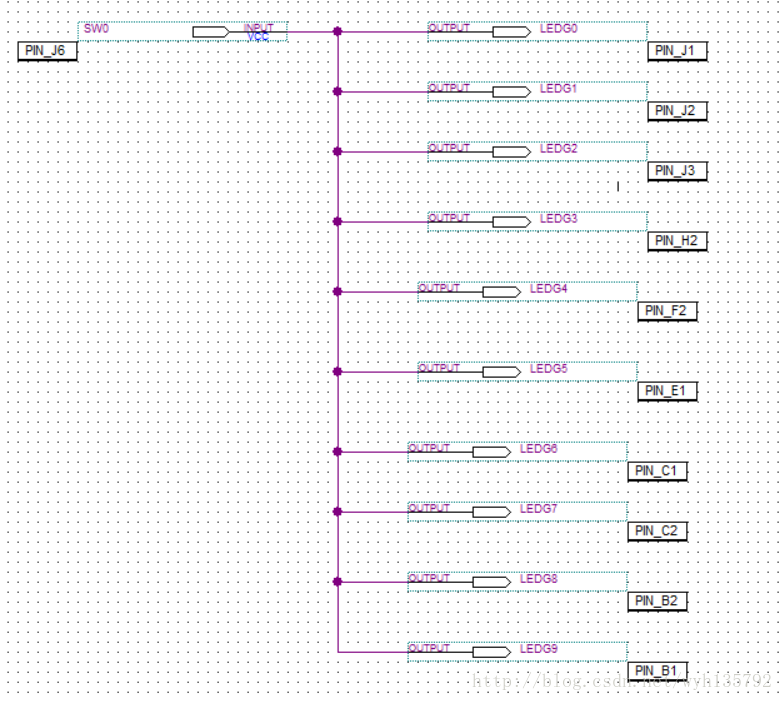

用一个开关控制所有LED灯的亮灭!

实验二:FPGA实验译码器组合逻辑

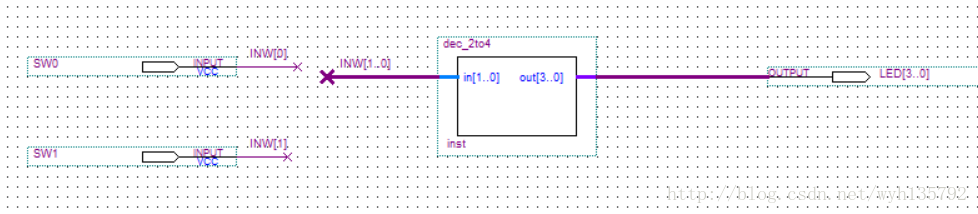

2—4译码器

module dec_2to4(in,out);

input[1:0] in;

output[3:0] out;

reg[3:0] out;

always@(in)

begin

case(in)

2'b00:out=8'b0000;

2'b01:out=8'b0010;

2'b10:out=8'b0100;

2'b11:out=8'b1000;

endcase

end

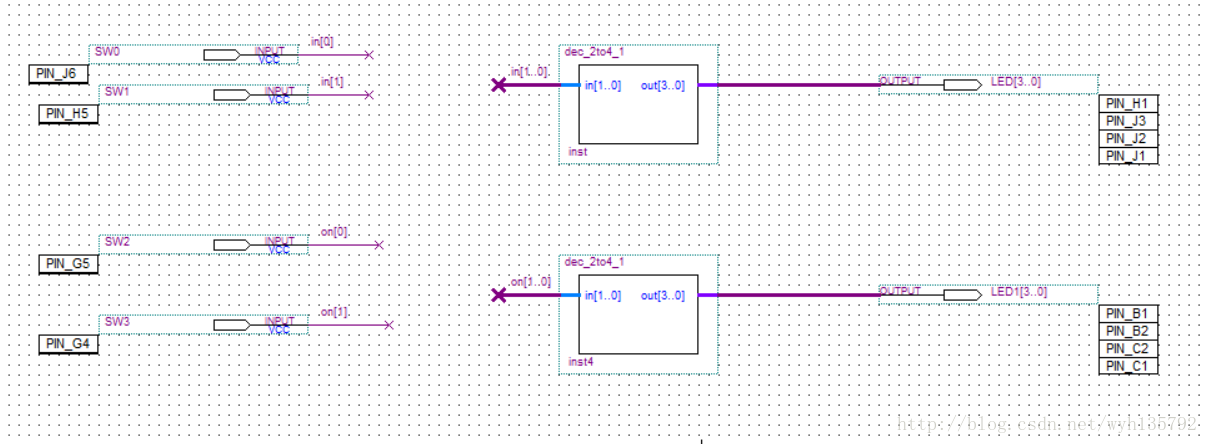

endmodule注:网标式的连接方法 (1)导线命名方法:导线上右键,properties,name,然后设定 名称,中括号表示该导线是一个bus的一部分

(2) 线网的选择使用 两个点号“..”,例如图中的inW[1..0],表 示其包含了inW[0]和inW[1]两根导线(3)这种使用导线的名称来进行连接电路的方法叫做网(络) 标(号)式连接

2个2-4译码器模块

注:引脚锁定已经完成

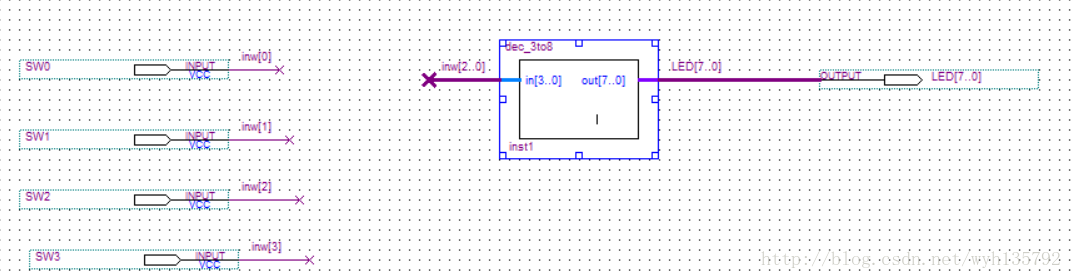

3-8译码器模块

module dec_3to8(in,out);

input[3:0] in;

output[7:0] out;

reg[7:0] out;

always@(in)

begin

case(in)

3'b000:out=8'b00000001;

3'b001:out=8'b00000010;

3'b010:out=8'b00000100;

3'b011:out=8'b00001000;

3'b100:out=8'b00010000;

3'b101:out=8'b00100000;

3'b110:out=8'b01000000;

3'b111:out=8'b10000000;

endcase

end

endmodule开关控制译码管

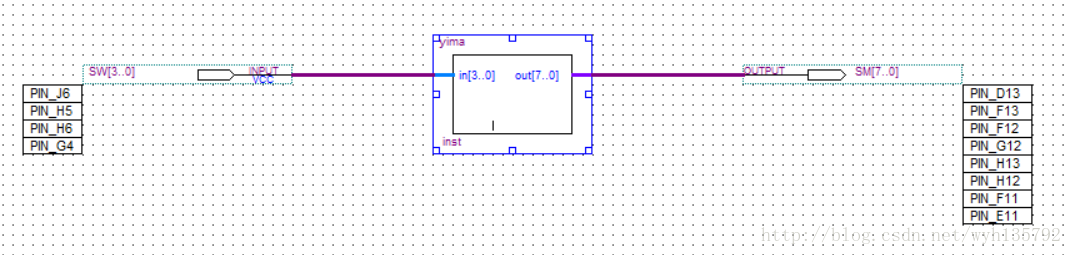

要求:用4个拨码开关控制一个7段译码器的数字,从 0-9-A-F,共16个数字和字母

module yima(in,out);

input[3:0] in;

output[7:0] out;

reg[7:0] out;

always@(in)

begin

case(in)

4'b0000:out=8'b11000000;

4'b0001:out=8'b11111001;

4'b0010:out=8'b10100100;

4'b0011:out=8'b10110000;

4'b0100:out=8'b10011001;

4'b0101:out=8'b10010010;

4'b0110:out=8'b10000010;

4'b0111:out=8'b11111000;

4'b1000:out=8'b10000000;

4'b1001:out=8'b10010000;

4'b1010:out=8'b10001000;

4'b1011:out=8'b10000011;

4'b1100:out=8'b11000110;

4'b1101:out=8'b10100001;

4'b1110:out=8'b10000110;

4'b1111:out=8'b11001110;

endcase

end

endmodule