【 1. 时序逻辑电路 】

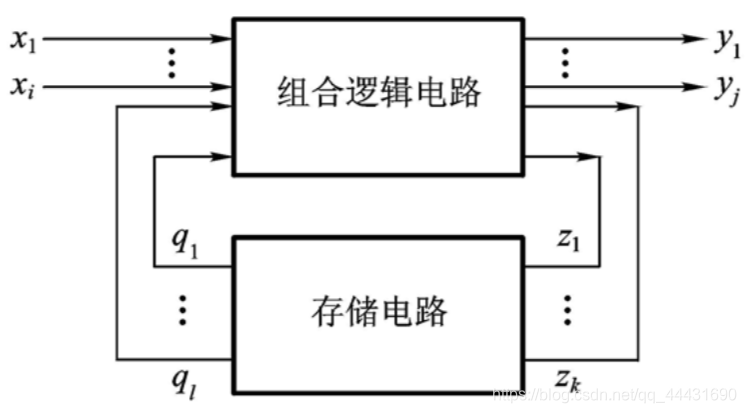

任一时刻的输出不仅取决于该时刻的输入,还与电路原来的状态有关。

同步时序电路

存储电路中所有触发器的时钟使用统一的CLK,状态变化发生在同一刻。

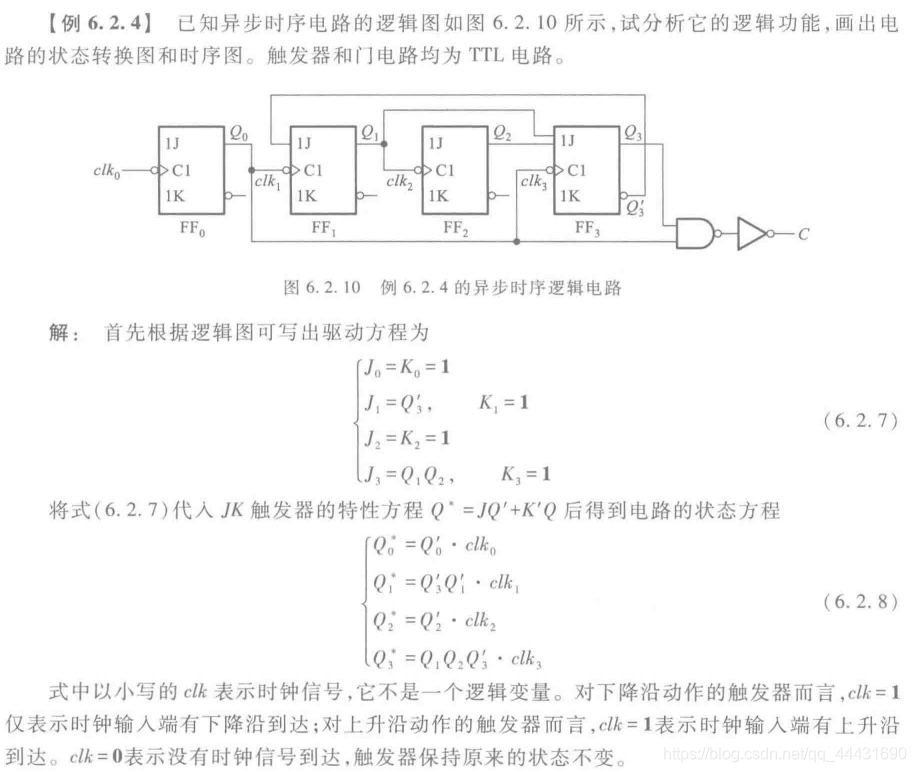

异步时序电路

没有统一的CLK,触发器状态的变化有先有后。

Mealy型

Moore型

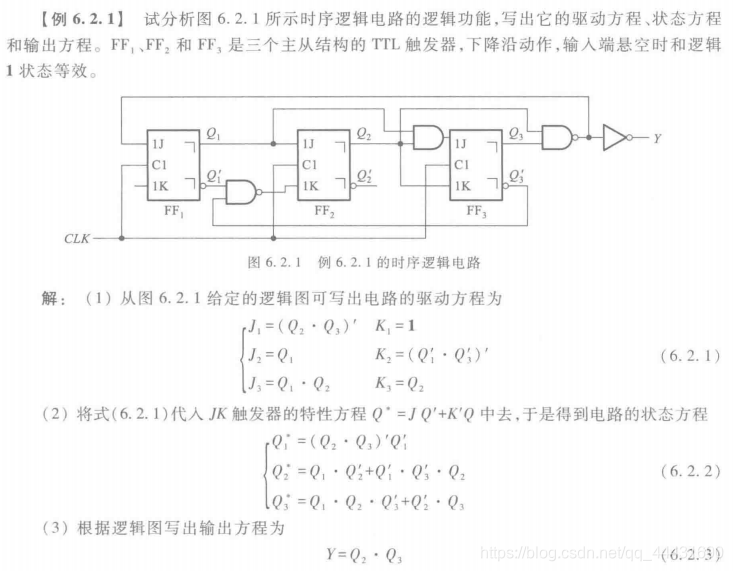

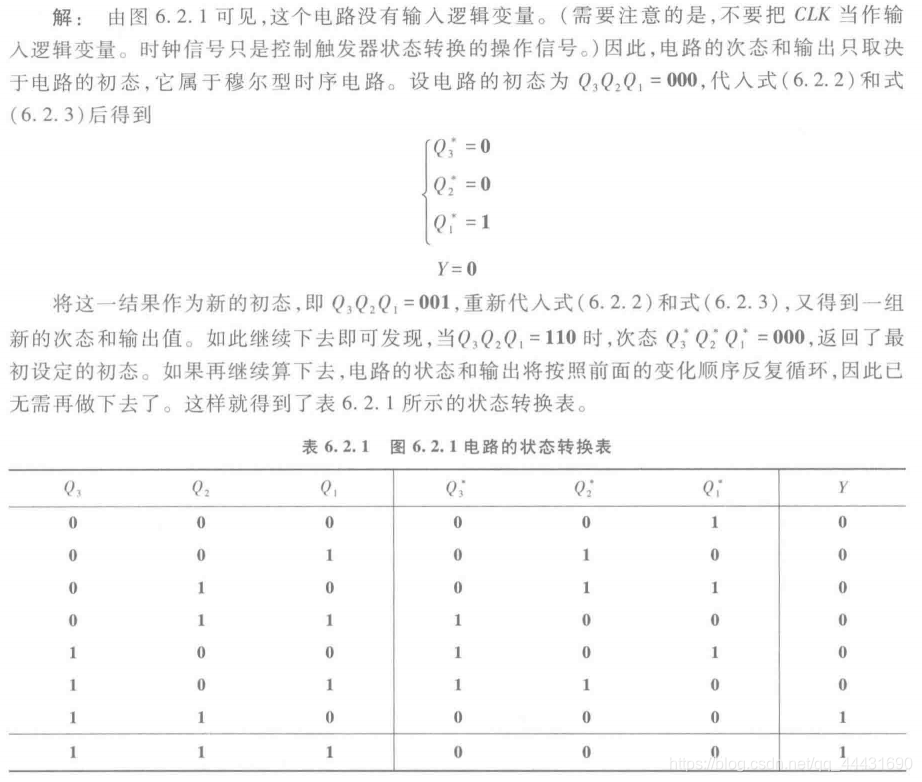

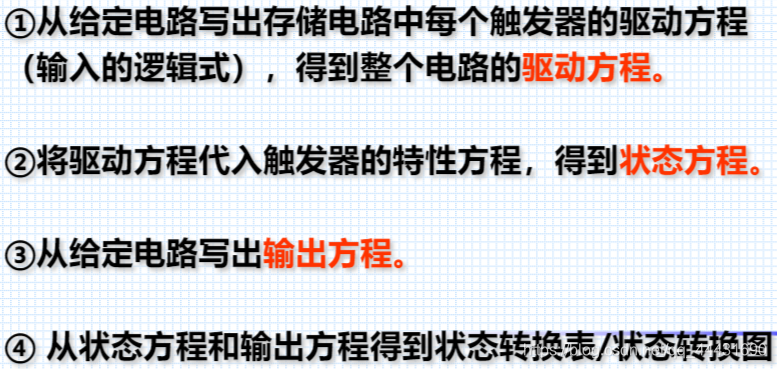

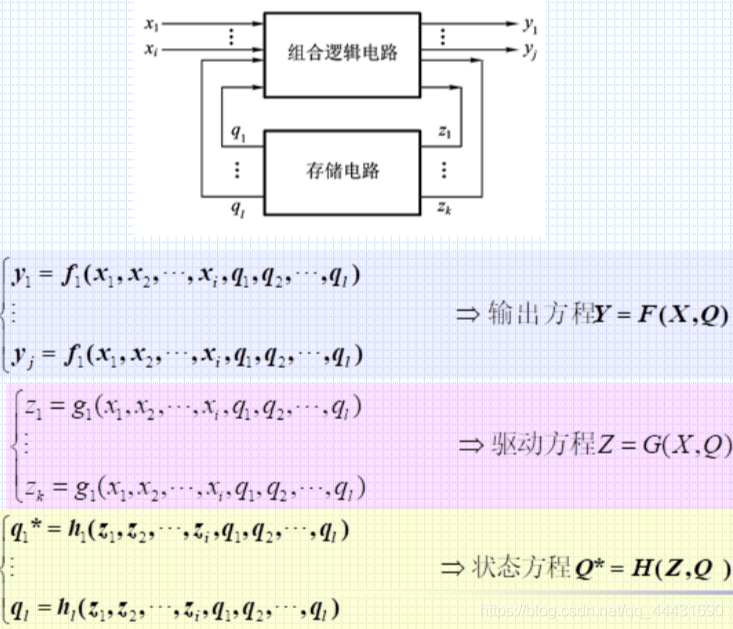

【 2. 同步时序电路的分析 】

找出给定时序电路的逻辑功能。即找出输入和CLK作用下,电路的次态和输出。

【 3. 功能描述 】

①

②

③

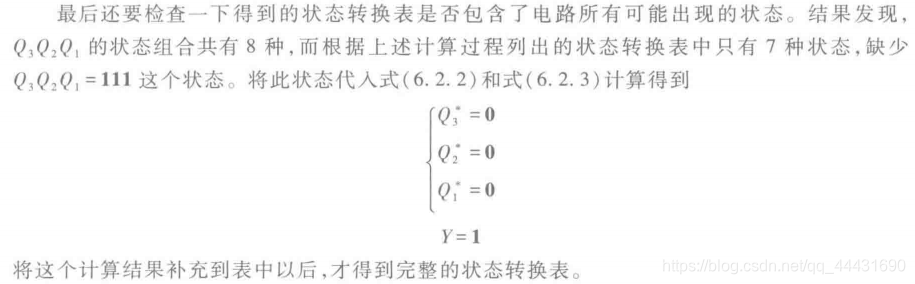

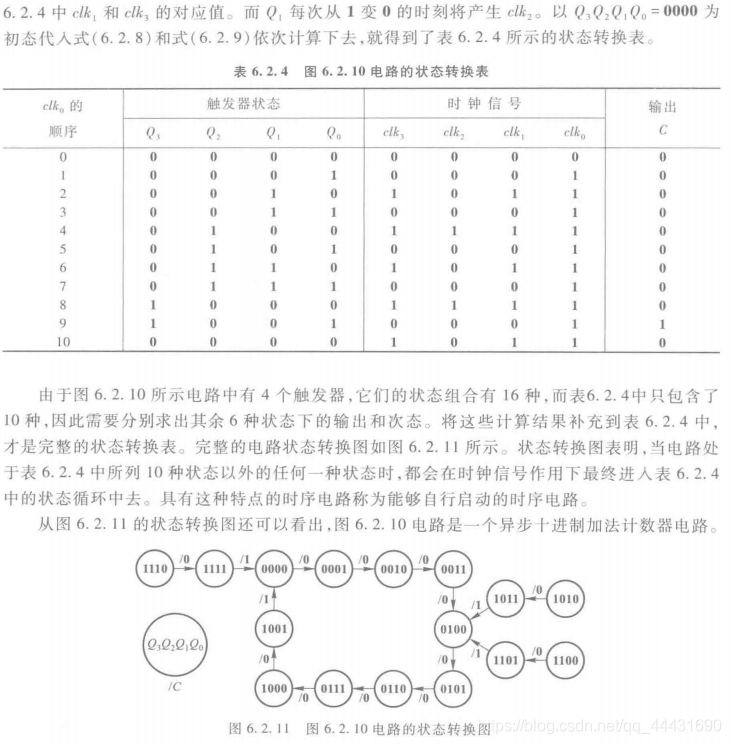

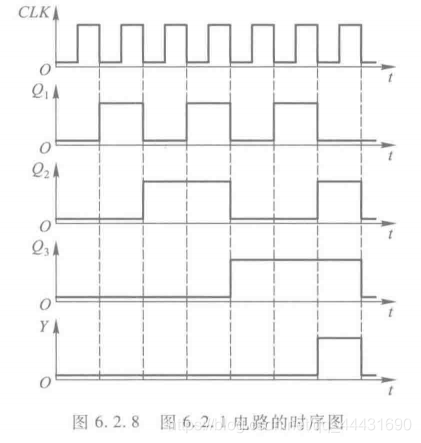

当电路进入任何无效状态,都能在时钟信号的作用下,自动返回有效循环中。

检查自启动方法:

- 检查状态转换图,找出无效状态:如题中Q1、Q2、Q3有8种组合,循环中只有7种,则存在无效状态111。

- 将无效状态代入输出方程和状态方程,若结果返回有效状态,则能够自启动。

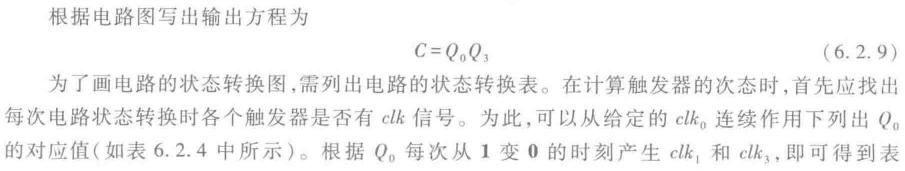

【 4. 异步时序电路的分析 】

异步时序逻辑电路中,每次电路状态发生转换时并不是所有触发器都有时钟信号,只有那些有时钟信号的触发器才需要用特性方程去计算次态,而没有时钟信号的触发器将保持原来的状态不变。