文章目录

一、在线Verilog编程网站学习

网站地址:Wire

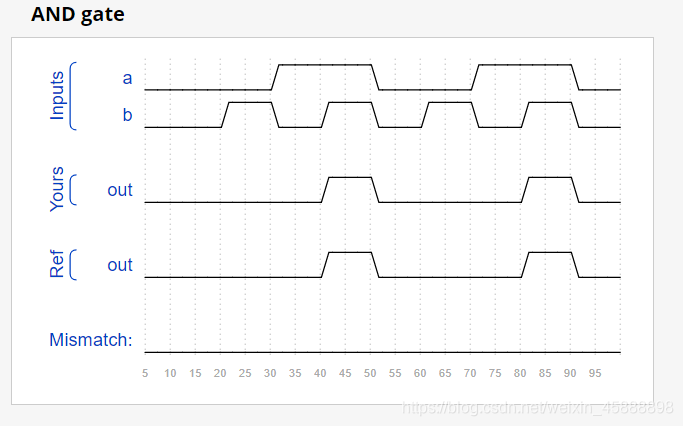

一、门电路

一、选择与门

编写代码

module top_module(

input a,

input b,

output out );

assign out=a&b;

endmodule

运行结果

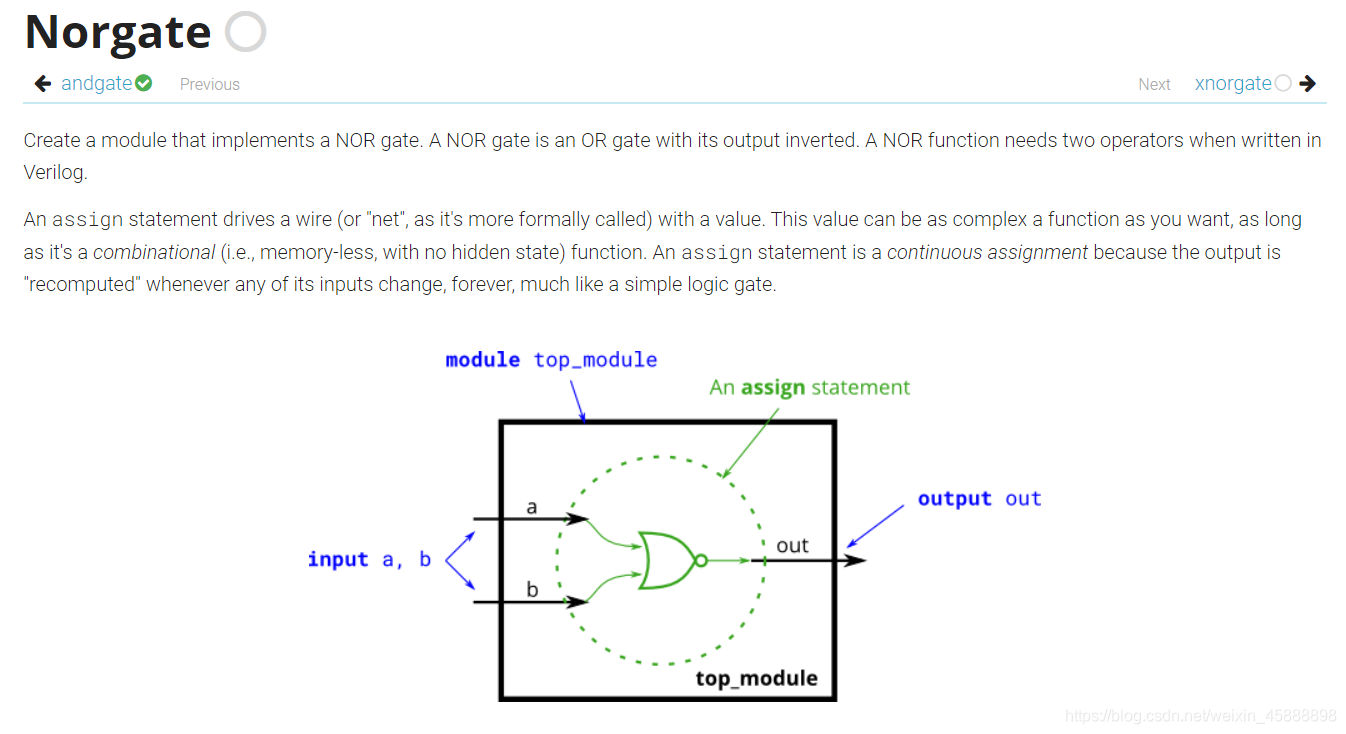

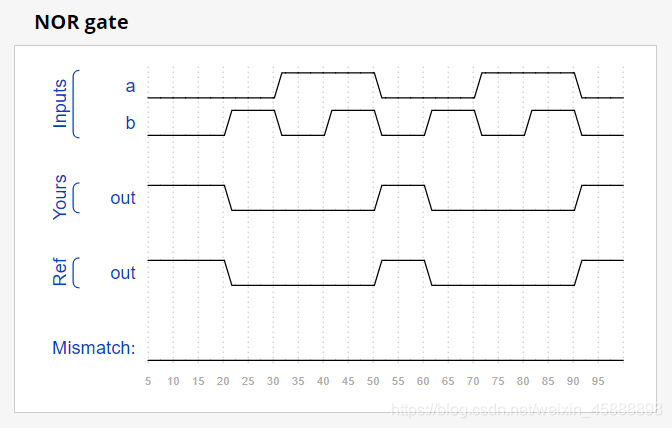

二、或非门

编写代码

module top_module(

input a,

input b,

output out );

assign out=!(a||b);

endmodule

运行结果

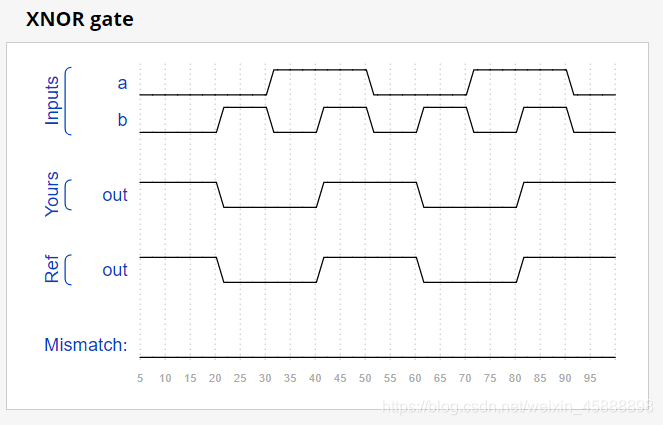

三、同或门

编写代码

module top_module(

input a,

input b,

output out );

assign out= !((!a & b) | (a & !b));

endmodule

运行结果

二、组合电路

一、半加器

半加器是实现两个一位二进制数加法运算的器件。它具有两个输入端(被加数A和加数B)及输出端Y(含和数S和进位数C)

编写代码

module top_module(

input a, b,

output cout, sum );

assign cout=a&b;

assign sum=a^b;

endmodule

运行结果

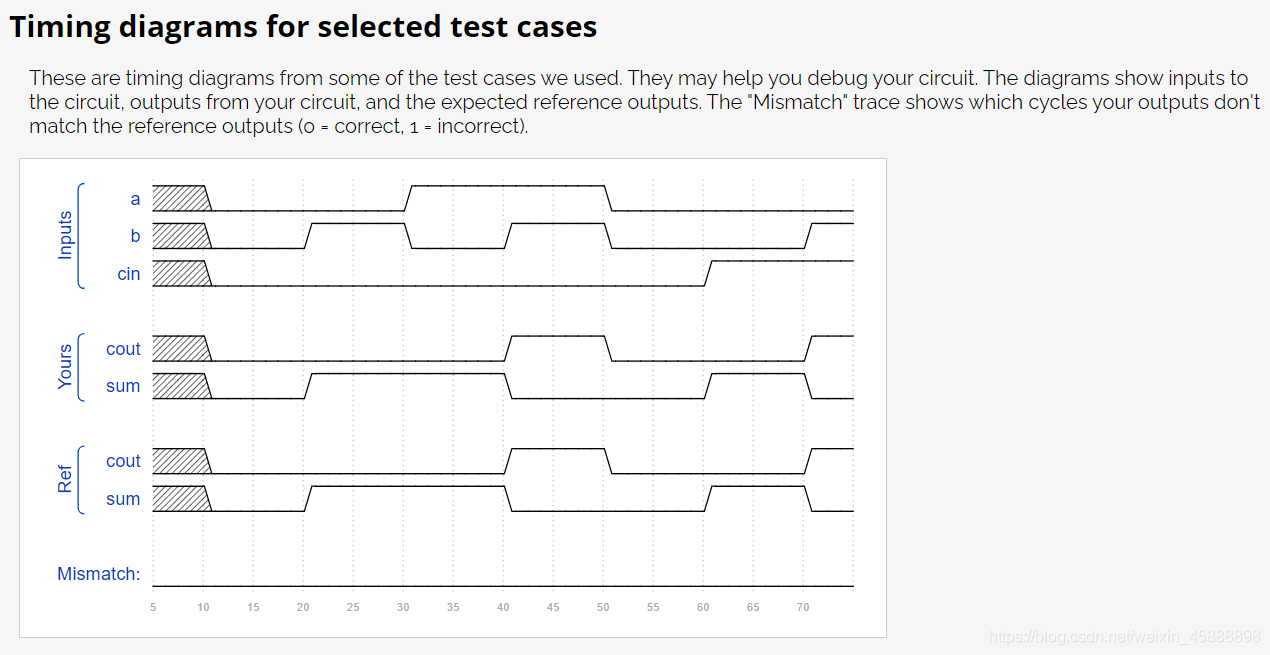

二、全加器

全加器是用门电路实现两个二进制数相加并求出和的组合线路,一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器

编写代码

module top_module(

input a, b, cin,

output cout, sum );

assign sum = a^b^cin;

assign cout = (a&b)|(a&cin)|(b&cin);

endmodule

运行结果

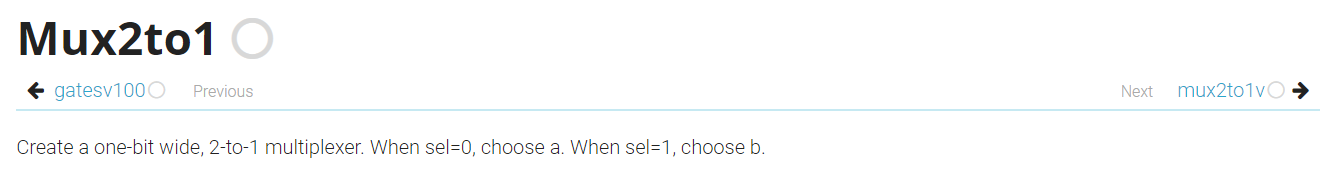

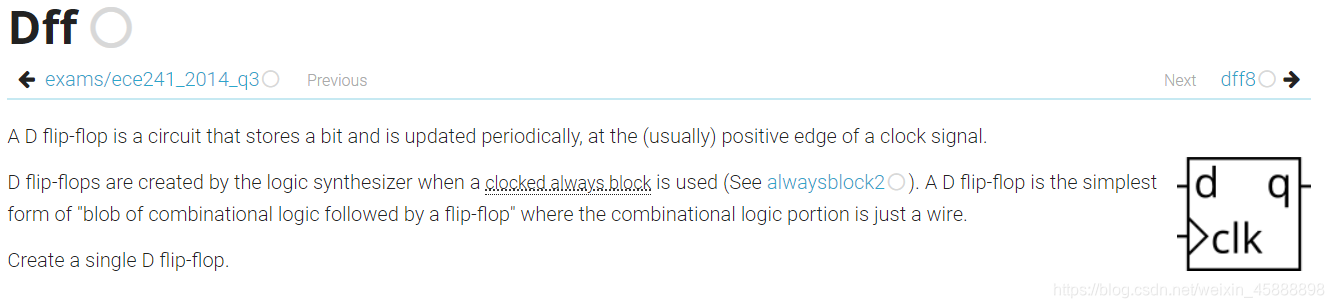

三、2选1多路复用器

编写代码

module top_module(

input a, b, sel,

output out );

assign out=(sel)?b:a;

endmodule

运行结果

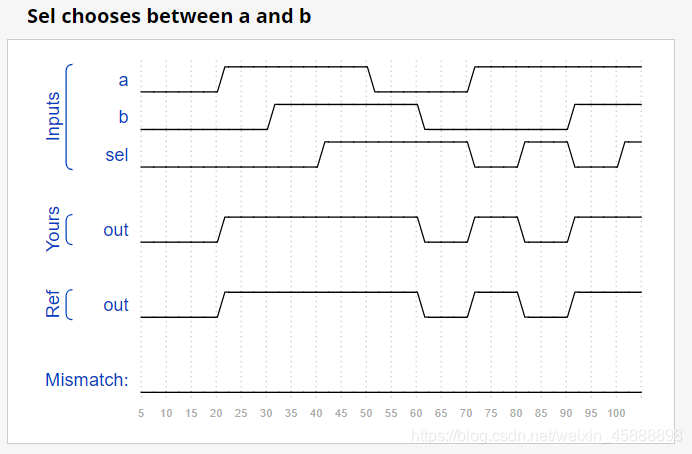

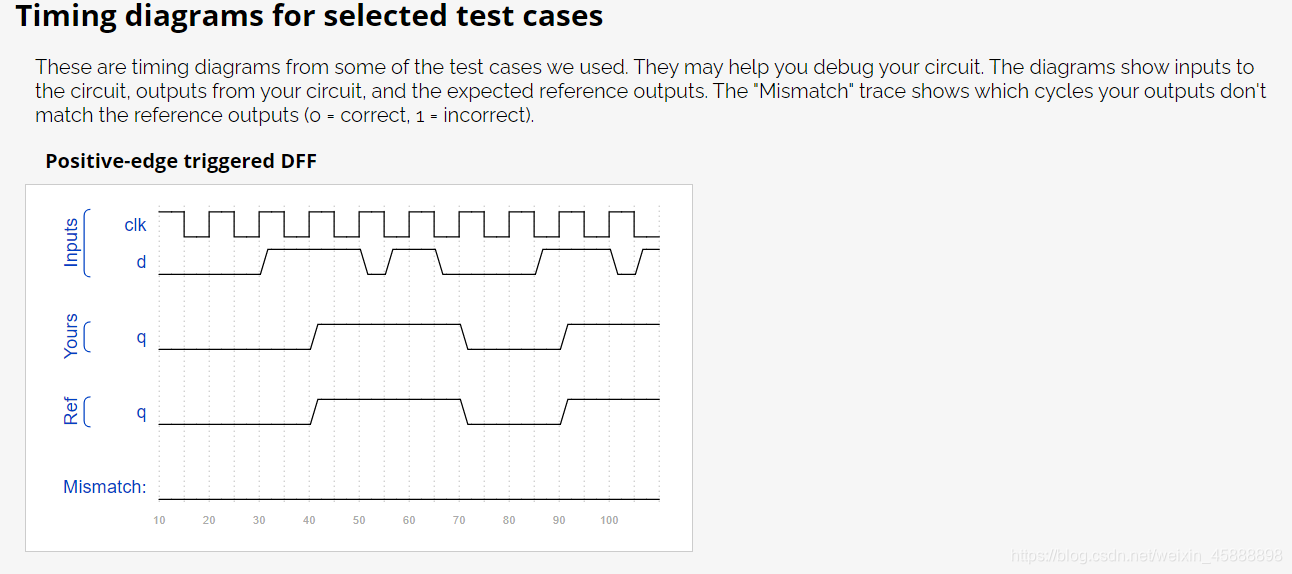

三、时序电路

一、D触发器

编写代码

module top_module (

input clk, // Clocks are used in sequential circuits

input d,

output reg q );//

// Use a clocked always block

// copy d to q at every positive edge of clk

// Clocked always blocks should use non-blocking assignments

always@(posedge clk) begin

q <= d;

end

endmodule

运行结果

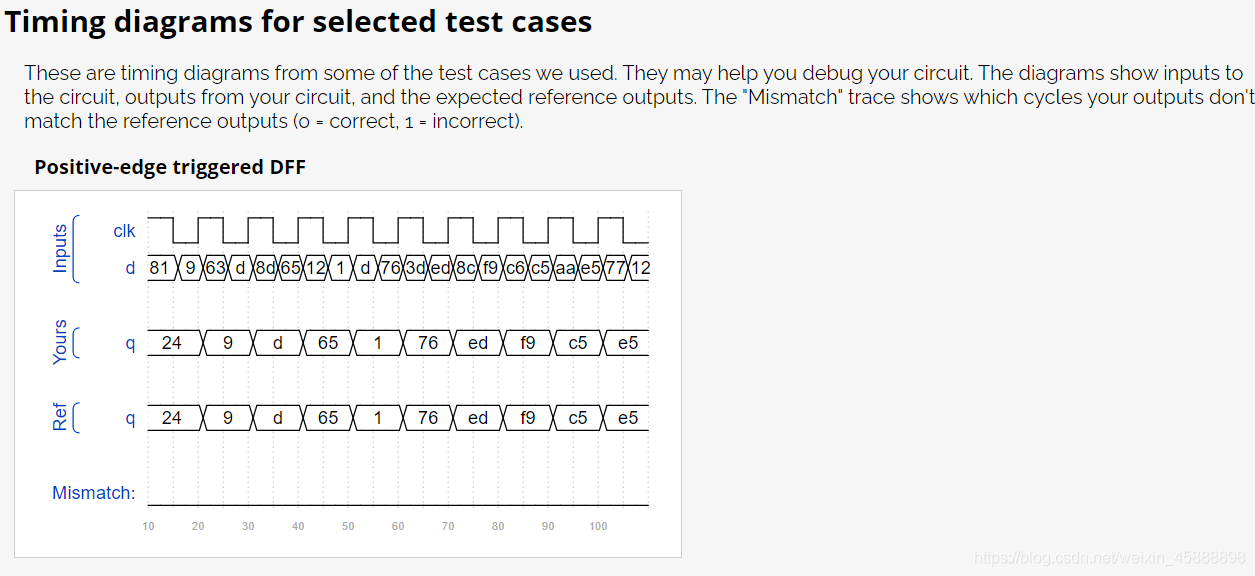

二、8位D触发器

编写代码

module top_module (

input clk,

input [7:0] d,

output [7:0] q

);

always@(posedge clk) begin

q <= d;

end

endmodule

运行结果

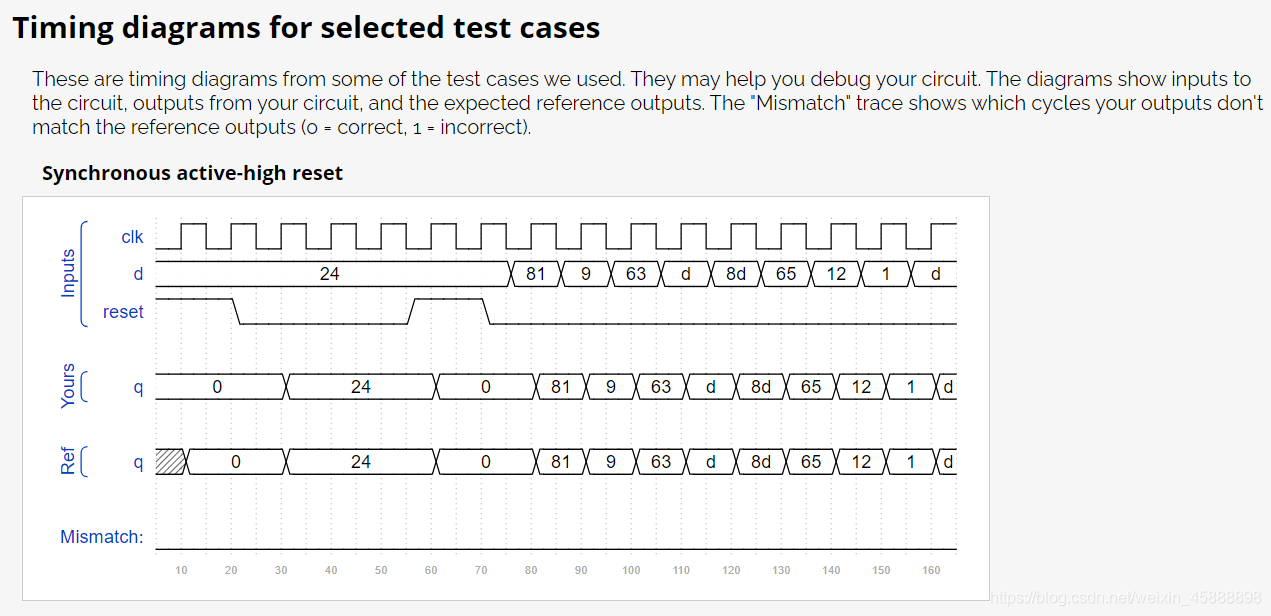

三、带复位按钮的D触发器

编写代码

module top_module (

input clk,

input reset, // Synchronous reset

input [7:0] d,

output [7:0] q

);

always@(posedge clk) begin

if(reset)

q <= 8'b0;

else

q <= d;

end

endmodule

运行结果