PS:本系列参考夏宇闻老师的Verilog数字系统设计jiao教程,意在对verilog形成基础的体系,留作将来查询参考,请大家多指教。

硬件描述语言(HDL,hardware description language)是一种形式化方法来描述数字电路和系统的语言。数字电路系统的设计者利用这种语言可以从上层到下层(从抽象到具体)逐层描述自己的设计思想用一系列分层次的模块来表示极其复杂的数字系统。然后利用EDA工具逐层进行仿真验证,再把其中需要变为具体物理电路的模块组合经由自动综合工具转换到门级电路网表。接下去再用专用集成电路(ASIC)或现场可编程门阵列(FPGA)自动布局布线把网表转换为具体电路布线结构的实现。在制成物理器件之前,还可以用Verilog的门级模型来代替具体基本元件。

verilog HDL 是硬件描述语言的一种,用于数字电子系统设计。该语言允许设计者进行各种级别的逻辑设计,进行数字逻辑系统的仿真验证、时序分析、逻辑综合。

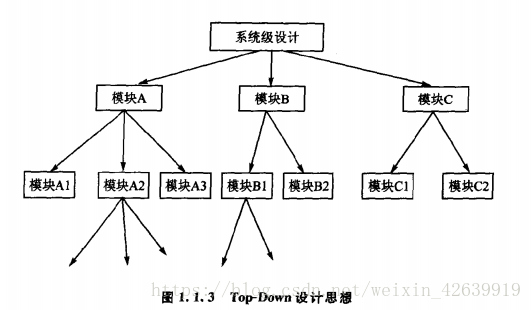

自顶向下设计的基本概念

自顶向下的设计是从系统级开始 ,把系统划分为若干个基本单元,然后再把每个基本单元划分为下一层次 的基本单元,一直这样做下去 ,直到可以直接用 EDA 元件库中的基本元件来实现为止 。

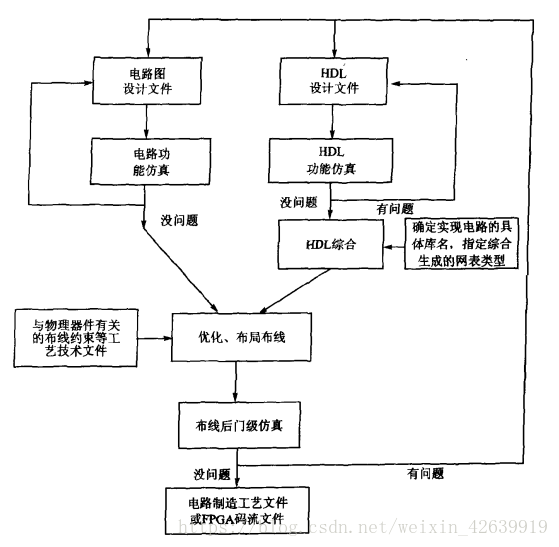

HDL设计流程图

电路设计步骤

1、设计输入:原理图输入或者硬件描述语言输入

2、综合:将行为级或者RTL级等设计输入 转化成 由基本逻辑单元组成的逻辑连接,并将RTL级文件映射到FPGA的原语,生成综合的网表文件。(RTL级,描述数据在寄存器之间的流动和如何处理、控制这些数据流动的模型)。

3、实现:将综合产生的网表文件 转化成 所选器件的底层模块和硬件原语。

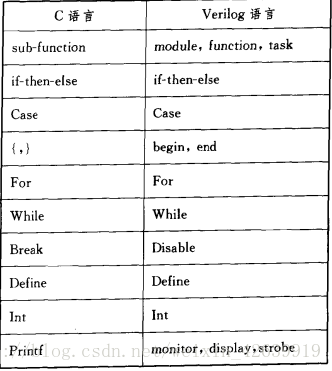

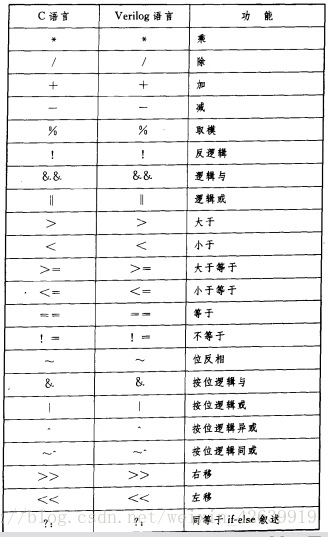

C语言与verilog的比较

1、C 程 序 是 一 行接 一 行依次执行 的,属 于顺 序 结构 ,而 Veri log 描述 的硬件 是 可 以在 同 一 时 间 同 时运行的 ,属 于并行结构 。

2、Verilog 可 用 的输 出 输入 函数很少 ,C 语 言 的花 样则很 多

3、C 程 序 调 用 函 数 是 没 有延 时特性 的 ,一 个 函数是惟 一 确 定 的 ,对 同一 个 函 数 的 不 同调 用 是 一 样 的 。而 Verilog 中对模 块 的不 同调 用 是不 同 的 ,即使调 用 的是 同一 个模块 ,必 须 用 不 同 的名 字 来指定 。

4、Ver ilog 的语 法 规则很死 ,限 制 很 多 ,能 用 的判 断语 句 有 限 。仿 真速度较 慢 ,查错 功 能 差 ,错 误信 息 不 完 整 。仿 真 软 件 通 常 也很 昂贵 ,而 且 不 一 定可 靠 。C 语 言没 有 时 间 关 系 ,转 换后 的 Verilog 程 序 必须做到 没 有任 何 外加 的人工延 时信 号 ,也 就 是 必须表达 为 有 限状 态 机 ,即 RTL 级 的 Verilog,否 则将 无 法 使用 综 合 工具把 Verilog 源 代 码 转 化 为 门级逻辑 。

5、关键字和运算符比较

verilog HDL 与VDHL的比较

VHDL 的英文全名 为 VHSIC Hardware Description Language ,而 VHSIC 则是 Very High Speed lntegerated Circuit 的缩写词,意为甚高速集成 电路,故 VHDL 其准确的中文译名 为甚高速集成 电路的硬件描述 语言。

Verilog HDL 和 VHDL 作为描述硬件 电路设计的语言,其共同的特点在于:

1、 能形式化地抽象表示电路的行为和结掏;

2、支持逻辑设计中层次与范圄的描述;

3、可借用高级语言的精巧结掏 来简化电路行为的描述 ;

4、具有电路仿真与验证机制以保证设计的正确性 ;

5、 支持电路描述由高层 到低层的综合转换;

6、 硬件描述与实现工艺无 关(有关工艺参数可 通过语言提供的 属性包括进去);

7、便于文档管理;易于理解和设计重用。

但是 Verilog HDL 和 VHDL 又各有其 自己的特点。

与 VHDL相比 ,Verilog HDL 的最大优点为 :它是一种非常容易掌握的硬件描述语言 ,只要有 C 语言的编程基础 ,通过 20 学时的学习,再经过一段时间的实际操作 , 一般可在 2、3个月内掌握这种设计技术。而掌握 VHDL 设计技术就比较困难 。

一般认为 Verilog HDL 在系统级抽象方面比VHDL 略差些 ,而在门级开关电路描述方面比VHDL 强得多。

verilog语法的基本概念

Verilog HDL 是一种用于数字系统设计的语言。用其描述的电路设计就是该电路的 Verilog HDL 模型,也称为模块 。Verilog HDL 既是一种行为描述的语言也是一种结构描述的语言。这就是说 ,无论描述电路功能行为 的模块或描述元器件或较大部件互连 的 模块都可以用 Verilog 语言来建立电路模型。

Verilog 模型可以是实际电路的不同级 别的抽象。这些抽象的级别和它们所对应的模型类 型共有以下5种,现分别给以简述 。

( 1) 系统级( system-level) :用语言提供的高级结构能够实现所设计模块的外部性能的模型。

( 2) 算法级( algorithm level) :用语言提供的高级结构能够实现算法运 行的模型 。

( 3 ) RTL 级(register transfer level) :描述数据在寄存器之间 的流动和如何处理 、控制这 些数据流动的模型 。

以上三种都属于行为描述 ,只有 RTL 级才与逻辑 电路有明确的对应关系 。

( 4 ) 门 级( gate-level ) :描述逻辑门以及逻辑门之间连接的模型 。

与逻辑电路有确定的连接关系 ,以上四种数字系统设计工程师必须掌握。

( 5) 开关级( switch-level ):描述器件中三极管和储存节点以及它们之间连接的模型 。

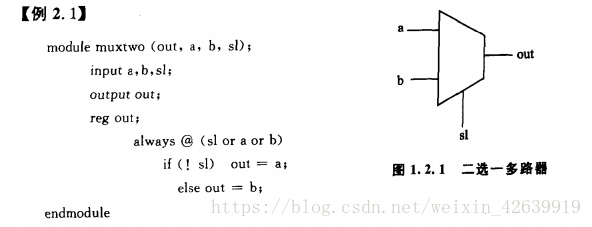

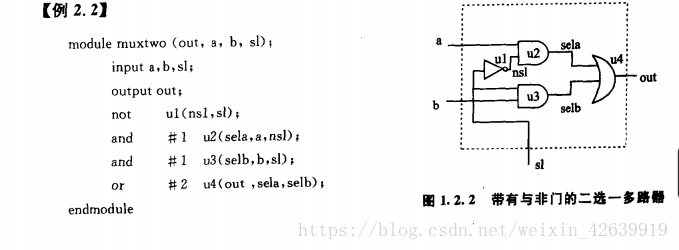

通过计算机上运行的工具进行从例2.1转换为例2.2形式的模块,这个过程就是综合

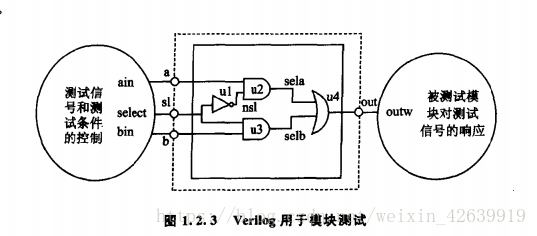

verilog用于模块的测试

Verilog 还可以用来描述变化的测试信号 。描述测试信号的变化和测试过 程的模块叫做 测试平台(testbench 或 testfixture),它可以对上面介绍的电路模块 (无论是行为的或 结构 的〉进行动态的全面测试 。

下面是对例2.1多路选择器的全面测试

'include "muxtwo.v"

module t;

reg ain,bin,select;

reg clock;

wire outw;

initial //把寄存器变量初始化为一确定的值

begin

ain=0;

bin=0;

select=0;

clock=0;

end

always #50 clock=~clock ;//产生一个不断重复的周期为100个的时钟信号clock

always@(posedge clock)

begin

#1 ain={$ random}%2;//{$ random}为系统任务,会产生一个随机数

#3 bin={$ random}%2;//分别延迟1和3个时间单位后产生随机的位信号流ain和bin

end

always #10000 select=! select;//产生周期为10000个单位时间的选通信号变化

muxtwo m(

.out(outw),

.a(ain),

.b(bin),

.sl(select)

);

/*“.”表示端口;后面紧跟端口名,其名称必须与muxtwo模块定义的端口名一致;

小括号内的信号名为与该端口连接的信号线名,可以用别的名,但必须在本模块中定义,说明其类型。*/

endmodule