设计一个2位十进制的循环计数器,从0到99,然后再回到0.输出为out0和out1,分别表示十进制数的高位和低位。

设计代码

`timescale 1ns / 1ps

module Test1030(clk,rst,out0,out1,data);

input clk;

input rst;

output [3:0] out0;

output [3:0] out1;

output [7:0] data;

reg [3:0] out0;

reg [3:0] out1;

wire [7:0] data;

always @(posedge clk or negedge rst)

if(!rst)

begin

out0=0;

out1=0;

end

else

begin

if(out0= =9)

begin

out0<=0;

out1=out1+1;

end

else

out0<=out0+1;

if(out1==10)

out1<=0;

else

out1=out1;

end

assign data=(10*(out1))+out0;

endmodule

测试代码

`timescale 1ns / 1ps

module Test1049;

reg clk;

reg rst;

wire [3:0] out0;

wire [3:0] out1;

wire [7:0] data;

always begin

#10 clk=0;

#10 clk=1;

end

initial begin

clk=0;

rst=0;

#100;

rst=1;

end

Test1030 x1(.clk (clk ),

.rst (rst ),

.out0(out0),

.out1(out1),

.data(data));

endmodule

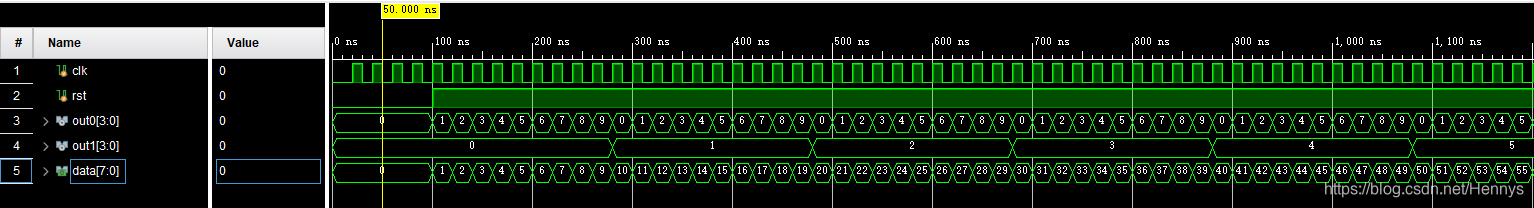

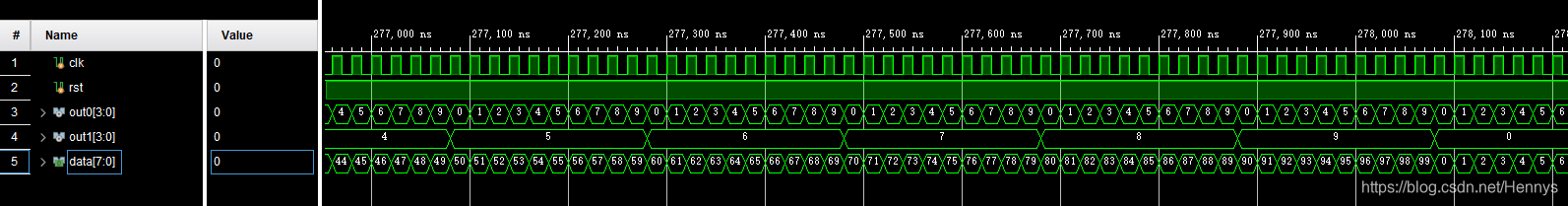

仿真波形

out0为低位输出,out1为高位输出,data将两个参数综合后输出两位十进制的数。