目录

(3)Intel 2114 RAM 矩阵 (64 × 64) 读

(4)Intel 2114 RAM 矩阵 (64 × 64) 写

(5)单管动态 RAM 4116 (16K × 1位) 芯片 读

(6)单管动态 RAM 4116 (16K × 1位) 芯片 写

一、主存储器——半导体存储芯片

1、半导体存储芯片的基本机构

读写控制线:将CPU的控制信号传给读写电路

地址线:将CPU需要的地址传输到译码驱动中,然后由译码驱动进行翻译,然后进行寻址,是单向的

地址线的数量决定了存储单元的数量,假如有8根地址线:0000 0000 总共有几种排列组合,即2的8次方。每一种组合都对应一个存储单元。

数据线:将存储体中的数据读出,放入CPU;将CPU计算完毕的数据存入存储体。是双向的。

数据线的数量决定了存储单元的大小,即一个存储单元能够存多少数据。比如八根数据线0000 0000, 进行一次读取的方式。

片选线:一个半导体存储器是有多个芯片构成的,所以在调用一个存储器中的具体的存储单元时,确定是哪一个芯片

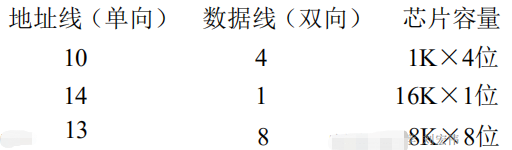

(1)计算芯片的容量

芯片容量 = 地址线的寻址能力 * 数据线的数量 = 存储单元的数量 * 每一个存储单元的容量

如下所示,根据地址线和数据线计算芯片的容量:2^10*4=1K*4...

(2)存储芯片片选线的作用

片选线的作用:让某一个芯片或者某些芯片同时进行工作

扩充存储单元容量:如图,16K x 1位的芯片,总共有16K个存储单元,每一个存储单元有1位。若要存储八位数据,将八个存储单元进行并联,每一个存储芯片存储八位数据中的一位。每一次读取数据都同时读取八位芯片地一位,统一输出就是八位。

增加存储单元的的总数:以扩容完毕的八个一组的存储芯片为一组,成组地进行扩展,增加整体地存储器地存储单元地个数。

地址分配:按照前后顺序,第一组从0到(16K -1),第二组从16K到(32K - 1),第三组从32K到(48K - 1),第四组从48K到(64K - 1)。当地址为 65 535 时,第四组的 8 片的片选有效。

2、半导体存储芯片的译码驱动方式

(1)线选法

线选法:K位地址码经过译码,得到2^K根地址线,每根地址线对应一个存储单元。

在线选法中,地址码只需进行一次译码就可选择存储单元,其地址码位数越长,译码器结构越复杂,成本越高,故该寻址方式适合在速度较快、容量较小的存储芯片中使用。

如图所示,总共有4根地址线,通过译码器导出,每一种排列组合都对应一根寻址线,2的四次方总共有16根寻址线,输入对应的地址,直接输出存储单元中的数据。

问题:如果存储单元的数量很多,有16根地址线,那么对应就有2^16次方根数据线,增大了存储器的体积,降低了集成度

(2)重合法

重合法:将线选法中单一的地址译码器分成了行地址译码器和列地址译码器,通过两者互“与”来选中存储单元,大大简化了外部译码线路,主要用于大容量的存储器结构,能有效的提高芯片的集成度。

将原先的线性排列方式,改为二维排列的方式。

将8根数据线分为两组,每组四根地址线,每组十六根寻址线。两组分别是X地址和Y地址,确定一个存储单元,要分别要有X地址和Y地址。

读数据方式:

输入地址0000 0000,X地址对应的X0保持高电位,对应行的所有存储单元全部找到,并向外输出,但是到达底部时,对应列的开关没有打开,无法传输。Y地址对应的Y0保持高电位,对应列的传输开关打开,数据通过开关传输。通过X地址和Y地址两方面联合确定存储单元的位置,进行输出。

二、主存储器——随机存取存储器

随机存取存储器(英语:Random Access Memory,缩写:RAM),也叫主存,是与CPU直接交换数据的内部存储器。它可以随时读写(刷新时除外),而且速度很快,通常作为操作系统或其他正在运行中的程序的临时数据存储介质。RAM工作时可以随时从任何一个指定的地址写入(存入)或读出(取出)信息。它与ROM的最大区别是数据的易失性,即一旦断电所存储的数据将随之丢失。RAM在计算机和数字系统中用来暂时存储程序、数据和中间结果。

1、静态RAM(SRAM)

(1)静态 RAM 基本电路

存储0和1信号的方式:静态RAM保存的0和1的原理就是使用触发器。T1~T4为4根管子构成的双稳态触发器,不易丢失或者是损耗,它在两端存储信息,左端保持输入信号的非,右端保存原输入信号。

移码驱动方式:重合法——分别通过行地址和列地址的联合选中才能输出,每一份存储单元都对应一个行列地址坐标(行地址X,列地址Y)。

T5和T6是行地址选择开关:当接通的时候,对应的信号可以通过两端分别经过行选择开关输出到列选择开关终止。

T7和T8是列地址选择开关:当开关接通时,允许数据从双稳态触发器两端输出,经过行地址选择器,再通过列地址选择器,实现最终的输出。只有行、列被选中的某个单元存储电路,在其行列通门同时被打开时,才能进行读出信息和写入信息的操作。

读写开关,通过输入对应的读写控制信号选择是否打开,通过数据。

总结:一个SRAM的基本单元需要由8个电路基本元件构成

静态RAM的基本读操作

静态RAM的基本写操作

(2)静态 RAM 芯片——Intel 2114

在Intel 2114芯片中,WE为写允许信号,其中低电平为写,高电平为读。CS为片选信号,只有CS信号是低电平的时候Intel 2114芯片才会选中,芯片左侧A0-A9是10条地址线,可以看出芯片是1K的存储,右侧是4根数据线,可以读出和写入4位信号,因此可以看出,芯片的存储容量为1K X 4位 。

(3)Intel 2114 RAM 矩阵 (64 × 64) 读

(4)Intel 2114 RAM 矩阵 (64 × 64) 写

Intel 2114 RAM 矩阵的写跟读基本上是一致的,只是WE被换成了写信号(低电平),从I/O数据线写入数据

2、动态RAM(DRAM)

动态RAM保存0和1的方法是电容,当电容保存电荷时为1,不保存电荷(没充电)时为0;

常见的动态RAM基本单元电路有三管式和单管式两种,他们共同的特点是靠电容存储电荷的原理来寄存信息。

(1)三管式动态RAM电源电路

信息读出

如果预充电信号有效,T4开关打开,V(DD)进行充电,会对读数据线进行充电,读数据线有效(变成高电平,表示为1),如果进行读出,读选择线有效,T2开关被打开。

如果C(g)当中没有保存有电容(存储0),那么T1开关为低电平(表示为0),T1开关不会被打通,读数据线仍然保持高电平,读出的数据为1;如果C(g)电容当中保存有电荷(存储为1),那么T1开关为高电平(表示为1),此时T1和T2开关同时放电,使得读数据线由高电平变成了低电平(表示为0),由这个过程,我们可以看出读出的信息和原存的信息是相反的。

信息写入

如果进行写入,写选择线有效,T3开关被打开,写数据线会通过T3开关向C(g)进行充电或者放电。如果写选择线是高电平,那么写入的信号就是高电平,同样,如果写选择线是低电平,写入的便是低电平。因此写入与输入信息相同。

(2)三管动态 RAM 芯片 (Intel 1103) 读

三管动态 RAM 芯片 (Intel 1103) 一共有A0~A9 10个 地址线,因此芯片的存储容量为1K; 每次读出和写入都为一位信号,因此是1K x 1位容量的芯片。行地址经过译码后,每一行都对应了两个控制信号,一个是读选择信号和一个是写选择信号,读和写分别使用不同的信号进行控制。如图,是对第0行第0列的地址进行读数据的电路图,第0行第0列的数据经过读控制线进入到读写控制电路进行输出。

刷新放大器:使用电容存储电荷的原理表示0和1时,电容会漏电,一段时间后,电容里边的信号会消失,因此需要定期使用刷新放大器对电容信号进行重写。

(3)三管动态 RAM 芯片 (Intel 1103) 写

写入信号,如果行地址为11111,即行地址为31,那么第31行全部被选中,所有的写选择线有效,给出列地址为00001,那么第31行的第一列的原件为我们需要写入数据的操作原元件。数据通过D端进行输入,经过读写控制电路,通过写数据线被写入到指定原件的位置。

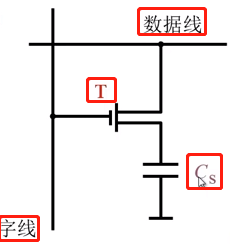

(4)单管动态RAM电源电路

读出:C(s)当中如果保存了电荷(表示1),那么数据线读出就是高电平。

写入:单管动态RAM中字线是控制线,如果字线充电,T开关被打开,C(s)可以进行充电或者放电。

单管动态 RAM 4116 (16K × 1位)外部特性

单管动态 RAM 4116 (16K × 1位)的7位行地址和列地址分两次传送,第一次传送7位行地址,保存在行地址缓存器当中,第二次传送列地址,保存在列地址缓存器当中;行地址和列地址分别经过行译码和列译码以后,选中给定的存储单元进行输入和输出。

I/O缓存器,缓存了输入和输出数据,连接I/O缓存器两端的数据输入和输出寄存器可以控制数据的输入和输出。

时序与控制:由行选中信号RAS、列选中信号CAS和读写信号WE组成,分别生成了行时钟、列时钟和写时钟,控制了芯片内部的读和写操作。

(5)单管动态 RAM 4116 (16K × 1位) 芯片 读

下图是单管动态 RAM 4116 (16K × 1位) 芯片读图示,注意:其中横线电路为列选择信号,竖线电路为行选择信号。

RAM 4116芯片中的读放大器的工作原理为跷跷板电路,其左右两侧电平相反。

如果行地址给出的是0111111(一个0,6个1),那么第63行被选中;然后给出列地址为7个0,那么第0列将被选中,第0列的列选信号有效,对应开关被打开。数据就会经过读放大器的右侧(0变成1),经过列选开关,送入到读/写线上,然后经过I/O缓冲,通过输出驱动送出来。

(6)单管动态 RAM 4116 (16K × 1位) 芯片 写

下图是单管动态 RAM 4116 (16K × 1位) 芯片写图示,跟读数据的逻辑基本一致,数据经过读放大器时(1变成0),读出时(0变成1),经过两次反向,使得读写数据保持正确。

3、动态RAM刷新

电容存储电荷的原理表示0和1时,电容会漏电,一段时间后,电容里边的信号会消失,因此需要定期进行动态RAM刷新完成对电容信号的重写。

动态RAM刷新只跟行地址有关,跟列地址无关。每次刷新的都是一行的数据,而不是某一个存储单元的数据。

(1)集中刷新

所谓集中是刷新就是把刷新时间集中在一起进行操作,如图,动态RAM在2ms内对128行进行集中式刷新,2ms内一共式4000个存储周期,前3872个周期可以供CPU或者I/O进行读写操作,后128个周期专用于进行集中式刷新,这段时间内CPU或者I/O都不可以与动态RAM进行数据信息交换,因此这段时间也被称为死区。以下便是死区比重的计算结果

(2)分散刷新

分散式刷新就是把刷新时间分散放在一个读写周期内,如图,T(c)为一个读写周期,t(M)为数据的读写操作,t(R)为刷新操作。分散刷新实际上把原来的读写周期时间进行了延长,使得芯片的刷新频率上升,芯片性能下降。唯一的优点是,分散刷新没有死区。

(3)分散刷新与集中刷新相结合(异步刷新)

在2ms的周期内,芯片的总刷新行数为128行,因此,我们把这个时间分成128份,芯片每隔15.6us(微秒)就需要刷新一行。在15.6us时间内,刷新时间可以放在任何一个周期上,因此相当于一个集中式刷新的方式,而相对于整个时间周期2ms来说,这种方式又是一种分散式刷新。

4、动态RAM和静态RAM的比较

(1)动态RAM的单元电路由一个晶体管和一个电容构成,总体比较简单;静态RAM比较复杂,每一个单元单路包含6个晶体管,所以集成度比较低。

(2)从芯片引脚上来说,动态RAM行地址和列地址可以分别进行传送,节约了引脚数量,减少了封装体积。但是,动态RAM行地址和列地址分别进行传送时,消耗了执行时间。

(3)动态RAM只是对电容进行充电、放电和刷新,因此功耗比较低,而静态RAM需要由6条晶体管协同工作,晶体管进行工作时需要保持通电,因此所需功耗比较大。

(4)动态RAM对电容进行充电需要消耗时间,比静态RAM使用触发器的工作原理速度要慢。

因此,根据动态RAM和静态RAM的特点,我们一般选择动态RAM作为主存,静态RAM作为缓存(加快速度)。