半导体存储器的读写时间一般在十几至几百毫微秒之间,其芯片集成度高,体积小,片内含有译码器和寄存器等电路。常用的半导体存储器芯片有多字一位片和多字多位片,如16M位容量的芯片可以有16M×1位和4M×4位等种类。

一、存储容量的扩展

目前单片存储芯片的容量总是有限的,它在字数或字长方面与实际存储器的要求都有差距,所以需要在字向和位向方面进行扩充才能满足实际存储器的容量要求,通常采用位扩展、字扩展和字位扩展。

1) 位扩展

位扩展法指的是用若干片位数较少的存储芯片构成具有给定字长的存储器。

例如:

用8片8192×1位的芯片构成8K×8位(8KB)的存储器,如图所示。

特点:

1、片选 互连

2、地址线 互连

3、数据线 分别连接各自数据位

4、读写信号线 互连

(2) 字扩展

字扩展法指的是增加存储器中字的数量。

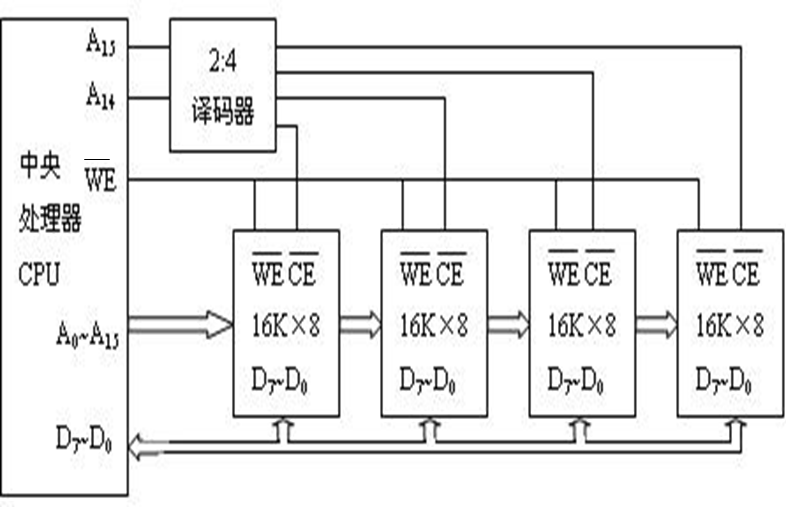

例如:用4片l6K×8位的存储芯片构成容量为64K×8位的存储器。

地址空间分配表

字扩展构成的存储器如下图

(3) 字位扩展

字位扩展是指即增加存储字的数量,又增加存储字长。一个存储器的容量为M×N位,若使用L×K位存储器芯片,则这个存储器共需要 ![]()

个存储器芯片。

二、存储器与CPU的连接

(1) 地址线的连接

存储芯片容量不同,其地址线数也不同。通常总是将CPU地址线的低位与存储芯片的地址线相连。CPU地址线的高位经译码,作为片选信号。

(2) 数据线的连接

CPU的8位数据线(D7~D0),与芯片的8位数据线相连。

(3) 读/写命令线的连接

CPU读/写命令线一般可直接与存储芯片的读/写控制端相连,通常高电平为读,低电平为写。

(4) 片选线的连接

由于存储器是由许多存储芯片组成的,存储芯片的片选控制线和CPU的高位地址有关,CPU的高位地址线经过译码器译码,和访存控制信号共同作用,产生存储芯片的片选信号。

访存控制信号(例如M/IO#或MREQ#),低电平有效时,访问存储器;若为高,访问I/O。

例

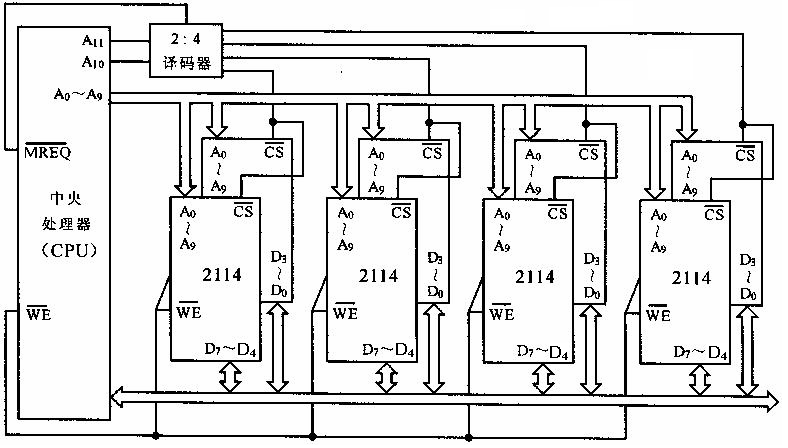

如图是一个小容量存储器的连接图。它由Intel2114芯片经字位扩展而成,容量为4K×8位。Intel2114芯片容量为1K×4位。先用2个Intel2l14芯片位扩展成1K×8位的芯片组,再用4个这样的芯片组字扩展成4K×8位的存储器,共用了8个芯片。Intel2114有10个地址线(A0~A9)、4位数据线(D0~D3)、一个片选端、一个读写控制端。CPU提供12位地址,其中低10位(A0~A9)连接各芯片的地址端,还有两位地址(A11,A10)经译码器,产生4个片选信号,分别连接4组芯片。