1、前言

emm今天射频联调时解决的问题记录一下,因为一直使用spi mode 1配置各种器件,定式思维了,加上乙方过于冷漠不搭理交流不顺,花了好久才解决的问题(疯狂吐槽),其中部分原因是spi 模式不匹配,即主端使用模式1配置模式3的收端,导致一直配置不上额。

1.1、SPI总线概述

SPI是一种串行通信总线,支持全双工通信,相较I2C总线数据速率较高,一般为MHz级别,但缺点是不具备类似I2C总线的应答机制,SPI总线根据时钟极性和时钟相位的不同分为4种模式。

① 时钟极性 :

CPOL=0 :空闲状态时,时钟SCK为低电平;

CPOL=1 :空闲状态时,时钟SCK为高电平;

②时钟相位:

CPHA=0:数据在时钟奇数沿进行采样,在时钟偶数沿输出数据;

CPHA=1:数据在时钟偶数沿进行采样,在时钟奇数沿输出数据;

模式1:CPOL=0 ;CPHA=0;

空闲状态时,时钟SCK为低电平,数据在时钟上升沿进行采样,在时钟下降沿输出数据;

模式2:CPOL=0 ;CPHA=1;

空闲状态时,时钟SCK为低电平,数据在时钟下降沿进行采样,在时钟上升沿输出数据;

模式3:CPOL=1 ;CPHA=0;

空闲状态时,时钟SCK为高电平,数据在时钟下降沿进行采样,在时钟上升沿输出数据;

模式4:CPOL=1 ;CPHA=1;

空闲状态时,时钟SCK为高电平,数据在时钟上升沿进行采样,在时钟下降沿输出数据;

1.2、SPI管脚描述

SPI总线根据管脚数量又分为三线或四线,数据格式一般是由读写位、地址位、数据位组成,只是不同应用场景可能地址和数据位宽的不同。

4 wire SPI:

SCK :SPI总线时钟,方向为主->从;

CS:SPI 片选信号,方向为主->从;

SDI:SPI写数据,方向为主->从;

SDO:SPI读数据,方向为从->主;

3 wire SPI

SCK :SPI总线时钟,方向为主->从;

CS :SPI 片选信号,方向为主->从;

SDIO:SPI读写数据,方向为主<->从;

1.3、spi时序

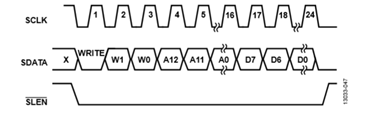

以HMC7044锁相环芯片为例,数据格式如图:

根据手册所述数据读写时序要求可知这是SPI模式1时序。

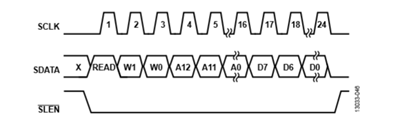

读时序:如图1-14所示,片选信号拉低,接着16位数据在时钟上升沿送入时钟芯片中,对应8 bit寄存器数据会随着下个时钟上升沿串行传输返回至FPGA。

根据读写时序状态机如下图,初始状态为空闲状态,每当有效数据到来时,通过判断最高位读写位的值,如果为0,状态跳转到写数据状态,此时24位数据根据时钟节拍通过移位一位一位送出,如果状态位1,状态跳转到读状态,首先写16位地址,然后在写完地址后开始接受数据。

根据状态转移图,有状态机:

实际上有多种方式可以实现spi时序哈,不一定使用状态机,只做一种参考哈,本设计采用的mode1,然后仿真一下写数据如下,时钟空闲时为低电平,数据在时钟的上升沿采样奥。

然后用示波器可以看到具体进入被配置芯片的信号哈,写信号SCK和SDI:

写信号SCK和NCS:

然后改为mode 3之后,写信号SCK和NCS:

写信号SCK和SDI: