GMII接口的时序:

RXCLK和GTXCLK信号有着相同的功能,都是125M时钟信号,且两者之间的相位差很小,可以忽略,这两个时钟信号控制着RXD【7:0】、RXDV、RXER、TXD【7:0】和TXEN五个信号。当RXDV信号为高,且RXER信号为低时,RXD【7:0】有效,并接收数据。当TXEN信号为高时,TXD【7:0】为有效,并且发送数据。

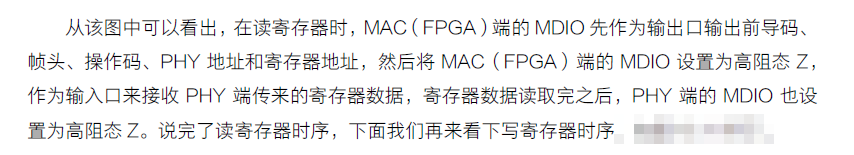

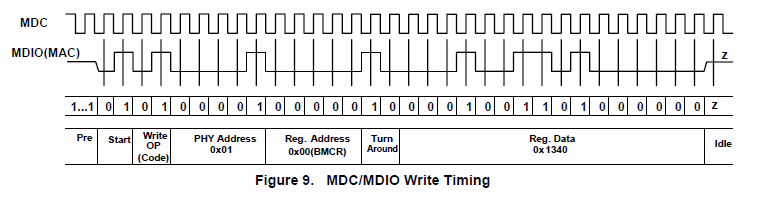

从图中可以看到,写寄存器时序和寄存器时序基本上是一致的,唯一不同的就是,写寄存器时序的时候,我们是不需要PHY输出数据,我们只要闷着头往里面写就可以了。这里,我们需要说明的是,在实际的运用中,我们很少回去配置RTL8211EG寄存器的,因为RTL8211EG芯片支持自动协商模式,可以根据传输速率,自动配置为合适的模式。在我们的程序中就没有对RTL8211EG进行配置,我们直接就能够驱动使用它进行通信。