一、代码风格概述

一样的逻辑电路会有不同的写法,要求设计者写出的代码尽可能优化,编写代码要注意一些基本原则。

二、寄存器电路的设计方式

1.简单的寄存器输入输出模型

通常在每个时钟(clk)上升沿锁存数据。

2.带异步复位的寄存器输入输出模型

通常在每个时钟(clk)上升沿锁存数据,异步复位信号(rst_n)下降沿强制清零。

3.带异步置位的寄存器输入输出模型

通常在每个时钟(clk)上升沿锁存数据,异步置位信号(set)上升沿强制置位。

4.既带异步复位又带异步置位的寄存器输入输出模型

两者同时有效时可通过设置优先级解决两者的冲突问题

if(!rst_n)

dout <= 1'b0;

else if(set)

dout <= 1'b1;

else

dout <= 1'b2;

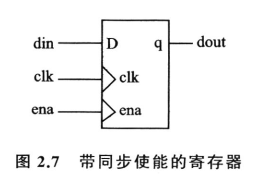

5.带同步使能的寄存器输入输出模型

三、同步以及时钟的设计原则

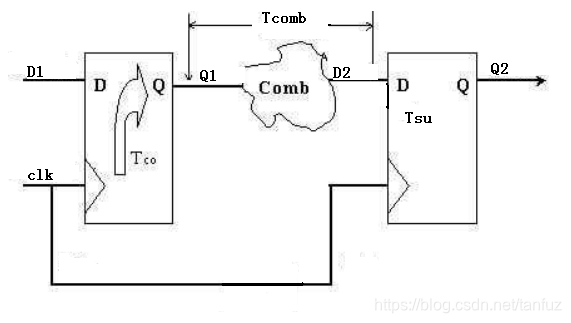

1.建立时间

在时钟的有效沿之前,必须保证输入寄存器的数据在建立时间(Tsu)内是稳定的。这要求寄存器从时钟沿到来后,前一级寄存器的D端到Q端的输出响应延时Tco+组合逻辑的传输延时Tdelay很小,确保在下一个时钟沿到达之前,前一级寄存器的输出数据能够“准时”到达下一级寄存器,从而保证下一级寄存器能及时采样到上一级寄存器的输出数据。其中Tco是对寄存器本身性能的要求,Tdelay是对布局布线的要求。

2. 保持时间

在时钟的有效沿之后,必须保证寄存器的输出数据在保持时间(Th)内是稳定的。这要求寄存器的在上一级数据到达之后及时为自己 “充好电”,达到上一级的输入电平,如果上一级寄存器采样得到的低电平经过Tco+Tdelay后还没有“充好电”,那么上一次到达的高电平会比下一次到达的低电平取代,导致下一级寄存器无法正确的捕获上一级寄存器的高电平数据。

(建立时间要求Tco+Tdelay尽可能短以确保上一级输出寄存器的信号及时到达下一级寄存器的输入端,而保持时间要求Tco+Tdelay尽可能长以确保留给下一级寄存器足够多的时间完成“充电”过程。)然而我们的设计要求提升时钟clk的频率,这就要求Tco+Tdelay尽可能短,从而对寄存器的要求是输出响应延时Tco短且保持时间Th("充电时间)尽可能短,因此要提升系统的整体工作频率就对器件本身的性能提出了更高的要求,也意味着更高的成本。此外,提升频率要求Tco+Tdelay尽可能短,也需要我们尽可能减少布局布线造成的延时。

3.几个时钟设计要点

(1)避免使用门控时钟,或系统内部逻辑产生的时钟

(2)分频倍频采用专门的时钟管理单元(PLL、DLL)

(3)尽量对输入的异步信号用时钟进行锁存:异步信号的同步机制

(4)避免使用异步信号进行复位或置位控制

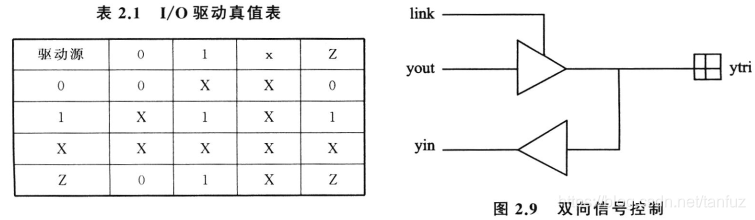

四、双向引脚的控制代码

五、提升系统性能的代码风格

1.减少关键路径的逻辑等级

整个电路时序不收敛可能只于其中某一两条关键路径有关,只要解决了这关键的一两条路径就可是满足时序约束。

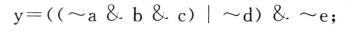

例如如下逻辑运算:

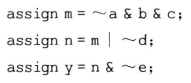

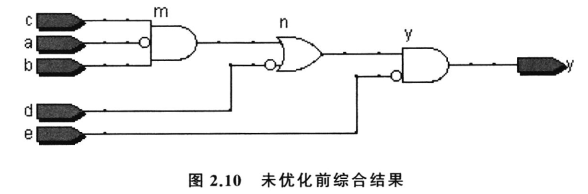

常规思路代码:

综合结果:

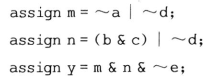

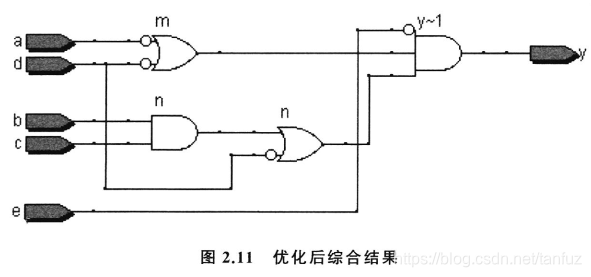

若a到y的路径是影响整个电路时序约束的关键路径,可以考虑减少a到y的逻辑等级:

优化后综合结果:

a到y的逻辑等级由3减少到2,解决了关键路径问题,但代价是增加了一个逻辑门,体现了“面积换速度”的思想。

2.逻辑复制(减少重载信号的散出)与资源共享

逻辑复制通过增加面积改善时序约束,如果某个信号需要驱动的后级信号较多,可以复制该信号的生成逻辑,加入多个同频同相的信号驱动后续电路。

资源共享是与逻辑复制的逆过程,节省资源,牺牲速度。

3.消除组合逻辑的毛刺

逻辑期间和路径都存在延时,多个信号到达输出端的时间不一致,可能导致多个错误毛刺信号的输出。

解决方法1:输出端加电容滤波,FPGA不能实现

解决方法2:输出端加一级寄存器