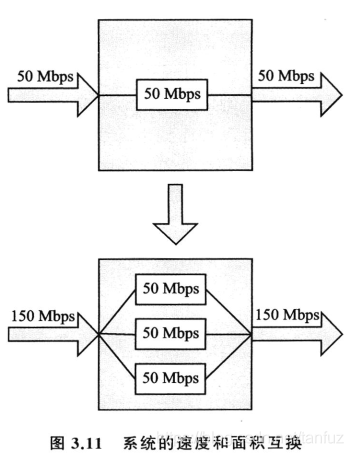

一、速度面积互换原则

速度的提高要以面积的增扩为代价。

例如有时关键路径过长,频率无法提升,这是可以将关键路径的信号打一拍,减小路径长度,利于频率提升;再比如一定逻辑资源可以达到50Mbps,若用三倍的逻辑资源实现相同的功能则可以将速度提升3倍。

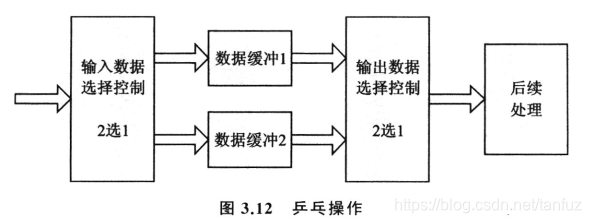

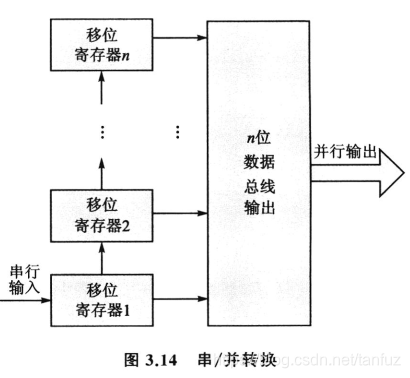

二、乒乓操作及串并转换设计

1.乒乓操作

2.串并转换

3.流水线设计

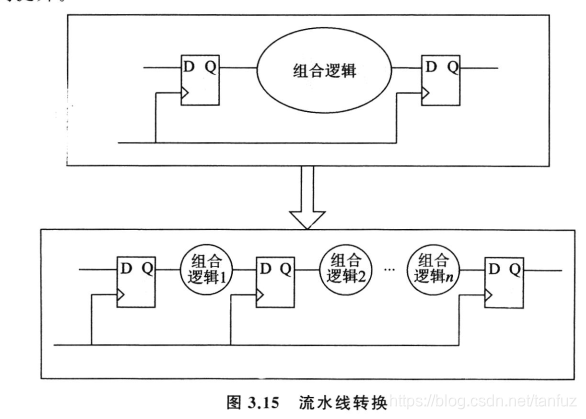

如果数据流是单向的,前一个步骤的输出即下一个步骤的输入,可以通过流水线设计从某种程度上提高系统频率,常用于高速信号处理领域。

典型的流水线设计是将原本一个时钟周期完成的较大的组合电路用多个时钟周期完成,这样该部分的逻辑的运行频率会后很大的提升,尤其是当他是一条关键路径,整个系统性能会有很大提升,流水线设计体现面积换速度的思想。

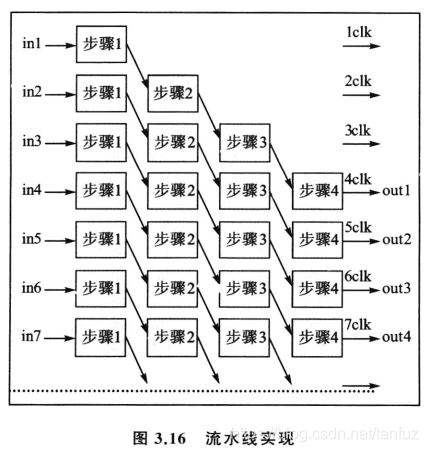

假设一个流水线设计需要四个步骤完成,那么从数据输入的第一个时钟周期开始,需要四个时钟周期后才能输出,但是之后就会不间断的输出,不采用流水线设计处理一个数据需要四个时钟周期,而采用流水线设计只需要一个时钟周期。

四、逻辑复制与模块复用

逻辑复制通过增加面积改善时序约束,模块复用是逻辑复制的逆过程。

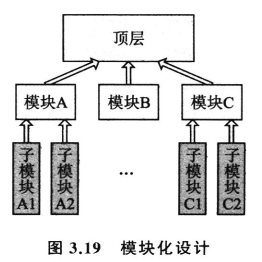

五、 模块化设计

一般顶层设计只做例化,不做逻辑,模块化设计步骤:

(1)初始预算:为系统整个设计进行位置布局

(2)子模块激活:每个项目成员并行完成各子模块的设计

(3)模块的最后合并:将顶层与子模块结合组织起来

模块划分的准则:

(1)子模块功能相对独立

(2)模块内部联系尽量紧密

(3)模块之间连线尽可能简单

对于难以满足模块划分且具有强内部关联的复杂设计并不适合采用模块化设计方法。

六、时钟设计技巧

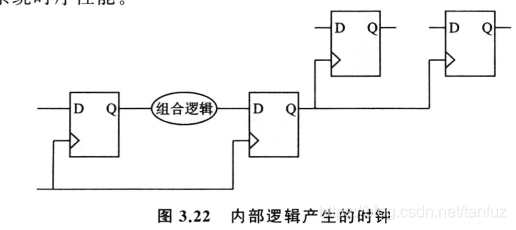

1.内部逻辑产生的时钟

对组合逻辑分频后的时钟打一拍,避免组合逻辑产生的毛刺。

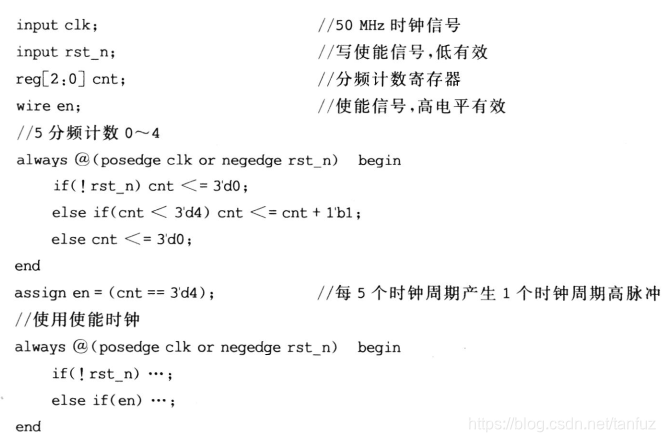

2.分频时钟与使能时钟

尽量使用PLL或者DLL,在无法使用PLL或者DLL时,可以利用内部产生的时钟作为使能时钟。

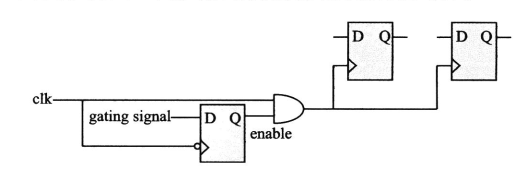

3.门控时钟

通过加入使能信号对时钟开关进行控制,从而降低系统功耗,将门控使能信号进行打拍有利于解决毛刺问题