FPGA学习笔记

图像处理算法

1. 灰度图像均值滤波算法

1.1 原理

1.2 FPGA实现灰度图像均值滤波算法

1. 灰度图像均值滤波算法

1.1 原理

-

均值滤波:线性滤波,邻域平均法。

-

原理:用均值代替原图像中的各个像素值。即以目标像素(x,y)为中心的找出N个像素f(x,y),再用这N个像素的平均值代替原目标像素,作为处理后的图像的点g(x,y)=(1/N)(∑f(xi,yi))。

-

缺点:不能很好的保护图像细节,使图像变得模糊,不能很好的去除噪声点。

1.2 FPGA实现灰度图像均值滤波算法

-

项目目标:

将彩色图片,通过灰度处理,均值滤波算法,进行去噪处理,并通过FPGA显示到TFT显示屏上。 -

FPGA实现步骤:

- 形成3*3矩阵像素

- 求周围邻域8个点的像素之和.

- 将结果右移3位(相当于除8),得到结果.

-

FPGA实现方法:

方法(2种): 1. 通过R/G/B通道形成单色通道进入均值滤波器,实现灰度图像的均值滤波. 2. 将RGB图像转换成Ycbcr图像,Y通道进入均值滤波器,实现灰度图像的均值滤波.-

通过R/G/B通道形成单色通道进入均值滤波器,实现灰度图像的均值滤波

-

将RGB图像转换成Ycbcr图像,Y通道进入均值滤波器,实现灰度图像的均值滤波

-

-

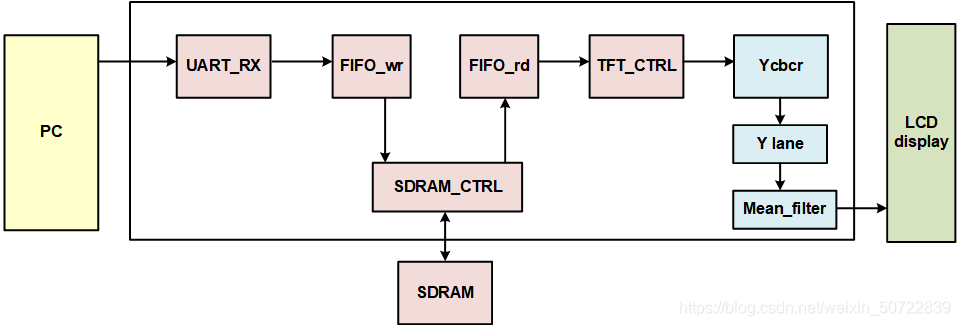

项目组成模块:

① pll: 产生项目所需时钟:1. SDRAM控制器时钟;2. SDRAM时钟信号;3. TFT屏控制器时钟

② uart串口协议(uart_rx, uart_tx)

③ 读FIFO

④ 写FIFO

⑤ SDRAM控制模块

⑥ TFT屏控制模块

⑦ 灰度处理,均值滤波模块 -

Verilog代码

/*

- 形成3*3矩阵像素

- 求周围邻域8个点的像素之和

- 将结果右移3位(相当于除8),得到结果。

*/

module mean_filter_r0(

input clk,

input rst_n,

input [15:0] data_in,//输入像素

input data_in_en,//lcd显示区使能信号

output reg [15:0] data_out,//输出像素

output wire data_out_en

);

wire [15:0] r0;

wire [15:0] r1;

wire [15:0] r2;

reg [15:0] ro_c0;

reg [15:0] ro_c1;

reg [15:0] ro_c2;

reg [15:0] r1_c0;

reg [15:0] r1_c1;

reg [15:0] r1_c2;

reg [15:0] r2_c0;

reg [15:0] r2_c1;

reg [15:0] r2_c2;

reg de_reg0;

reg de_reg1;

reg de_reg2;

wire [18:0] add_out;

//----3line pixels-----------------------------------

shifter3_3 shifter3_3(

.clken(data_in_en),

.clock(clk),

.shiftin(data_in),

.shiftout(),

.taps0x(r0),

.taps1x(r1),

.taps2x(r2)

);

//-------------------------------------------------

//----3*3 matrix pixels from image-----------------

//----r0-------------------------------------------

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

ro_c0 <= 16'd0;

ro_c1 <= 16'd0;

ro_c2 <= 16'd0;

end

else if(data_in_en)begin

ro_c0 <= r0;

ro_c1 <= ro_c0;

ro_c2 <= ro_c1;

end

end

//----r1-------------------------------------------

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

r1_c0 <= 16'd0;

r1_c1 <= 16'd0;

r1_c2 <= 16'd0;

end

else if(data_in_en)begin

r1_c0 <= r1;

r1_c1 <= r1_c0;

r1_c2 <= r1_c1;

end

end

//----r2-------------------------------------------

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

r2_c0 <= 16'd0;

r2_c1 <= 16'd0;

r2_c2 <= 16'd0;

end

else if(data_in_en)begin

r2_c0 <= r2;

r2_c1 <= r2_c0;

r2_c2 <= r2_c1;

end

end

//-------------------------------------------------

//----timing --------------------------------------

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

de_reg0 <= 1'd0;

de_reg1 <= 1'd0;

de_reg2 <= 1'd0;

end

else if(data_in_en)begin

de_reg0 <= data_in_en;

de_reg1 <= de_reg0;

de_reg2 <= de_reg1;

end

end

assign data_out_en = de_reg2;

//-------------------------------------------------

//----add------------------------------------------

add_paral add_paral(

.clken(data_in_en),

.clock(clk),

.data0x(r0),

.data1x(ro_c0),

.data2x(ro_c1),

.data3x(r1),

.data4x(r1_c1),

.data5x(r2),

.data6x(r2_c0),

.data7x(r2_c1),

.result(add_out)

);

//-------------------------------------------------

//----divide 8-------------------------------------

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

data_out <= 16'd0;

else if(data_in_en)

data_out <= add_out[18:3];

else;

end

endmodule

- 项目结果

5寸TFT电容触摸显示屏

图像:800*480像素

(1). (易烊千玺^^)网络原图:

(2). FPGA显示原图:

(3). FPGA灰度处理图:

(4). FPGA均值滤波图:

项目结果分析:

- 对比于原图与灰度处理图,经过均值滤波后,图像明显变得更加模糊,同时验证了均值滤波在图像去噪时,不能很好的保护图像细节的缺点。

参考资料:《FPGA系统设计与验证实战指南》

【注】:个人学习笔记,如有错误,望不吝赐教,这厢有礼了~~~