对之前的补充操作

说正题之前,先讲讲之前(二)没涉及到的,但是(三)用到的额外操作吧:

- BUS连线

- Verilog版图仿真

Verilog版图仿真

首先Verilog版图仿真,在之前的(一)(二)中介绍了两种TB方式,一种是用pulse产生的脉冲,另一种就是基于Verilog的数模混合仿真。但在INV里版图用的是第一种。那么第二种在Layout绘制后的config里,会发现Environment里面没有switch view list就无法像之前那样直接添加calibre

这次在config打开后的选项选这个

然后这样把你想要的画好的layout选择calibre

BUS连线

对于Verilog写出的多位寄存器,如 reg [3:0] A这种就会变成这样的BUS类型。想要单个连线就需要一些额外的操作。

一张图大家就能知道如何操作了

就是在线上用wire label标注线,然后就和AD的NET非常像,对应就好。

一位全加器

因为多位全加器的基础是一位全加器所以下面演示一位全加器。

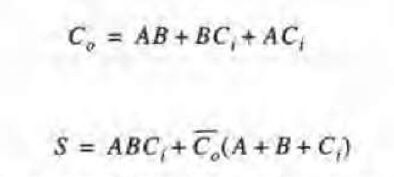

基本表达式转换如下

根据复杂CMOS门设计,NMOS设计就是非下面的东西,也就是C0非后AB+Ci(A+B),同理如此。

然后原理图就如下:

如(一)一样设计原理图(不知道怎么画的看系列(一)和(二))

然后TB用Verilog编写如下

`timescale 1ns/10ps

module add_tb (out1,out2,out3);

output out1,out2,out3;

reg out1,out2,out3;

initial begin

out1=1'b0;

out2=1'b0;

out3=1'b0;

#10;

out1=1'b1;

out2=1'b0;

out3=1'b0;

#10;

out1=1'b0;

out2=1'b0;

out3=1'b1;

#10;

out1=1'b0;

out2=1'b1;

out3=1'b0;

#10;

out1=1'b1;

out2=1'b1;

out3=1'b0;

#10;

out1=1'b1;

out2=1'b0;

out3=1'b1;

#10;

out1=1'b0;

out2=1'b1;

out3=1'b1;

#10;

out1=1'b1;

out2=1'b1;

out3=1'b1;

end

endmodule

仿真原理图

仿真如下

版图绘制

建议

画完后的感觉,首先相对应的NMOS和PMOS要栅极对着放,然后要对其。放每个的时候可以用别的层如TW层写注记符帮忙记住哪个MOS是哪个。每个位置放的时候要想好各个的关系和连线。不然连线很难单层Metal(这里…我改了好久)

一样的进行DRC、LVS、PEX仿真。如最前的Verilog版图仿真测试。

四位加法器

原理如图所示:

原理图连接:

TB编写:

"functional"

`timescale 1ns/10ps

module add_4_verilog (A,B,C );

output[3:0] A,B;

output C;

reg[3:0] A,B;

reg C;

initial begin

A=4'b0000;

B=4'b0000;

C=0;

#10;

A=4'b1111;

B=4'b1111;

C=1;

#10;

A=4'b0001;

B=4'b1111;

C=1;

end

endmodule

TB原理图:

Layout:

注意: 将SUB连上(用AA和SN、SP),N-WELL尽量连接在一起,不然就要用N-WELL重新连,但千万不要拆开…不然会出现很多莫名的连线…同时按Del的时候一定要注意有没有选中对象…发现Del后没发生改变直接Undo撤销…不然…哎,Co连Ci,然后重新M1TXT,标注A<3:0>,B<3:0>,Ci0,gnd!,vdd!,S<3:0>,Co3。

仿真结果:

为什么后面的级会出现波动?答:因为冒险和竞争,利用寄存器存储稳定结果即可。

感受:

…画版图…真的累眼睛和脑子…一个加法器也画了3、4天…之后的日子要么继续做FPGA图像处理,利用HLS配合zynq,继续做比赛。要么去用FPGA做CPU,去龙芯杯试试水,做个没得感情的炮灰…(清华的机组实验…为啥我们就…哎)