欢迎关注个人公众号摸鱼范式

网络课程《数字集成电路静态时序分析基础》的笔记

Time borrowing

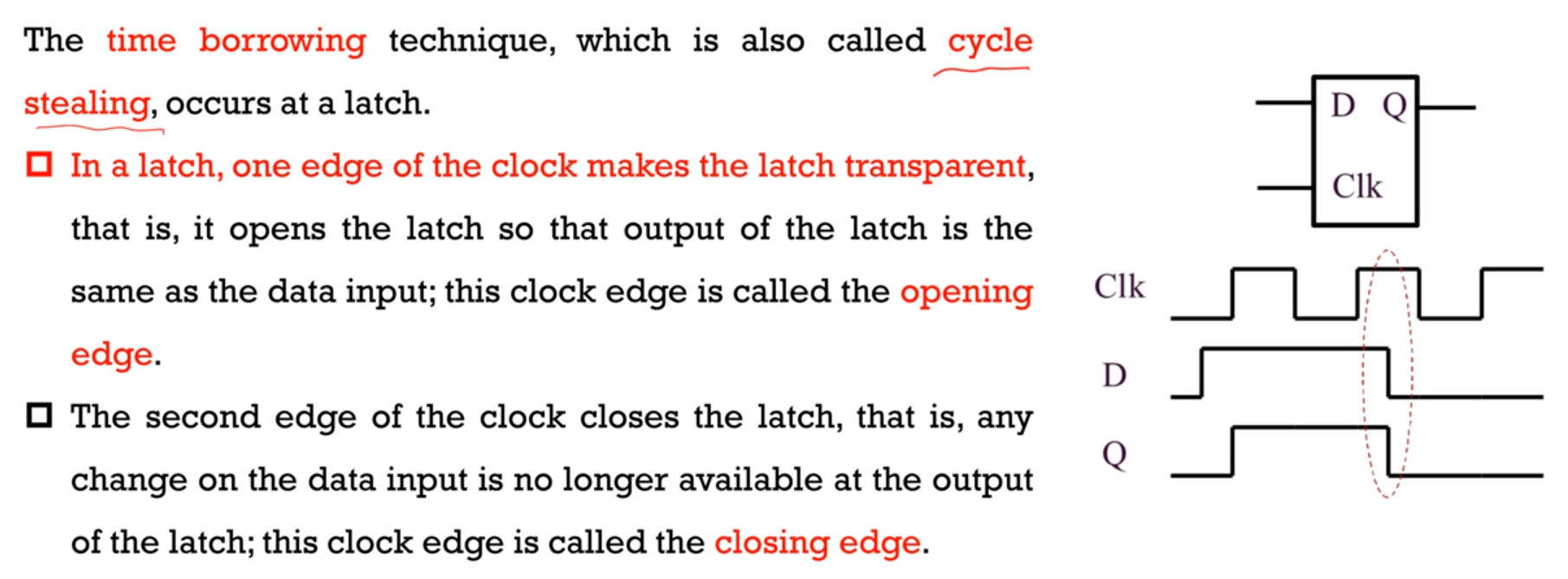

latch在高电平时透明,dff在边沿采样

opening edge指边沿跳变以后有效的边沿,closing edge指边沿跳变之后无效的边沿

通常触发器有建立时间和保持时间的要求,对于latch也是有类似的要求的。latch可以在opening edge以后变化,这种情况类似于向后借时间了,所以称之为Time borrowing。

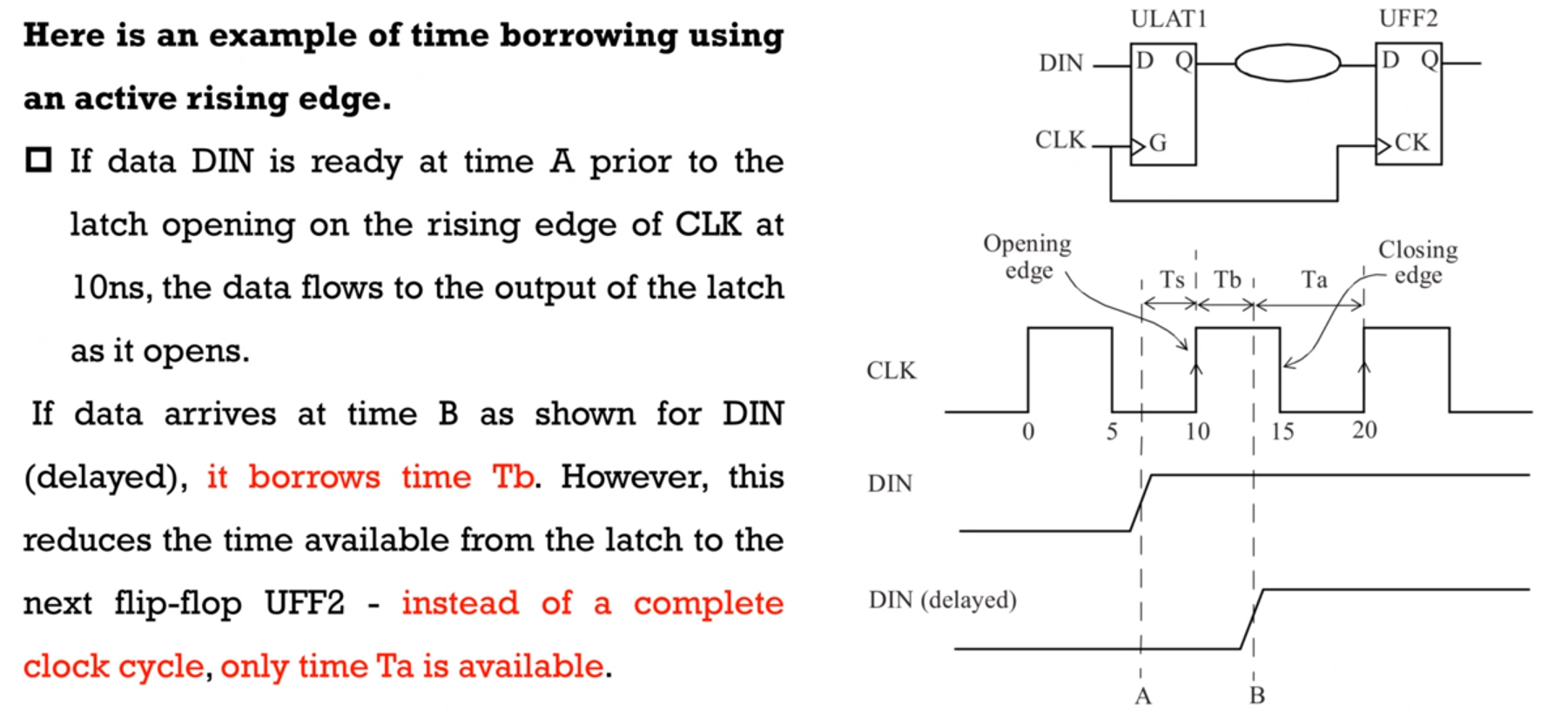

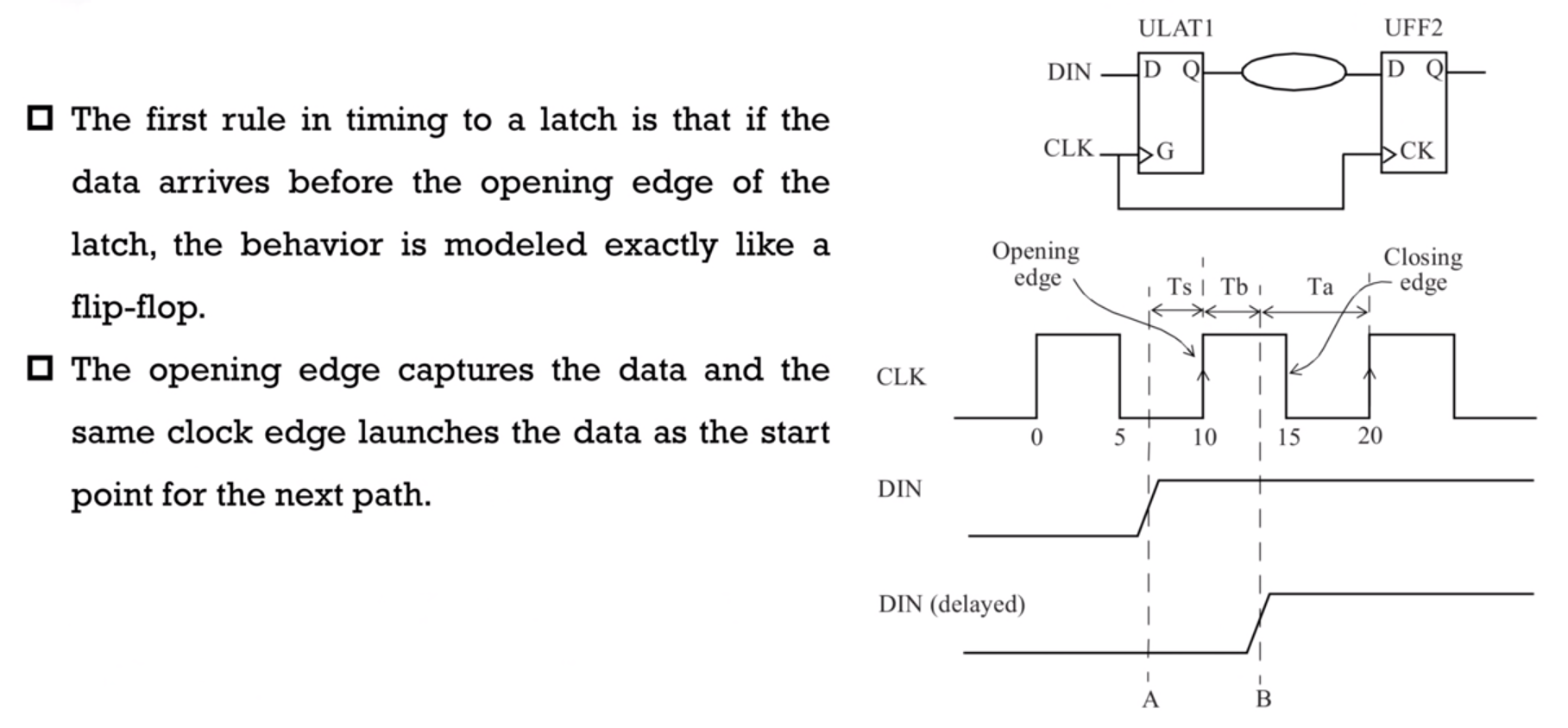

一个time borrowing的例子,数据可以在建立时间之前到达(DIN),也可以在边沿以后到来(delay),翻转到边沿的时间称为time borrowing,进一步下一个周期的时间余量就会变小

三种slack,如果在opening之前到来,成为positive edge,在opening和closing之间成为zero edge,可以使用time borrowing保证时序,如果在closing之后到来,那么就会产生时序违例,因为就算使用time borrowing也无法让数据正确采样。

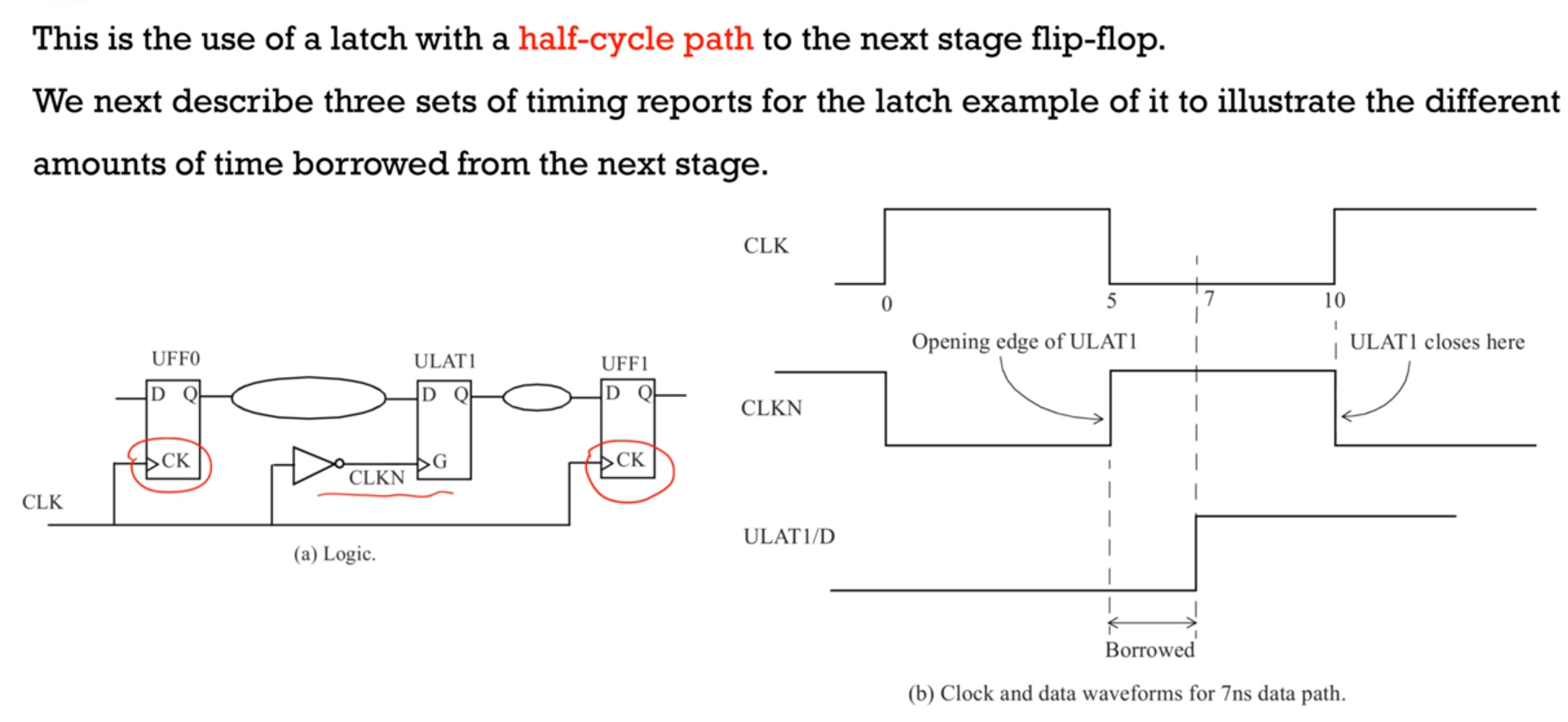

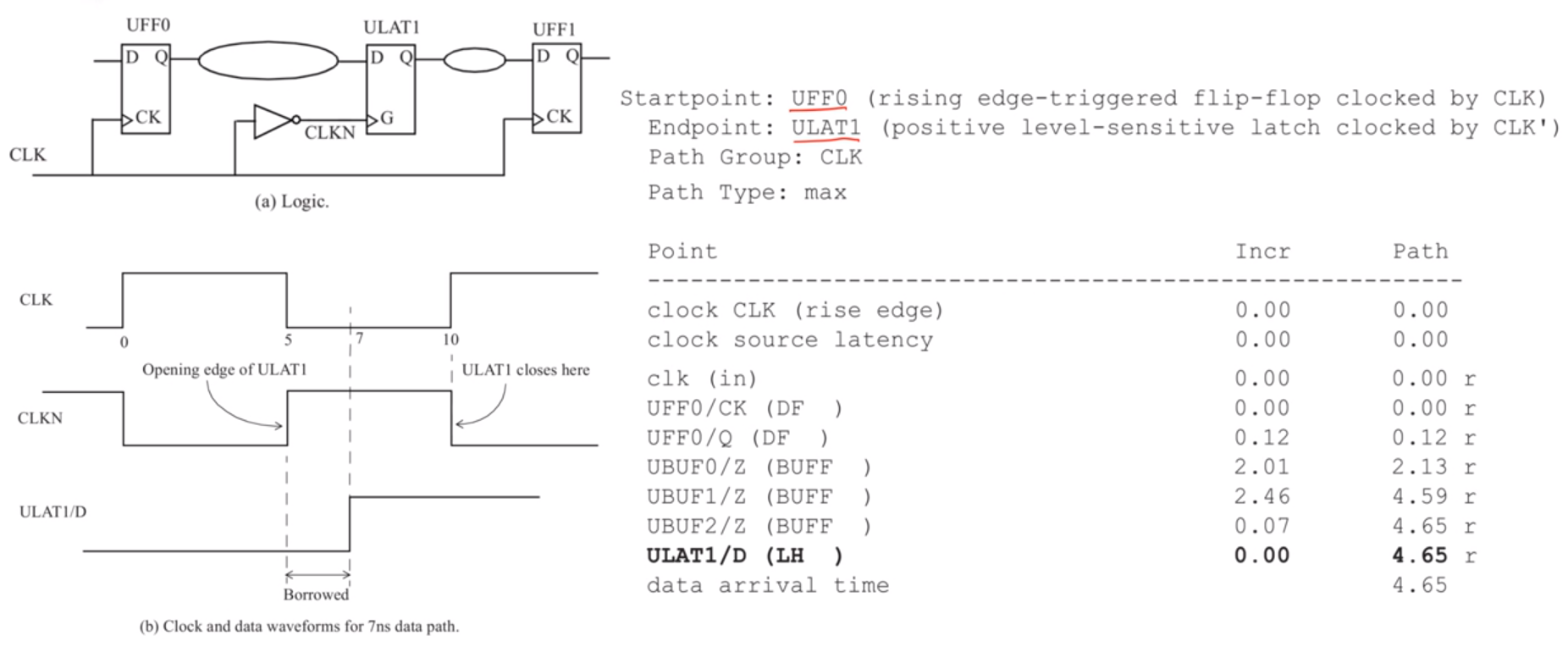

使用latch的一个例子,缓和时序

UFF0到ULAT1之间的逻辑延迟小于5ns,那么数据在opening edge之前到来

时序报告,期待您是UFF0终点时ULAT1,发射路径:

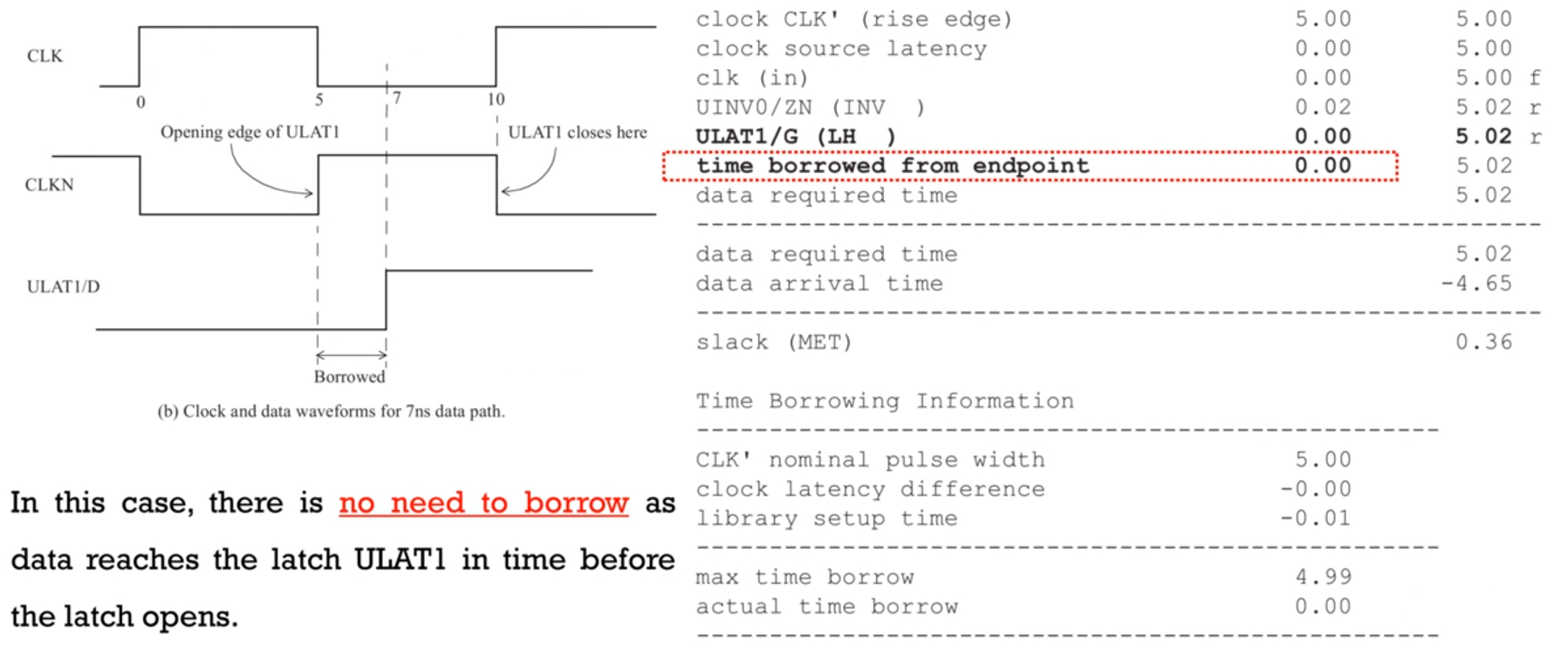

捕获路径,不需要借时间,时序满足

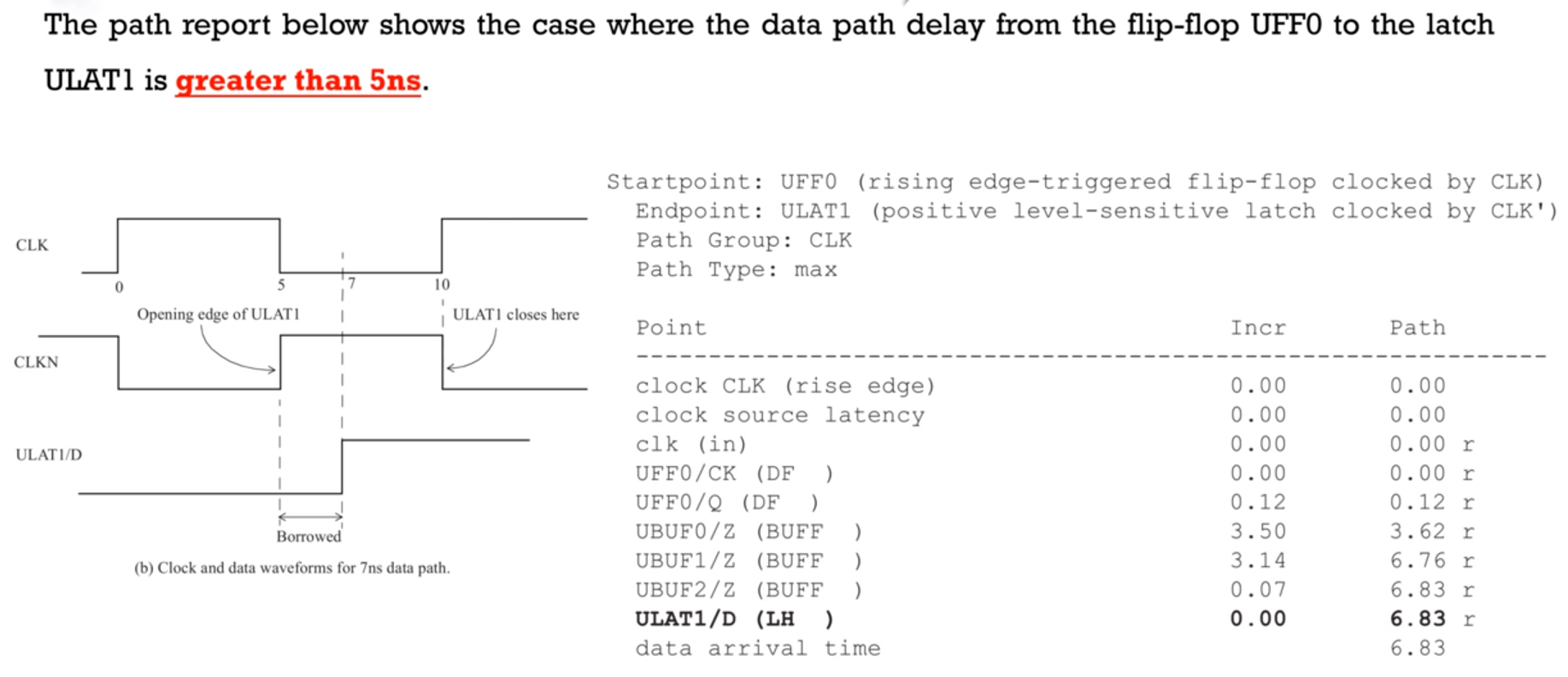

下面是zero slack,发射路径

捕获路径,使用time borrowing,借了1.81ns

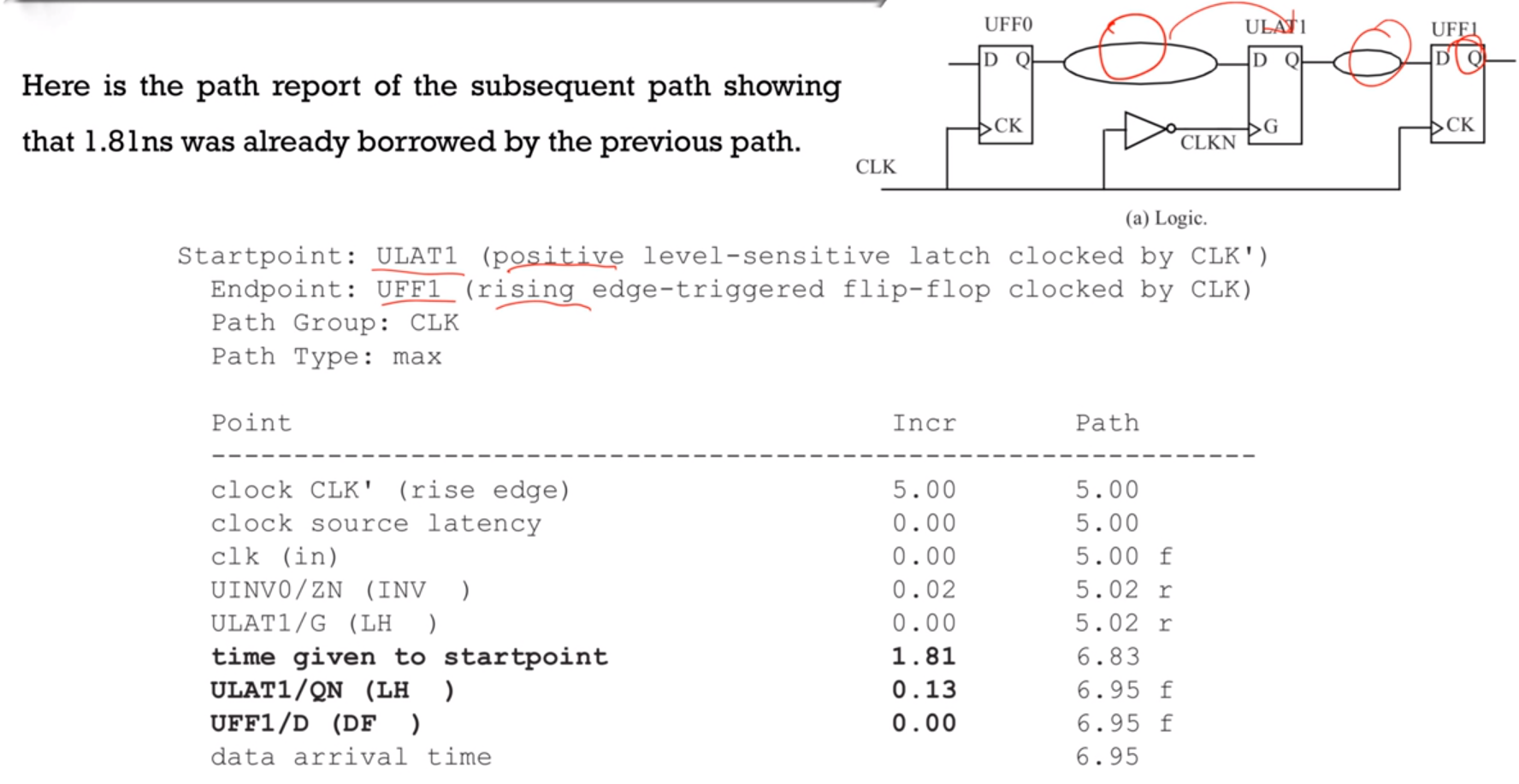

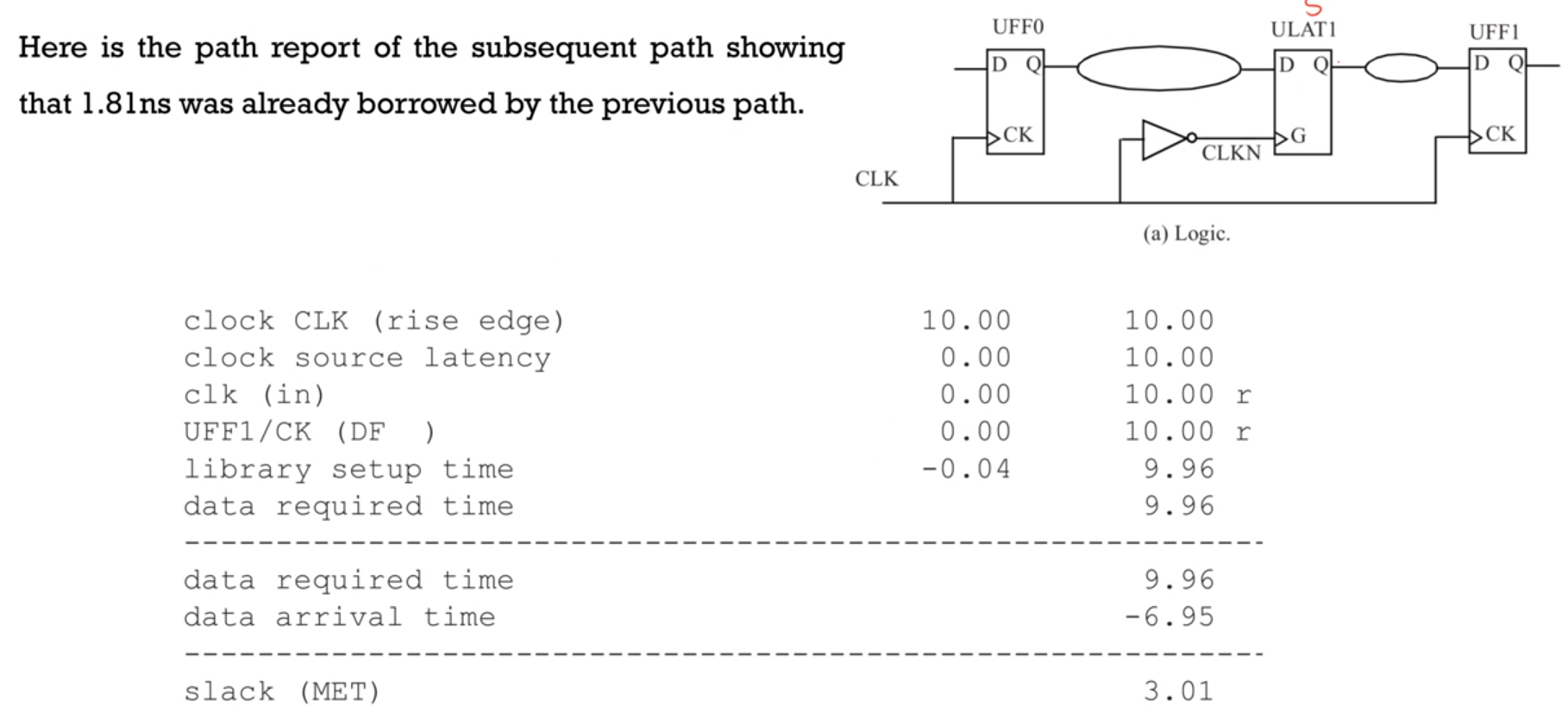

下面分析发生time borrowing时ULAT1到DFF1的时序,首先发射路径,注意,类似半周期路径,clock CLK‘ incr为5

捕获路径,时序满足

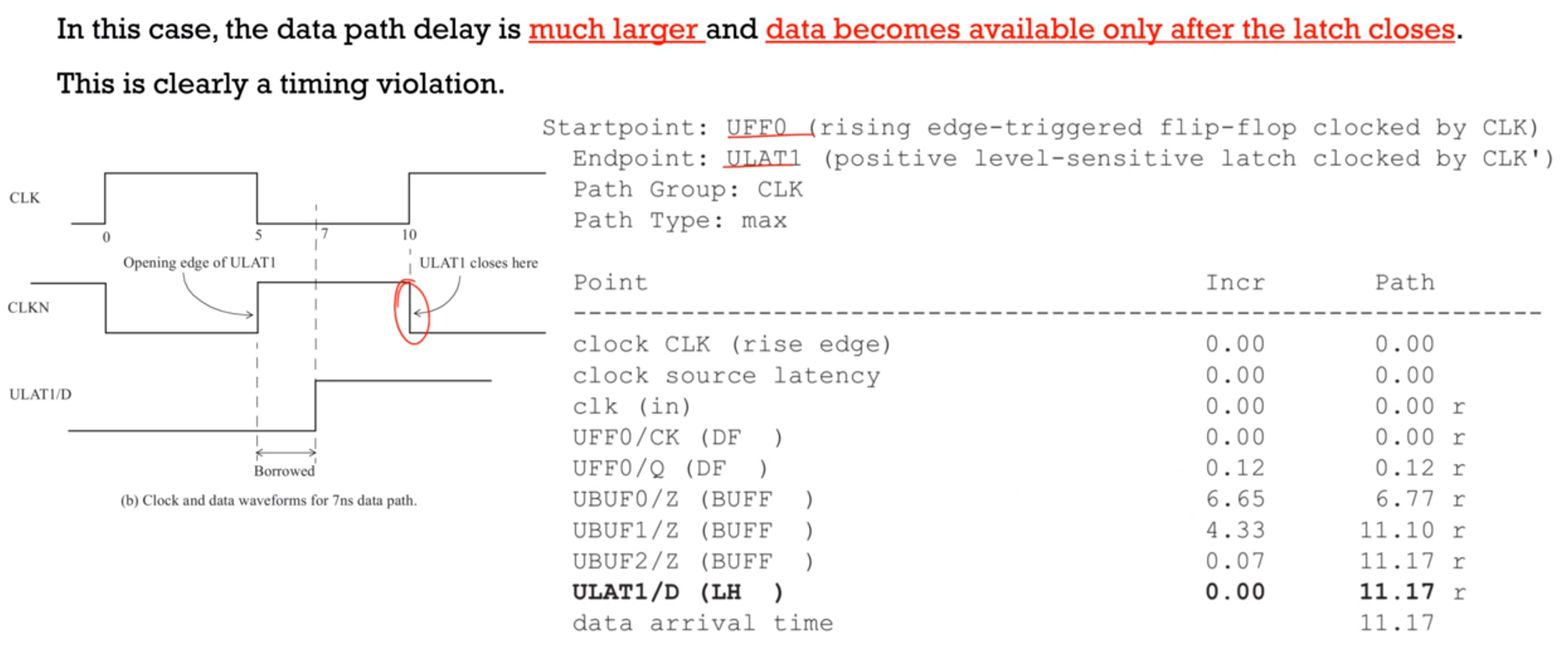

negedge slack,发射路径

捕获路径,就算借满所有时间,也无法满足时序(4.99是要减去setup时间0.01)

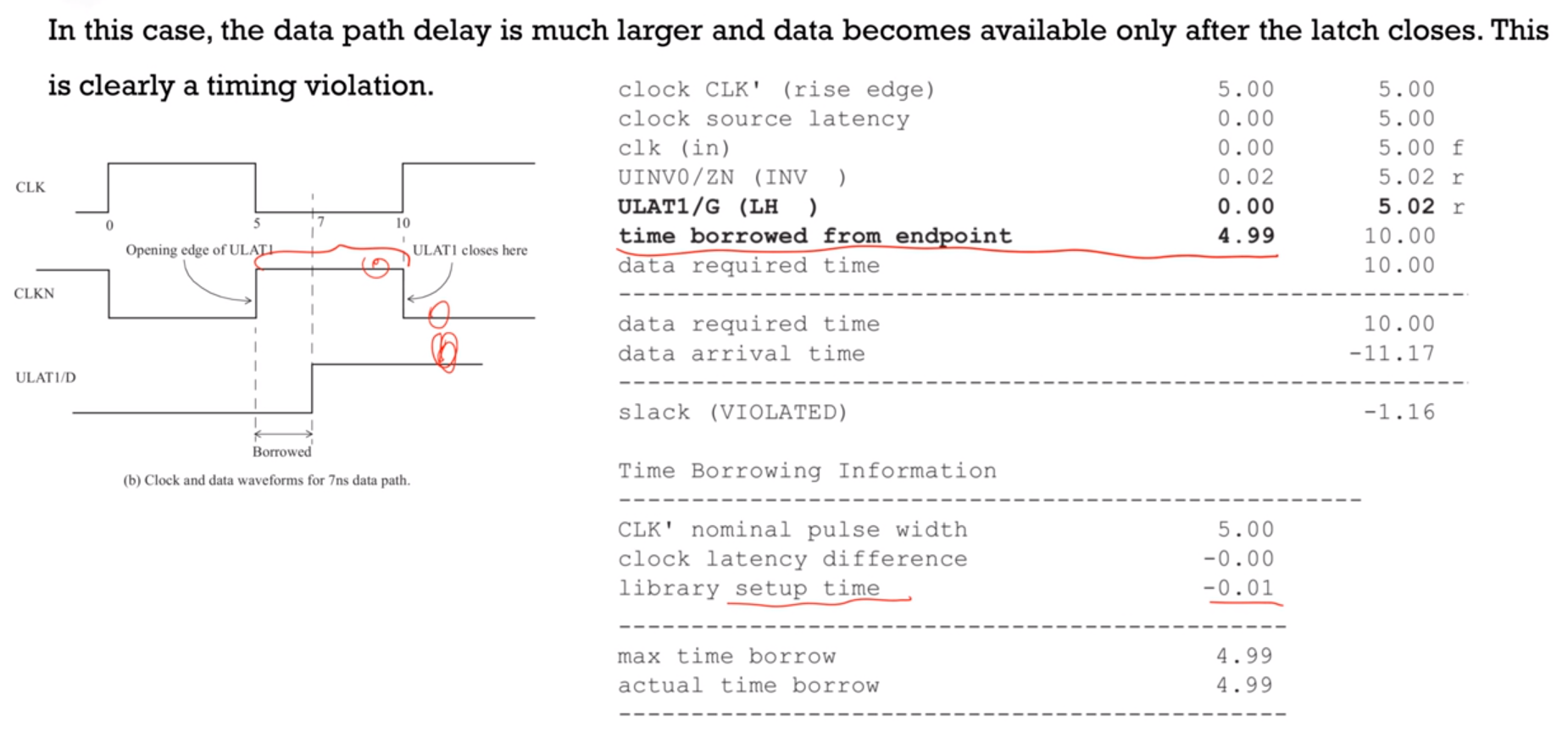

Data To Data check

检查两个pin之间的关系,而且并没有时钟,一个为constrainted pin类似于DFF的数据端,一个related pin类似于DFF的clock

这种检查的不同之处为,建立时间检查是在同一个边沿检查的,因此称之为zero-cycle check

data to data check使用set_data_check约束进行检查

这是用于约束外部引脚的约束

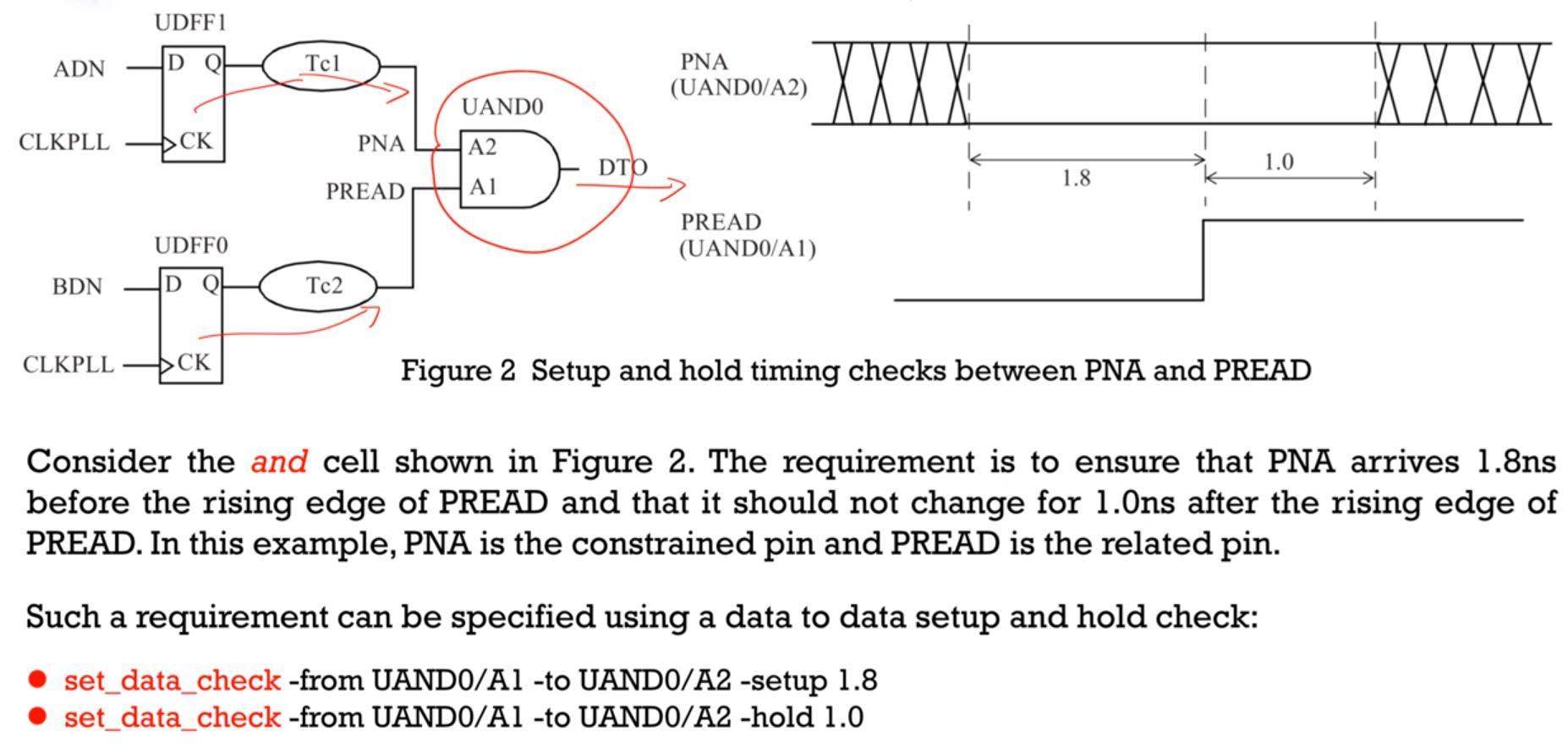

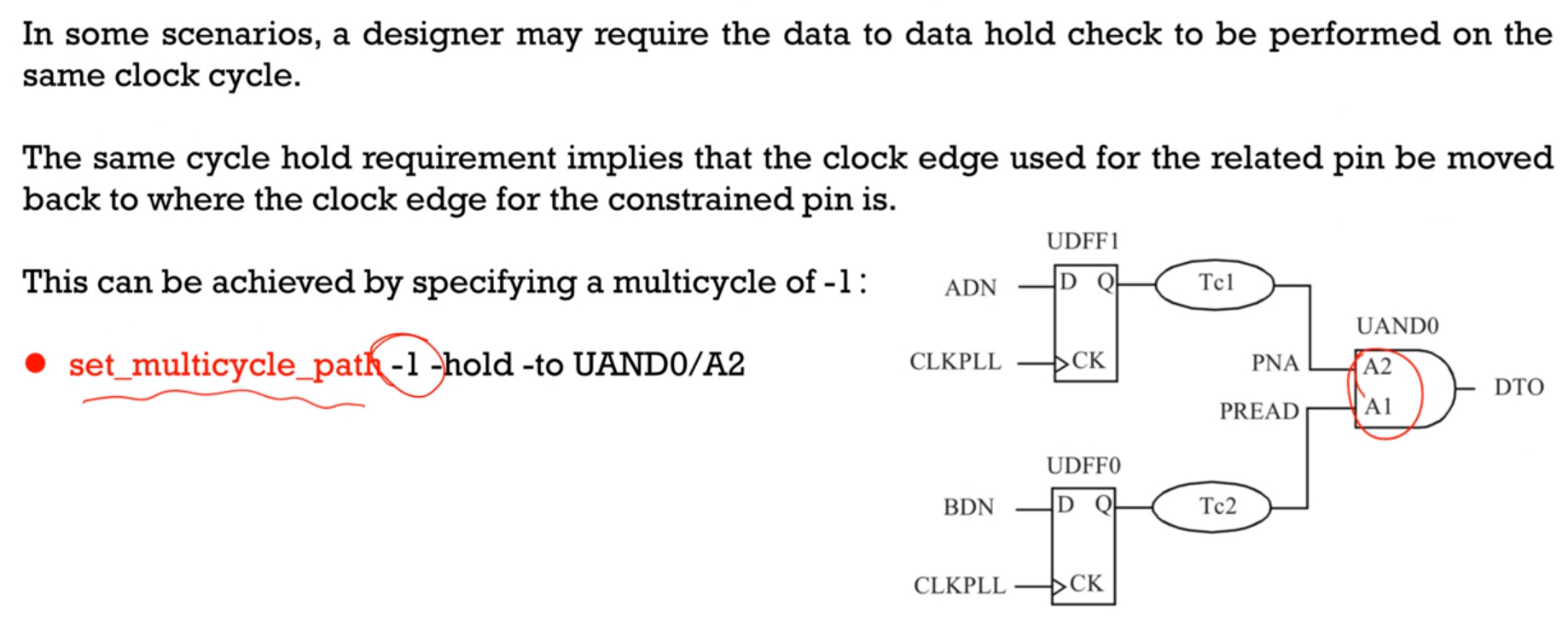

一个例子,对于与门,为了避免毛刺,进行约束

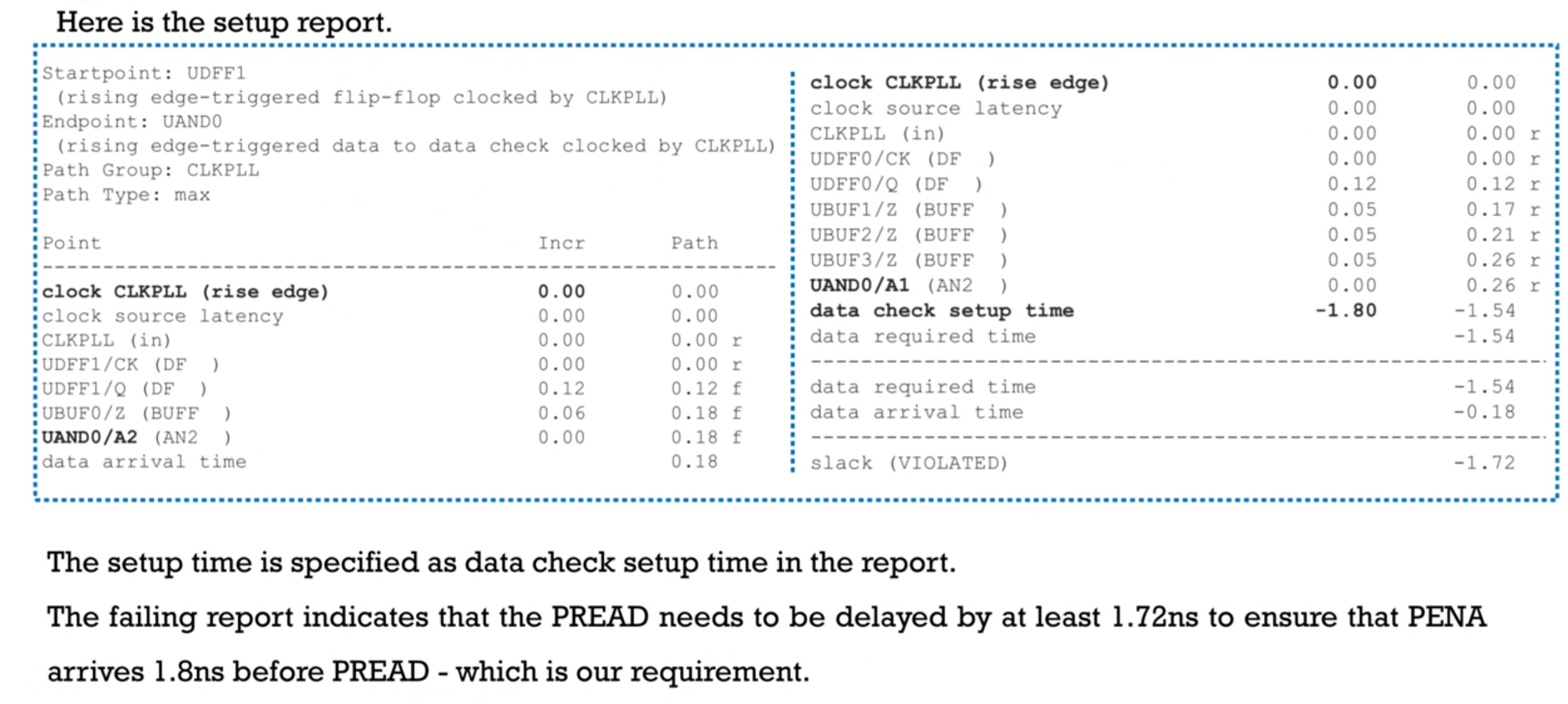

约束时序报告,注意时序报告中的是data check setup time

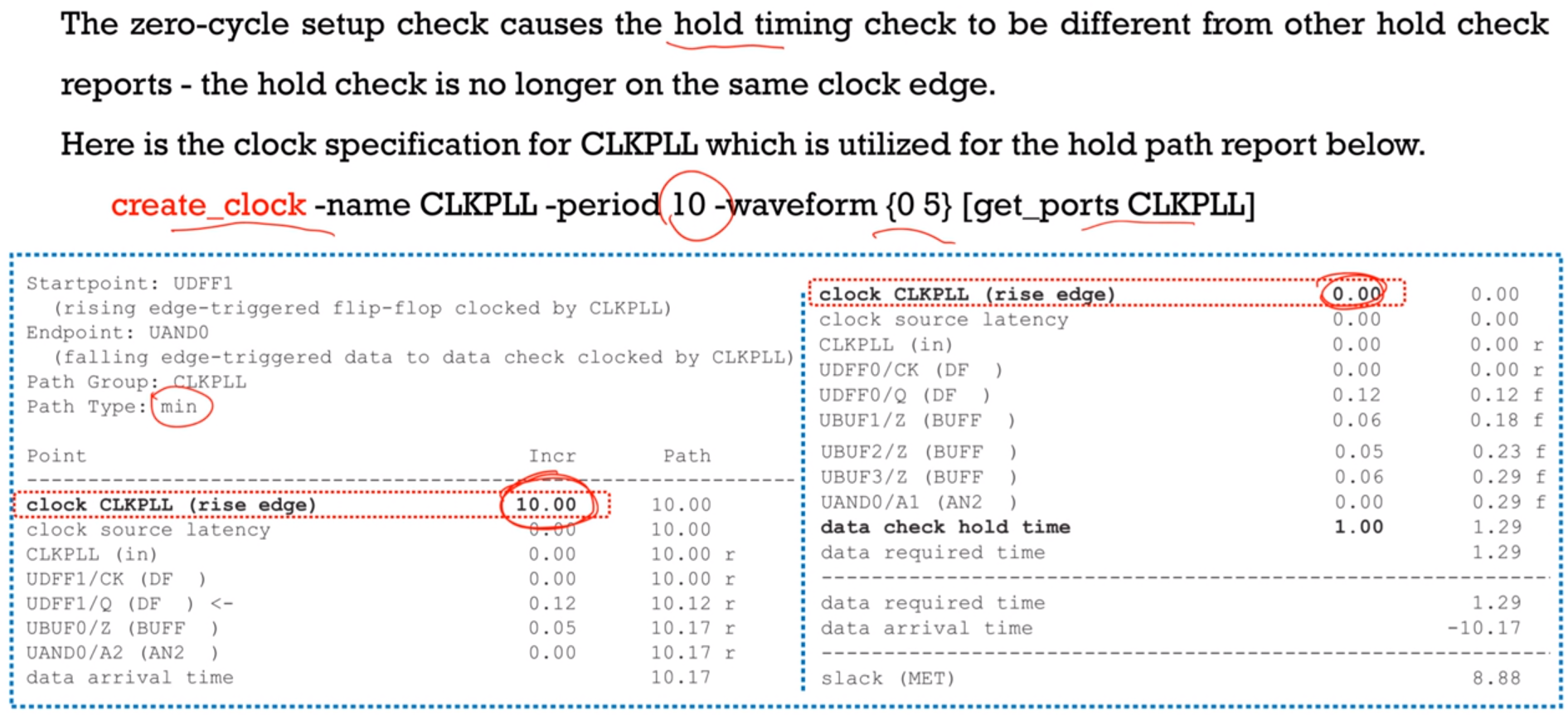

上面是建立时间检查,下面是保持时间检查,在发射路径中,是从10开始的,这相对于建立时间先前移动了一个周期。

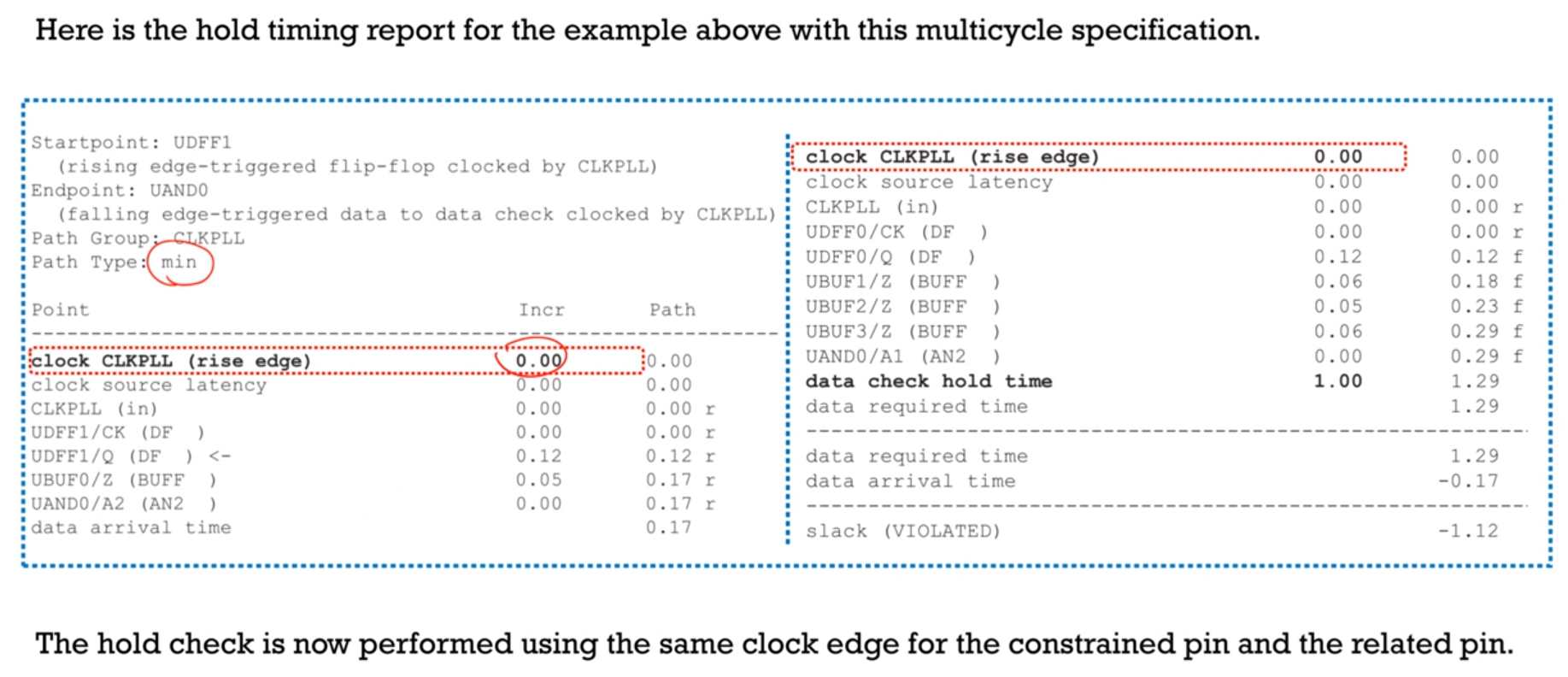

如果现在同一个边沿检查hold,可以使用多周期约束实现

多周期约束以后,发射路径从0开始

也可以将两个信号的约束反向,保持时间约束通过反向的建立时间约束实现,在同一个边沿进行检查

data to data check 也可以用于约束要求信号在时间内保持不变