一、静态时序分析的概述

时序弧

时序弧:用来描述两个节点延时信息的数据

时序弧通常又分为连线的延时和单元的延时

连线的延时指的是单元的输出端口和扇出的网络负载之间的延时信息。

单元的延时指的是单元的输入端口到单元的输出端口的延迟信息。

一条的完整的时序路径信息是由连线的延时加上单元的延时构成一个时序弧。

信号翻转的时候要注意时间的点卡的位置

逻辑的延时cell由输入端口都输出端口的延迟。

建立时间:时钟上升沿之前数据要保持稳定不变的时间

数据如果在建立时间之间进行变化,触发器就会亚稳态,通过建立时间约束整个电路的最大延迟值。最大的延迟不能超过建立时间的界限。

保持时间:就是时钟上升沿之后依然有一段时间数据保持不变。如果在保持时间之内变化,触发器也不能得到稳定的数据。保持用来计算最小的延迟。

静态时序分析把整个电路划分为不同时序的路径,再检查每条时序路径上面的建立时间和保持时间是否符合要求的约束。

通常静态时序的起点定义有两种,一个是时序单元的clock引脚,另一个是input port。

终点也定义为两种:一个是触发器的D端,一个是output port

上面这个图中有四条路径:

path1:input port到一个触发器的D端

path2:clk pin的起点到触发器的D端

path3:clk pin到output port

path4:input port到output port

现在的SOC基本是全局异步,局部同步的。(多个时钟)

时钟域(clock domains)

首先要根据时钟域区分哪些是同步电路哪些是异步电路。局部的同步电路可以用PT或者DC做静态时序分析。跨时钟域的电路要做一些约束(告诉工具这部分是不做静态时序分析的)。

set_false_path -from [get_clocks USBCLK] -to [get_clocks MEMCLK]

静态时序分析更多的是指定的操作环境。PVT(Process、Voltage、Temperature,工艺、电压和温度)。

一般情况下,PVT分为三种,比较慢的,典型的,快的。通过最慢的和最快的分析整个电路在这些情况下是否能继续满足时序分析的要求。如果在极限可以满足,那么典型的情况也可以满足。一般在最慢的情况下检查setup,在最快的条件下检查hold。

通常高温、低电压确保延迟最差。即检查setup

如果是最小的低温和高电压,延迟值最小,即最快检查hold。

二、标准单元库

1、时序库的概述

部分工艺库的模型,lib格式的可以打开,db格式的不能打开。

2、非线性的延迟模型

输入端的上升对应输出端的下降。

输入端的下降对应输出端的上升。

通常延迟会随着输入的transition增加而增加。

标准单元的延迟模型分为线性和非线性的。

非线性延迟的模型是通过一个二维的查找表来实现的

3、

之前库基本是90%和10%,中间是80%。

而现在的基本是70%和30%。中间是40%。

用这个库想得到一个真实的值就必须给它乘上0.5

在建库(k库)的时候,会用到这些,低功耗设计,低电压域等,

4、时序的模型

主要看组合逻辑和时序逻辑cell的timing arcs(时序弧)有哪几种

ck到D

5、线延迟

互联线更多用的分布式的RC的树。

三、静态时序分析环境的配置

静态时序分析的环境是指定一个正确的约束,精确,才能指导静态时序分析对整个电路做一个全面的比较严谨的检查,最终才能确定最终的建立时间和保持时间真正的满足需求。

包括:时钟的建立,IO的约束,关于时序路径的一些特殊约束。

STA主要针对的是同步电路。

只能处理DUA里面的同步电路。

2、指定时钟的约束

(1)时钟的源点

(2)时钟的周期

(3)占空比(高电平比上整个时钟周期的比例)

(4)边缘翻转的时间

creat_clock -name SYSCLK -period 20 -waveform {0 5} [get_ports SCLK]

creat_clock -period 5 [get_ports CLK]

crat_clock -name BDYCLK -period 15 -wave {5 12} [get_ports GBLCLK]

时钟还有其他的误差,时钟偏斜,jitter等,可以通过clock_uncertainty来对这些进行一个估计

会让检查保持时间和建立时间更加严格。让时序更加稳健

如果是理想时钟的边沿,加上uncertainty,会让时钟沿提前。让电路更加稳健。

hold加上uncertainty会让数据更加严苛。

set_clock_uncertainty -setup 0.2 [get_clocks CLK_CONFIG]

set_clock_uncertainty -hold 0.05 [get_clocks CLK_CONFIG ]

set_clock_uncertainty -from VIRTUAL_SYS_CLK -to SYS_CLK -hold 0.05

set_clock_uncertainty -from VIRTUAL_SYS_CLK -to SYS_CLK -setup 0.3

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -hold 0.05

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -setup 0.1

clock skew时钟偏差

clock delay时钟延迟

clock jitter 时钟抖动

clock latency

比如:PLL出发到定义的节点之间的叫source latency

从定义的时钟节点到驱动的触发器这里叫network latency

set_clock_latency 0.8 [get_clocks CLK_CONFIG]

set_clock_latency 1.9 -source[get_clocks SYS_CLK]

set_clock_latency 0.851 -source -min [get_clocks CFG_CLK]

set_clock_latency 1.322 -source -max [get_clocks CFG_CLK]

时钟的latency的分析根据时钟树的节点。

生成时钟

一个主时钟生成多个时钟

主时钟是CLKP。CLKDIV2是CLKP的2分频,它的源时钟是CLKP。

creat_clock -name CLKP 10 [get_pins UPLL0/CLKOUT]

#creat a master clock with name CLKP of period 10ns

#with 50% duty cycle at the CLKOUT pin of the PLL

creat_generate_clcok -name CLKPDIV2 -source UPLL0/CLKOUT -divied_by 2 [get_pins UFF0/Q]

约束输入输出路径

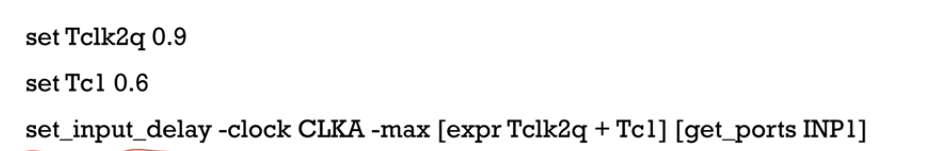

set_input_delay -clock CLKA -max 1.5 [get_ports INP1]

设置最大和最小值,分别对建立时间和保持时间各自一个比较严苛的约束来检查,最终得到一个比较稳健的电路。

creat_clock -period 15 -waveform {5 12} [get_ports CLKP]

set_input_delay -clock CLKP -max 6.7 [get_ports INPA]

set_input_delay -clock CLKP -min 3.0 [get_ports INPA]

set_output_delay -clock CLKQ -max 5.0 [get_ports OUTB]

creat_clock -period 100 -waveform {5 55} [get_ports MCLK]

set_input_delay 25 -max -clock MCLK [get_ports DATAIN]

set_input_delay 5 -min -clock MCLK [get_ports DATAIN]

set_output_delay 20 -max -clock MCLK [get_ports DATAOUT]

set_output_delay -5 -min -clock MCLK [get_ports DATAOUT]

路径组

终点属于哪个时钟就输入哪个时钟的path。

指定端口的时候还会有一些额外属性。

对于input这些属性主要包括:

(1)set_drive

(2)set_driving_cell

(3)set_input_transition

对于output要指定以下属性:

set_load

100这个值越小,驱动能力越强

可以通过库中的参数来设置

output 的负载默认是0(理想)。

DRC(Design Rule Checks)

通常约束的比库要求的小一点,这样时序会更加严苛点。

虚拟时钟

虚拟时钟跟其他design无关,主要用来静态时序的参考来指定input或output相关的一个时钟。

creat_clock -name VIRTUAL_CLK_SAD -period 10 -waveform {2 8}

creat_clock -name VIRTUAL_CLK_CFG -period 8 -waveform {0 4}

creat_clock -period 10 [get_ports CLK_CORE]

set_input_delay -clock VIRTUAL_CLK_SAD -max 2.7 [get_ports ROW_IN]

set_output_delay -clock VIRTUAL_CLK_CFG -max 4.5 [get_ports STATE_O]

Refining the Timing Analysis

(1)set_case_analysis

(2)set_disable_timing

(3)set_false_path

(4)set_multicycle_path

以上四条可以让静态时序变得更精细化。

(1)set_case_analysis主要是用来控制芯片中所加的扫描链的工作情况,正常情况下,扫描链不工作。

set_case_analysis 0 TEST

set_case_analysis 0 [get_ports {testmode[3]}]

set_case_analysis 0 [get_ports {testmode[2]}]

set_case_analysis 0 [get_ports {testmode[1]}]

set_case_analysis 0 [get_ports {testmode[0]}]

(2)set_disable_timing说明这不是一条时序路径,

(3)set_flase_path说明这是一条伪路径,用于跨时钟域的数据,异步电路,定义为伪路径不去分析。

(4)set_multicycle_path电路在运行的时候,两个寄存器之间的组合逻辑非常慢,一个周期肯定不够,就需要设置多个周期路径约束。(写RTL的时候就要考虑好)