视频网址https://www.iccollege.cn/study/unit/2389.mooc

一、 TCL语言入门

置换

TCL解释器运用规则把命令分成一个个独立的单词,同时进行必要的置换。

TCL的置换分为三类:

(1)变量置换$

(2)命令置换[]

(3)反斜杠置换\

变量置换

用$表示变量置换,TCL解释器会认为 $后面的为变量名,将变量置换置换成它的值。

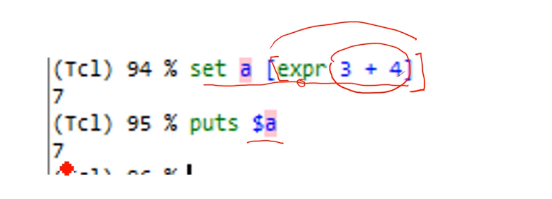

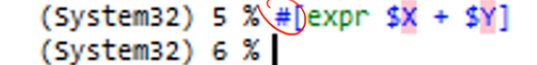

命令置换

用[]表示命令置换,[]内是一个独立的TCL语句

expr指的是求值。这条命令的意思就是给a变量赋值,结果就是3+4

反斜杠置换

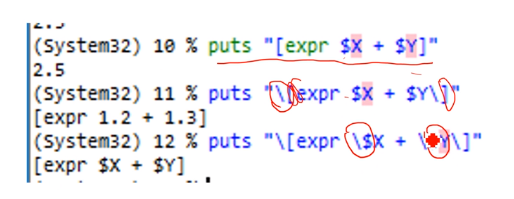

用\表示反斜杠置换,换行符,空格,[,$等被TCL解释器当作特殊符号对待的字符,加上反斜杠之后变成普通字符。

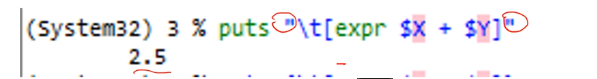

用\t表示TAB

用\n表示换行符

“”TCL解释器对双引号中$和[]符号会进行变量置换和命令置换。

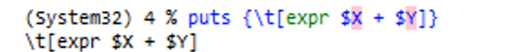

而在{}花括号中,所有的特殊字符都将变成普通字符,TCL解释器不会对其作特殊处理。

# 表示注释

变量、数组、列表

变量

变量就是某个容器的名称,可以存储一个值。变量的名称在程序运行期间保持不变,但是变量的值通常会不断改变。

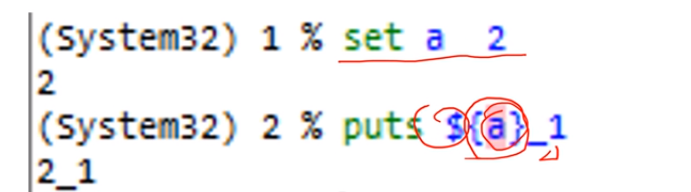

定义为: set 变量名 变量值

取值: $变量名

一定要注意这个{},只有这样puts才不会把a_1当成一个整体,只会把a,单独当成一个变量。这样的就可以实现为将变量打印为2_1

数组

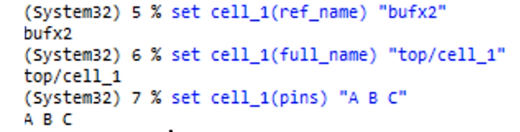

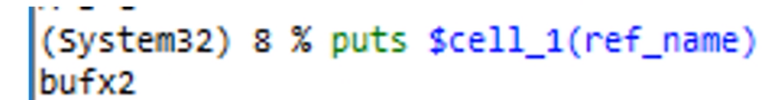

数组:TCL数组可以存储很多值,通过元素名来进行检索。类似于某件事务(数组名)几种不同属性(元素名),每一种属性都有其独立的值。

定义: set 数组名 (元素名) 值

取值: $数组名 (元素名)

使用array指令获取数组信息。

使用array size可以获取数组中元素的个数

使用array names可以获取数组里面的元素名

列表

列表是标量的有序集合。

定义 : set 列表名{元素1 元素2 元素3}

取值:使用$列表名

列表指令-concat

语法格式 : concat 列表1 列表2

功能: 将列表1和列表2合并

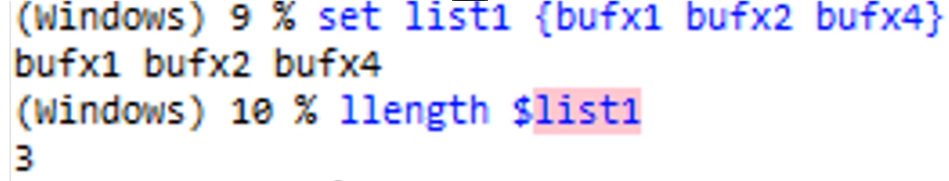

列表指令-llength

语法格式:llength 列表

功能:返回列表中的元素个数

这里的方括号[],是一个置换

列表指令-lindex

语法格式:lindex 列表n

功能: 返回列表中第n个元素(从0开始计数)

先通过llength命令得出,这个列表中有多少个元素

再通过expr这个求值指令让元素数量减一(这里的[]是命令置换)

最后通过index去返回最后一个元素

列表指令-lappend

语法格式:lappend列表 新元素

功能:列表末尾加入新元素

在列表末尾追加的列表会被当做一个整体。

可以先用lindex选取最后一个被当做整体的列表,再对这个选取出来的列表选取自己想要的元素。

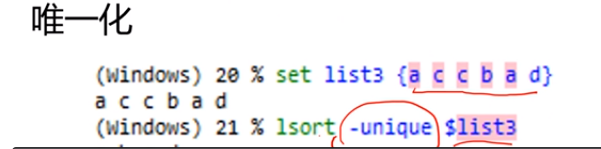

列表指令 -lsort

语法格式: lsort 开关 列表

功能: 将列表按照一定规则排序

开关 : 缺省时默认按照ASCII码进行排序

- -real 按照浮点数值大小排序

- /-unique唯一化,删除重复元素

先将列表进行按照浮点数大小进行排序,再用lindex选择该列表的第一个元素。

运算

数学运算指令-expr

语法格式: expr 运算表达式

功能:将运算表达式求值

控制流

控制流-if

语法格式:

注意:上面的脚本语句的"{"一定要写在上一行,因为如果不这样,TCL解释器会认为if命令在换行符处已结束,下一行会被当成新的命令,从而导致错误。

循环指令-foreach

语法格式: foreach 变量 列表 循环主体

功能: 从第0个元素开始,每次按顺序取得列表中的一个元素,将其值赋值给变量,然后执行循环主体一次,直到列表的最后一个元素。

将列表中第0个元素3赋值给变量i,进入循环打印i值为3.

将列表中第1个元素2赋值给变量i,进入循环打印i值为2.

将列表中第2个元素1赋值给变量i,进入循环打印i值为1.

退出循环

循环控制指令-break

语法格式:break

功能:结束整个循环过程,并从循环中跳出

循环控制语句-continue

语法格式:continue

功能:仅结束本次循环

循环控制指令-while

语法格式:while 判断语句 循环主体

功能:如果判断语句成了(返回值非0),就运行脚本,直到不满足判断条件停止循环,此时while命令中断并返回一个空字符串。

循环控制命令-for

语法格式:for参数初始化 判断语句 重新初始化参数 循环主体

功能:如果判断语句返回值非0就进入循环,执行循环主体后,再重新初始化参数。然后再进行判断,直到判断语句返回值为0,循环结束。

过程函数

过程函数-proc

语法格式:proc 函数名 参数列表 函数主体

功能:类似C语言中的函数,即用户自定义功能,方便多次调用

全局变量与局部变量

全局变量:在所有过程之外定义的变量

局部变量:对于在过程中定义的变量,因为它们只能在过程中被访问,并且当过程退出时会被自动删除。

指令global,可以在过程内部引用全局变量

正则匹配

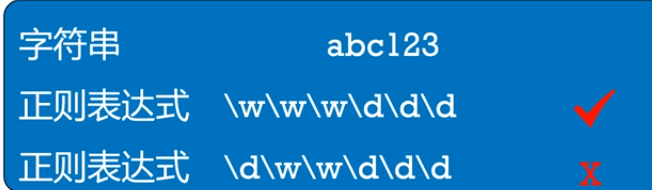

定义:正则表达式是一种特殊的字符串模式,用来去匹配符合规则的字符串。

正则表达式的\w,用来匹配一个字母,数字,下划线

正则表达式的\d,用来匹配一个数字

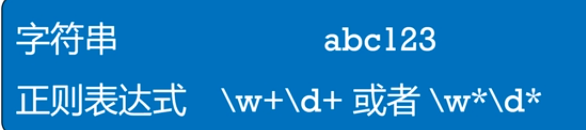

正则匹配–量词

\w\w\w\d\d\d这种写法过于繁琐,可以用代替重复的量词进行表示。

在TCL中常用以下三种量词

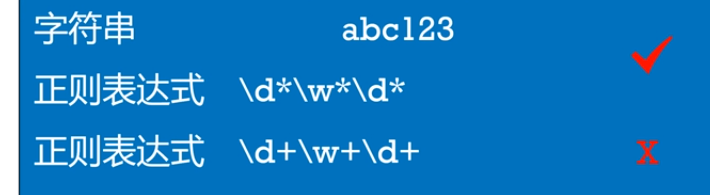

* 和 +的区别是:* 可以是零次,+至少是一次。

* 和 +的区别是:* 可以是零次,+至少是一次。

? 表示零次或者一次匹配

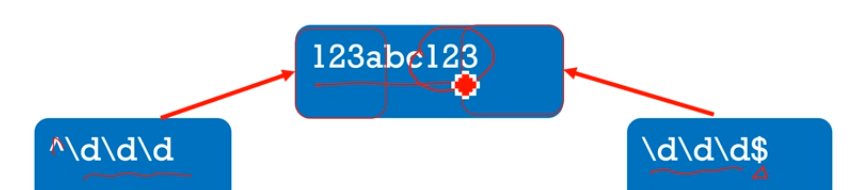

正则匹配–锚位

锚位,用来指示字符串当中的开头和结尾的位置,使我们能够匹配到正确的字符。

正则匹配—其他字符

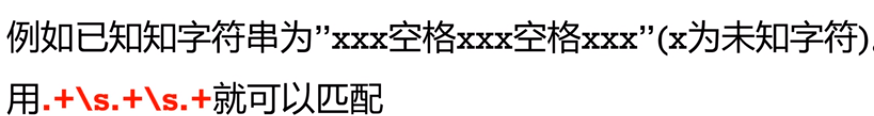

常用的其他字符还有\s和 .

\s表示空格

. 表示任意一个字符

不确定具体是什么字符就可以用 . 表示

正则匹配指令—regexp

语法格式:regexp ? switches ? exp string? match Var?subMatchVar subMatchVar…?

功能:在字符串中使用正则表达式匹配

switches:

—nocase将字符串中的大写都当成小写看待

exp 正则表达式

string 用来进行匹配的字符串

matchstring 表示用正则表达式匹配的所有字符串

sub1表示正则表达式中的第一个子表达式匹配的字符串

sub2表示正则表达式中的第二个子表达式匹配的字符串

如何匹配字符串“abc456”

regexp {\w+\d+} "abc456"

如何匹配一个以数字开头并且以数字结尾的字符串?

regexp {^\d .* \d$} "1 dfsal 1"

捕获变量

文本处理

TCL处理文本在工作中十分常用

主要掌握以下三个指令:

open

gets

close

open

语法格式: open 文件 打开方式(打开方式r表示读模式,w表示写模式)

功能:打开文件

gets

语法格式:gets fileld 变量名

功能:gets读fileld标识的的文件的下一行,并把该行赋值给变量,并返回该行的字符数(文件尾返回-1)

close

语法格式: close fileid

功能: 关闭文件

#现有文本file.txt其内容如下。请写一个TCL脚本求出所有的Slack值之和

set sum 0

set INFILE [open file.tx r]

while {[gets $INFILE line] >=0}{

if{[regexp {^Slack\s+=\s+(-?\d+\.?\d+)}

$line total slack]}{

set sum [expr $sum + $slack]

}

}

close $INFILE

puts $sum

二、 TCL语言在EDA工具中的扩展与应用

综合软件中TCL的常见指令

语法格式:get_ports portsname

指令功能:返回design中对应的port object

语法格式:get_cells cellsname

指令功能:返回design中对应的cell的instance name object

语法格式:get_nets netsname

语法功能:返回design中的net的 object

语法格式: get_pins pinsname

指令功能:返回design中pin的object

三、使用TCL语言设计DC的自动化Flow

该过程无需人为操作,用户只需要输入一条shell启动指令就能完全自动化的完成整个综合过程。

具备普适性和可重用性。在综合不太的设计时,只需要修改参数配置文件中环境变量,不需要修改脚本。

自动化电路综合平台只需用户将待综合的设计和库文件收入一个文件夹,修改与待综合设计对象有关的环境变量参数,在命令窗口唤醒DC的指令,即自动化地完成综合过程,并得到综合后的网表文件好所需的报告。

运行流程:

①运行run.csh脚本,启动DC

#!/bin/csh-f

\rm -rf *.log *.svf alib* reports log work #清楚之前的文档

mkdir reports work #新建文件夹

dc_shell-xg-t -32bit -f./top.tcl #启动DC并运行top.tcl

②建立reports与work两个文件夹。reports文件夹用于存放生成的报告,work文件夹用于存放该平台运行过程中生成的文档、脚本

③启动顶层脚本top.tcl

④top.tcl按先后顺序启动各个子脚本,最终生成script.tcl

⑤DC读取script.tcl中的约束,最终完成综合,并将所有报告写入reports文件夹中。

top.tcl脚本运行机制:

(1)set_library.tcl:生成设定库文件和search path的约束

(2)read_design.tcl:生成读入设计文件的约束

(3)creat_clock.tcl:生成时钟源相关的约束

(4)set_rst.tcl:生成复位端口约束的约束

(5)set_io.tcl:生成输入输出端口的约束

(6)set_cons.tcl:生成保存门级网表,各种report文件的约束

注意:以上所有约束都自动生成,无需人为干涉;库文件、代码、时钟、复位、输入输出等均根据代码自动进行匹配,并生成相应的的约束;最终所有的约束都被写入script.tcl中,供DC读取,完成最终的逻辑综合过程。

功能:本模块用filelist.tcl脚本实现,遍历目标文件下的所有文件,并将扩展名为.v符号要求的文件完整路径输出到指定的文档,最终形成DC读取verilog代码的约束,写入script.tcl中。