指令存储器

我用的是vivado 2019.1其他版本应该差不多

1、建立工程

名字填你想要的,这里我填inst_rom,板卡目前随便选不影响仿真

32位存储,8KB相当于2048个存储单元每个4*2048=8K每个存储单元宽度32位

User ENA pin带有使能为ena

不勾选Primitives Output Register保证上升沿采集到的访存地址信号,不然多一个时钟周期。

Coe文件相当于初始化存储器内容

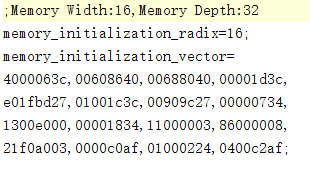

init.coe

;Memory Width:16,Memory Depth:32

memory_initialization_radix=16;

memory_initialization_vector=

4000063c,00608640,00688040,00001d3c,

e01fbd27,01001c3c,00909c27,00000734,

1300e000,00001834,11000003,86000008,

21f0a003,0000c0af,01000224,0400c2af;

Summary给出存储器类型、所消耗的Block Memory、读延迟、地址端口宽度

添加TextBeach文件

直接点ok,yes

inst_rom_tb.v

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/05/20 22:01:00

// Design Name:

// Module Name: inst_rom_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module inst_rom_tb();

reg clka,ena;

reg [10:0] addra;

wire [31:0] douta;

inst_rom uut(

.clka(clka), //input wire clka

.ena(ena), //input wire ena

.addra(addra), //input wire [10:0] addra

.douta(douta) //output wire [31:0] douta

);

initial begin

clka=0;ena=0;addra=0;

#100 ena=1;addra=1;

#50 addra =3;

#50 addra =6;

#50 addra =10;

#50 $finish;

end

always begin

#10 clka=~clka;

end

endmodule

可以看到ena不使能不好用,然后addra对应coe,比如地址1是00608540

到此指令存储器相当于设计结束了,接下来的数据存储器和它操作很像。

数据存储器

建一个data_ram工程(图略)

然后:

建立TB文件

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/05/20 22:43:52

// Design Name:

// Module Name: data_ram_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module data_ram_tb;

reg clka,ena;

reg [3:0] wea;

reg [10:0] addra;

reg [31:0] dina;

wire [31:0] douta;

data_ram uut(

.clka(clka), //input wire clka

.ena(ena), //input wire ena

.wea(wea), //inpur wire [3:0] wea

.addra(addra), //input wire [10;0] addra

.dina(dina), //input wire [31:0] dina

.douta(douta) //output wire [31:0] douta

);

initial begin

clka=0;ena=0;

#100 ena=1;wea=4'b1111;addra=0;dina=32'h12345678;

#100 wea=4'b1001;addra=0;dina=32'habcdef90;

#100 wea=4'b0000;addra=0;

end

always #10 clka=~clka;

endmodule

可以看到,100ns是全写,所以读出来是12345678,200ns是改1,4字节,所以变成了ab345690,然后300ns就是读出来了。