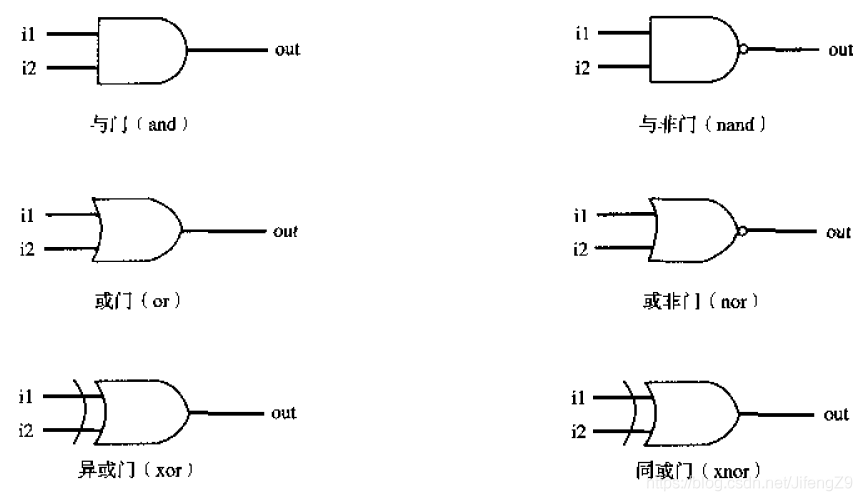

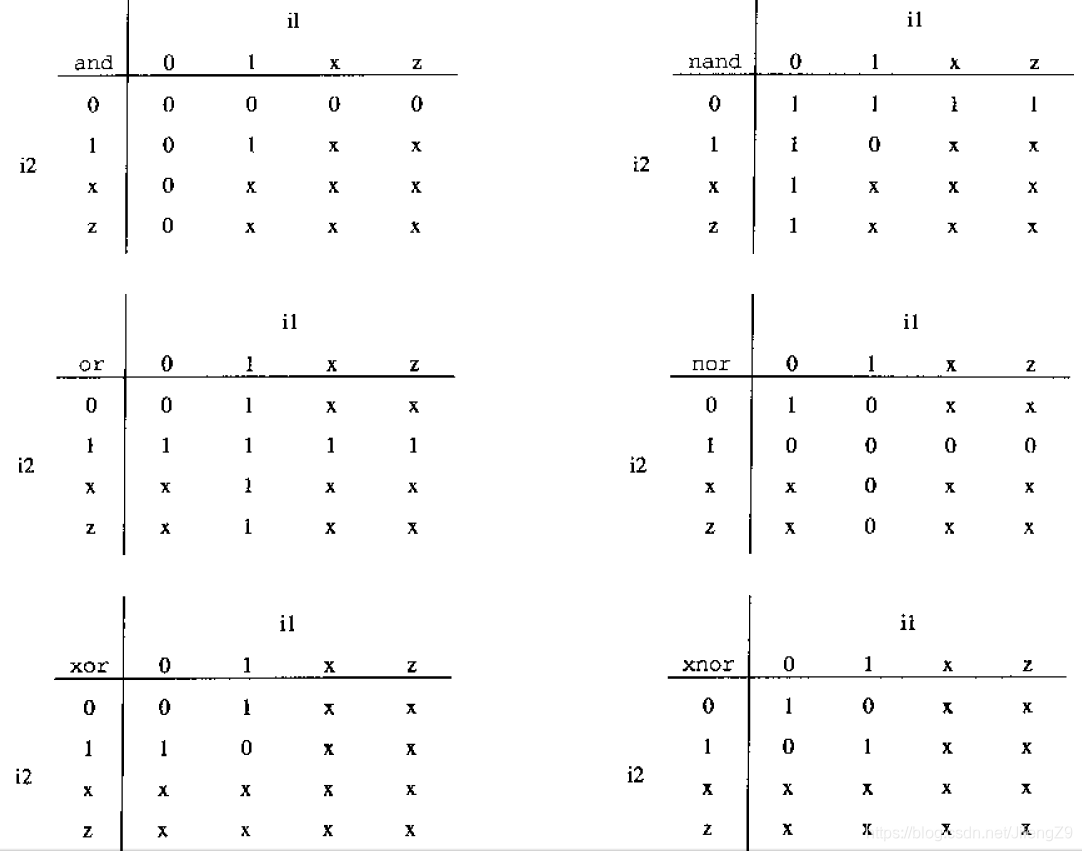

-门的类型:

-与门、或门:输出端口排在最前面,输入端口有多个,依次排在输出端口之后;

and a1(OUT, in1, in2, in3, in4);//类似这样

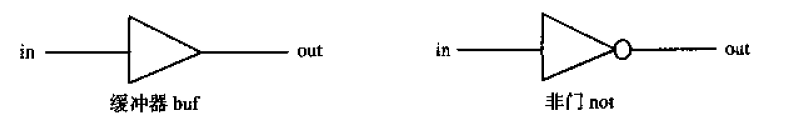

-缓冲器、非门:可以有多个输出端口,只有一个输入端口且必须是实例端口列表的最后一个;

buf b1(out, IN);//类似这样

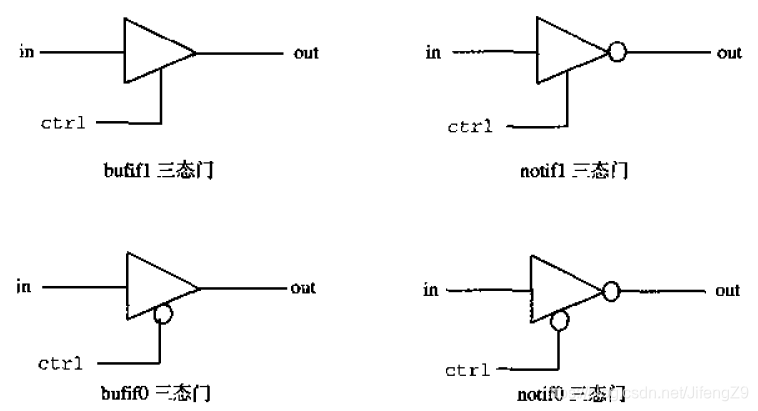

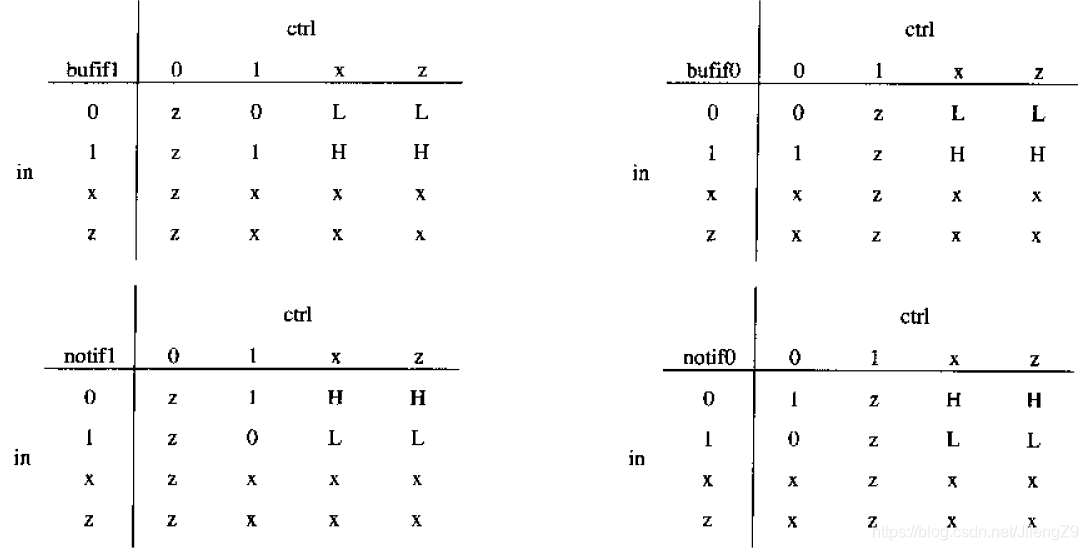

-带控制端的缓冲器、非门:控制信号有效是传递数据,无效时输出为高阻抗z

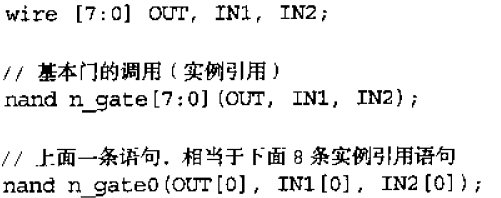

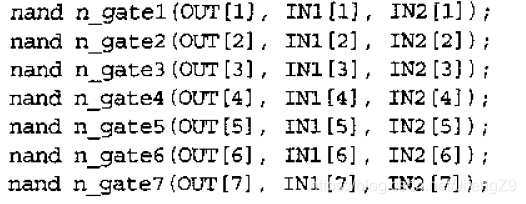

-实例数组:允许定义门实例数组

-门延迟:

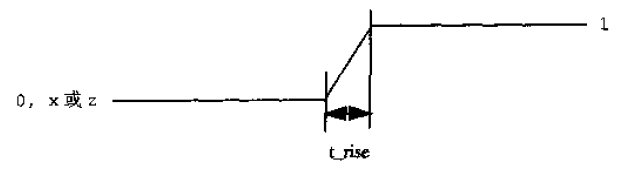

-上升、下降、关断延迟:

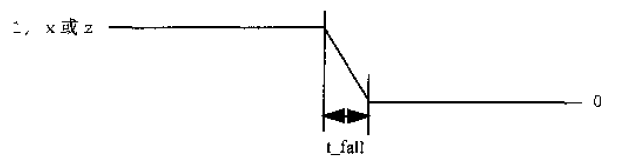

上升/下降延迟:输入变化时,门的输出从0、x、z变化为1或是从1、x、z变化为0所需的时间:

关断延迟:门的输出从0、1、x变化为高阻抗z所需的时间。

如果变化到不确定值,则所时间为以上三种延迟中值最小的那个。

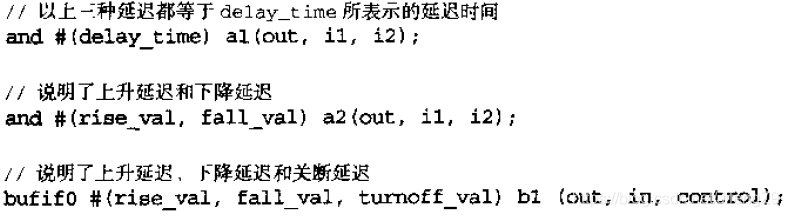

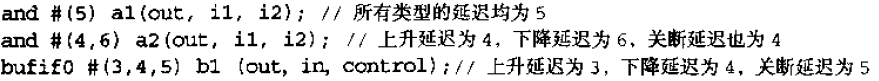

若用户指定一个延迟值,所有类型延迟均为此值;若指定两个值,则分别为上升和下降延迟,其中小者为关断延迟;若指定三个值,则分别为上升、下降、关断延迟;若没有指定,默认延迟值均为0。

-最小、典型、最大延迟

结合实际工艺,真实器件的延迟值是在某一范围内波动,设计者可以预期逻辑门所具有的最小、最大、典型延迟。

-门级设计步骤:

1、画出电路的逻辑图;

2、用门级原语将逻辑图转化为Verilog语言的门机描述;

3、编写激励模块对其进行仿真并观察输出,确认功能是否符合设计。