这篇文件记录,FPGA的3种建模方式及基本的Verilog HDL语法,内容会根据学习进度,不断更新。

一、FPGA的3种建模方式

A、数据流建模(assign)

在数字电路中,信号经过组合逻辑时会类似于数据流动,即信号从输入流向输出,并不会在其中存储。当输入变化时,总会在一定时间以后体现在输出端同样,我们可以模拟数字电路的这一特性,对其进行建模,这种建模方式通常被称为数据流建模1.1、是使用连续赋值语句(assign)对电路的逻辑功能进行描述,该方式特别便于对组合逻辑电路建模

1.2、连续驱动,连续赋值语句是连续驱动的,也就是说只要输入发生变化,都会导致该语句的重新计算。

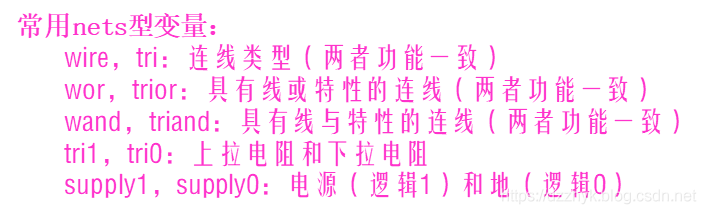

1.3、只有线网型的变量才能在assign语句中被赋值

扫描二维码关注公众号,回复: 16225688 查看本文章

1.4、因为assign语句中被赋值的变量,在仿真器中不会存储其值,所以该变量必须是线网(Nets)类型,不能是寄存器(reg)类型

1.5、线网类型的变量,可以被多重驱动,也就是说可以在多个assign语句中驱动同一个net<

Day6 FPGA三种建模方式区别及Verilog语法基础篇

猜你喜欢

转载自blog.csdn.net/qq_43416206/article/details/132255484

今日推荐

周排行