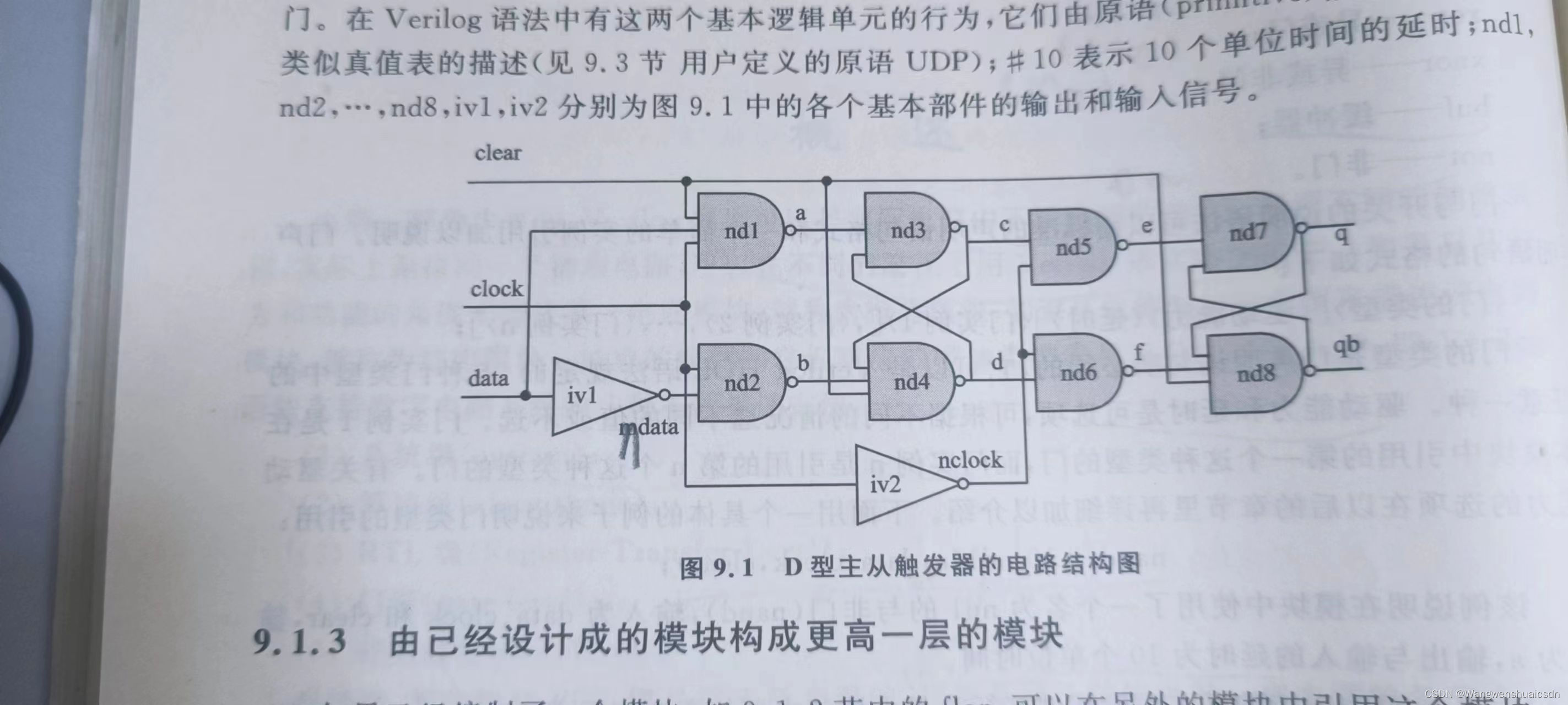

描述D型主从触发器模块的门级结构建模:

module flop(data, clock, clear, q, qb);

input data, clock, clear;

output q, qb;

// 批量定义门电路

nand #10 nd1(a, data, clock, clear),

nd2(b, ndata, clock),

nd4(d, c, b, clear),

nd5(e, c, nclock),

nd6(f, d, nclock),

nd8(qb, q, f, clear);

nand #9 nd3(c, a, d),

nd7(q, e, qb);

not #10 iv1(ndata, data),

iv2(nclock, clock);

endmodule

在该模块中,flop定义了模块名,设计上层模块时可以用模块名调用模块;

创建的电路模型图如下:

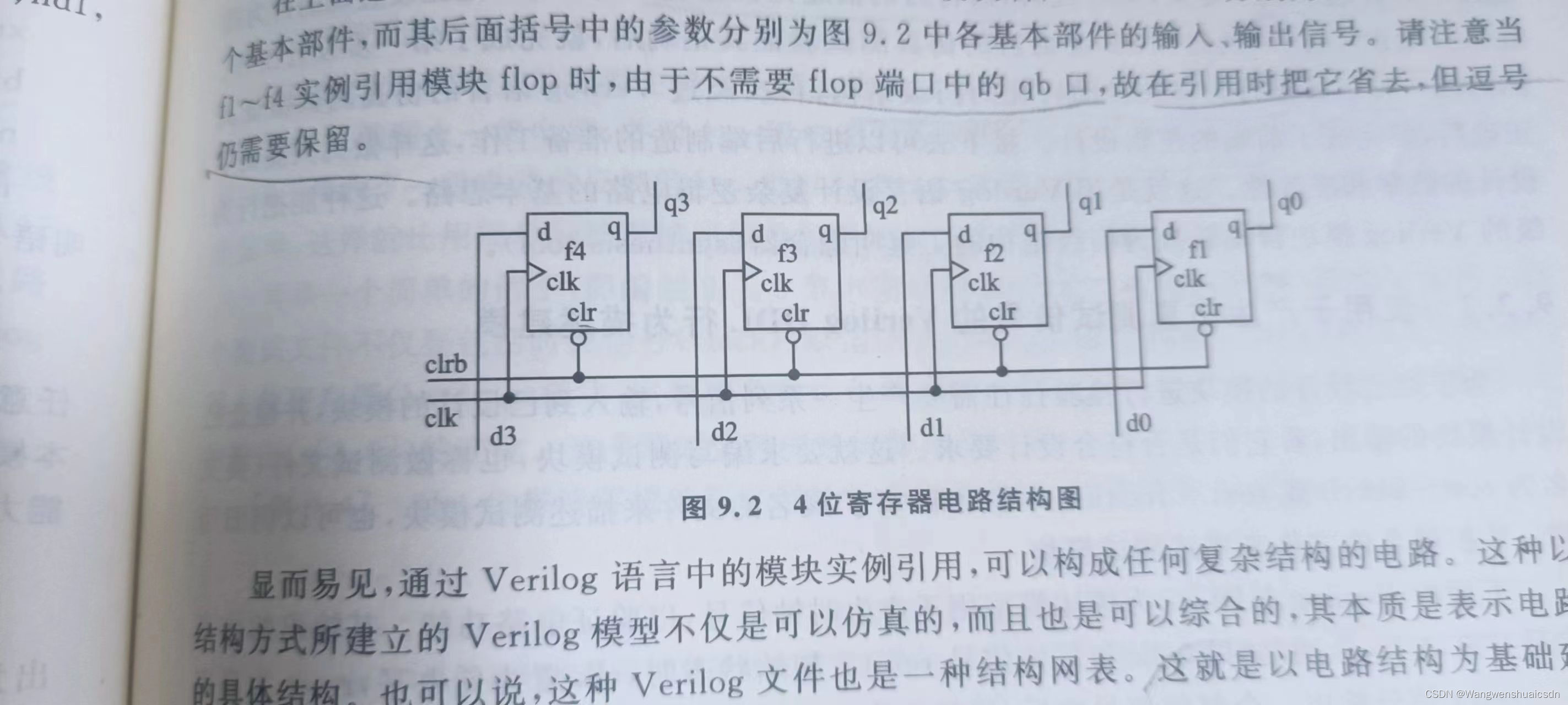

更高一级建模:

引用已编制好的模块进行实例化,用于行为级描述:

使用触发器组成带清零端的4位寄存器(hardreg.v)

`include "flop.v"

module hardreg(d, clk, clrb, q);

input clk, clrb;

input[3:0] d;

output[3:0] q;

flop f1(d[0], clk, clrb, q[0], ),

f2(d[1], clk, clrb, q[1], ),

f3(d[2], clk, clrb, q[2], ),

f4(d[3], clk, clrb, 1[3], );

endmodule

hardreg定义了模块名,f1,f2,f3,f4分别为基本D触发器,在实例引用模块flop时,由于不需要flop端口的qb口,故在引用时省去,但逗号仍保留。

通过模块之前的实例引用,可以构成任何复杂的电路,不仅可以用来仿真,也可以进行综合,本质是一种结构网表。

行为描述建模

用行为描述的方法来描述带清零端的4位寄存器:

module hardreg(d,clk,clrb,q);

input clk, clrb;

input[3:0] d;

output[3:0] q;

reg[3:0] q;

always@(posedge clk or posedge clrb)

begin

if (clrb)

q <= 0;

else

q <= d;

end

endmodule

门级描述表示的是电路结构,是电路布线的依据,设计的目的就是产生行为和功能描述的电路结构,电路结构看起来相当复杂,难以理解,而行为i的描述较为直观。

在设计时,可以用比较直观的行为描述来开始设计过程,通过仿真测试验证其正确性后,使用综合器将行为模块自动转化为门级结构,并再次经过仿真测试,便完成前端设计。

测试模块

四位带清零端的寄存器的测试文件(hardreg_top.v)

// start

`include "flop.v"

`inlcude "hardreg.v" //包含门级文件及行为描述文件

/*

如果仿真程序可以将有用的文件安排在一个项目中,只要底层模块经过编译;

并记录在编译的库中,可以不用包含在文件中。

*/

module hardreg_top; //顶层模块,没有输入输出的端口

reg clock, clearb; //为产生测试用的时钟和清零信号声明寄存器

reg[3:0] data; //为产生测试用的数据声明寄存器

wire[3:0] qout; //为观察输出信号需要从模块实例端口中引出线

`define stim #100 data = 4'b

event end_first_pass;

hardreg reg_3bit(.d(data), .clk(clock),.clrb(clearb), .q(qout));

/*

把本模块生成的测试信号data,clock,clearb输入实例reg_4bit中以观察输出信号qout。

实例reg_4bit实际上是已经设计好的模块hardreg;

实例引用的hardreg模块,根据包含文件的不同,可以是表示行为的模块,也可以表示结构的模块

*/

initial

begin

clock = 0;

clearb = 1;

end

always #50 clock = ~clock;

always@(end_first_pass)

clearb = ~clearb;

always@(posedge clock)

$display();

intial

begin

repeat(4)

begin

data = 4'b0000;

`stim 0001;//宏定义stim引用,等同于#100 data = 4'b0001;

`stim 0010;

`stim 0011;

...

`stim 1111;

#200->end_first_pass;//延时两百个单位,触发事件end_first_pass

end

$finish;

end

endmodule