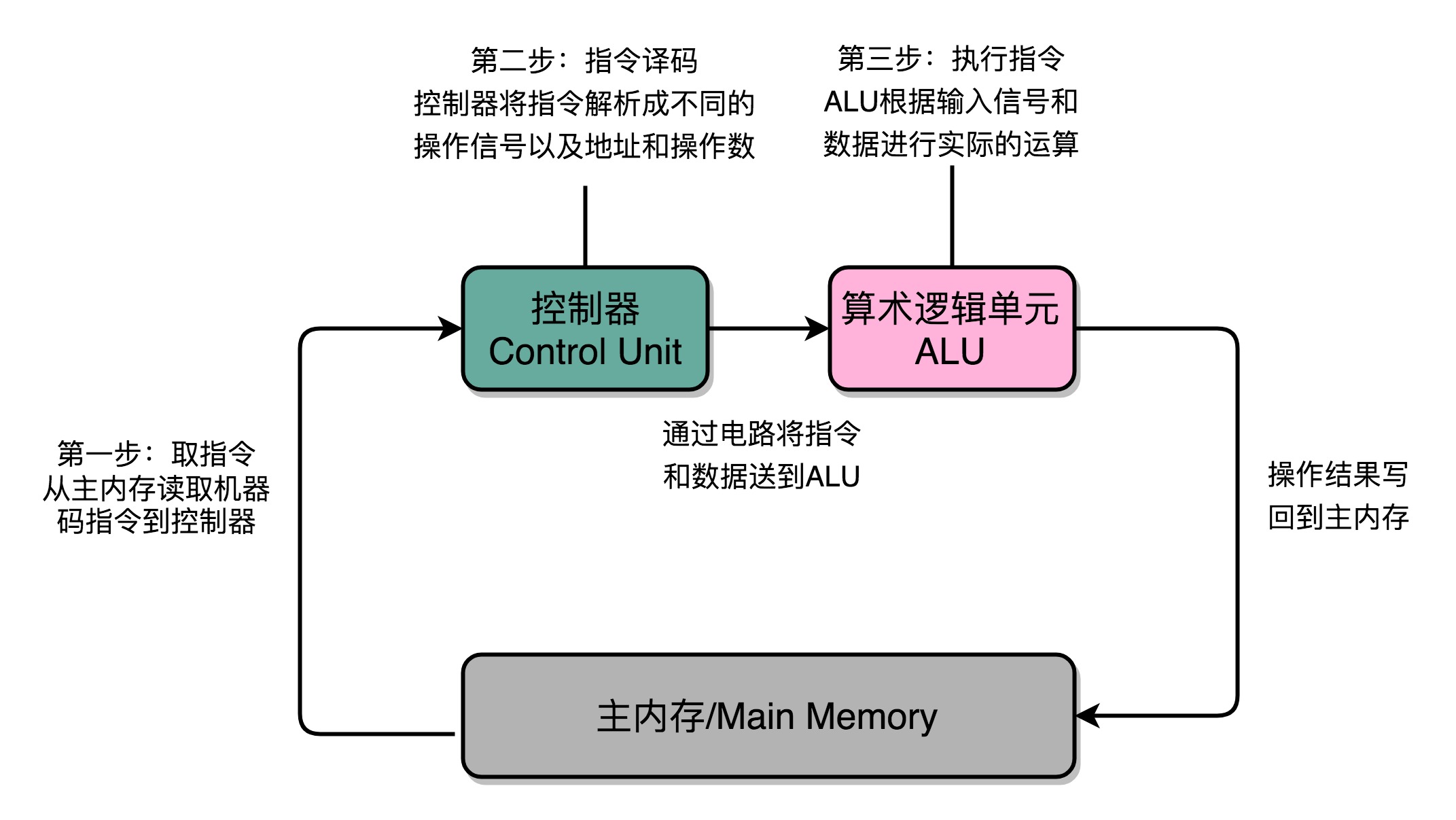

一、指令周期

计算机每条执行过程分解如下:

- Fetch:取指令,从PC寄存器取出指令地址,内存中取出指令,将取出的指令加载到指令寄存器,PC寄存器自增;

- Decode:指令译码,解析指令寄存器中指令,确定指令类型以及要操作的寄存器、数据、内存地址;

- Execute:指令执行,根据不同指令类型执行算数逻辑操作、数据传输、地址跳转;

- 不断重复1~3的过程;

以上 1~3 的取指令、指令译码、指令执行的一次循环称为一个指令周期;不同的过程由CPU中不同的组件执行:

- 指令放置在存储器

- PC寄存器和指令寄存器读取指令依赖控制器

- 指令解码依赖控制器;

- 指令执行由算数逻辑单元ALU完成,最简单的无条件跳转则可以由控制器完成;

三个周期极其关系:

- Instruction Cycle 指令周期,指令读取->指令译码->指令执行这个过程;

- Clock Cycle 时钟周期,即CPU主频时间;

- Machine Cycle 机器周期就是所谓CPU周期,通常是CPU从内存读取一次指令的最短时间,一个CPU周期通常由一个或多个时钟周期组成;

二、建立数据通路

数据通路由两类原件组成:

- 操作原件:就是ALU,输入不同电路信号输出特定结果;

- 存储原件:通用寄存器和状态寄存器;

通过数据总线将他们连接起来就构成了数据总线。

控制器:控制器的作用可以简单看作不断重复取指令然后指令译码再把译码结果交给ALU去执行。但实际的控制器相当复杂,所有CPU支持的指令都在控制器里面,现代Inter CPU已经支持超过2000个指令。

三、CPU需要的硬件电路

至少需要以下四类电路:

- 逻辑运算单元,它是无状态的电路,根据输入输出计算结果;

- 状态读写单元,能够存储状态,也就是寄存器,通常是锁存器和D触发器;

- 自动电路,可以按一定时钟频率发出信号,使得PC寄存器中指令地址不断自增,自动执行指令周期内的工作;

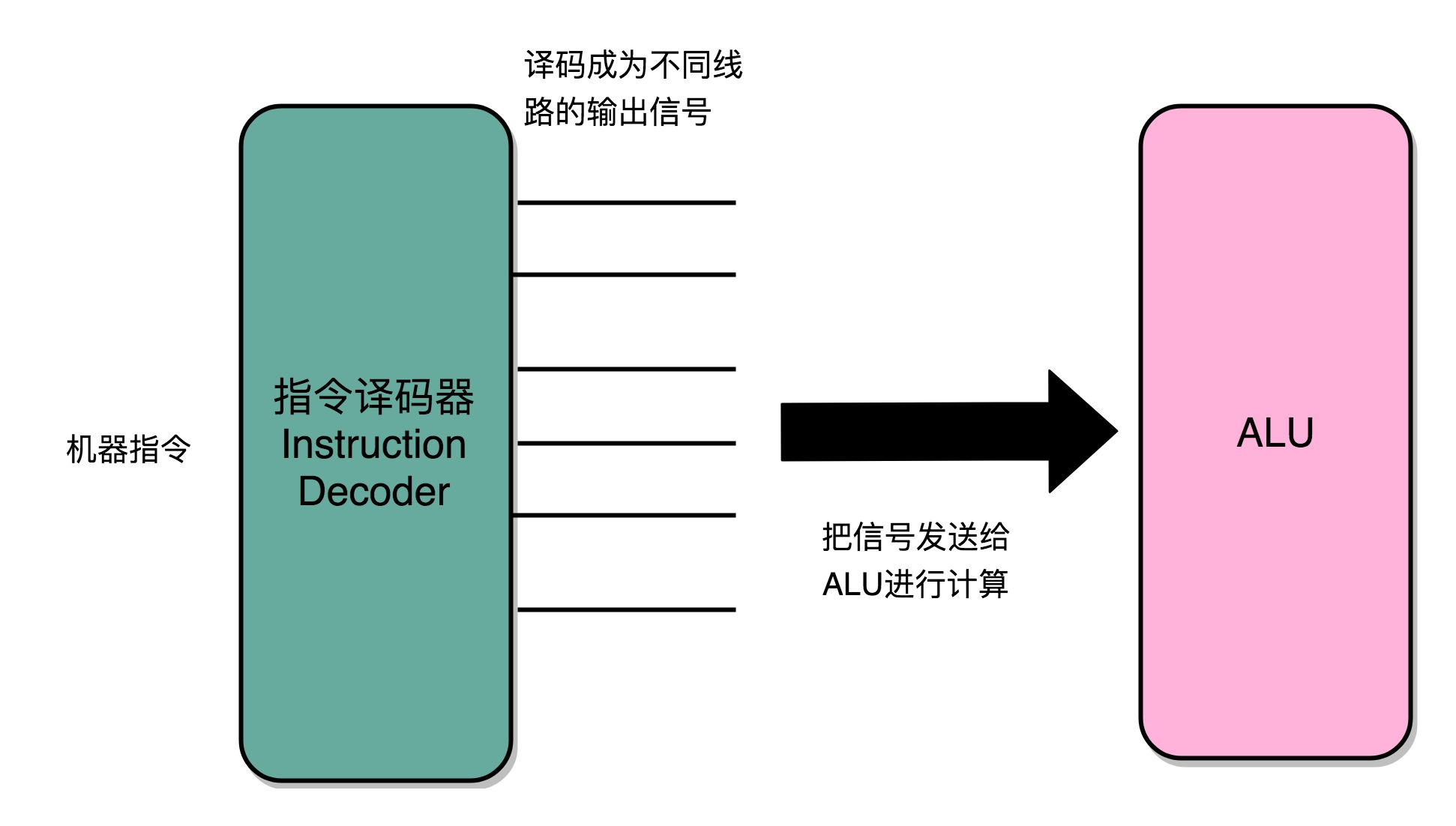

- 指令译码电路,进行指令译码和从内存读取指令和数据;

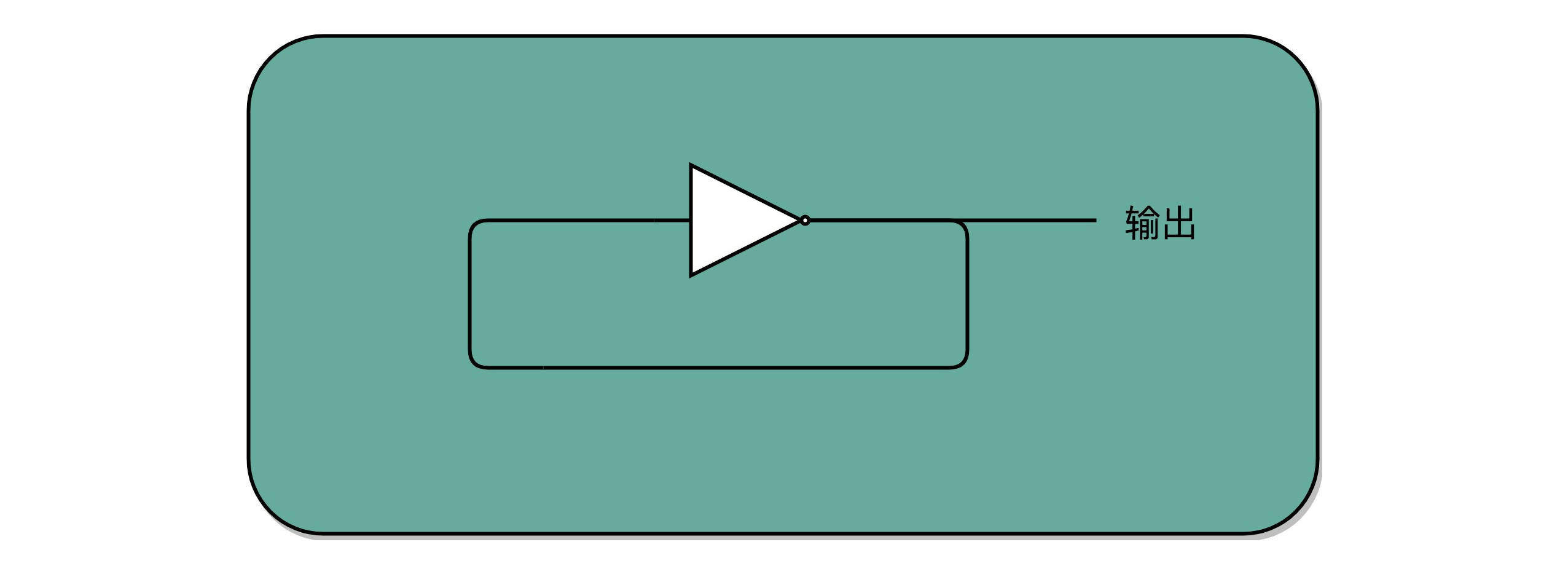

四、时钟信号的硬件实现

之前说过CPU的时钟信号是由晶体震荡器实现的,我们也可以通过一个反馈电路实现,所谓反馈器就是将电路的输出信号作为当前电路的输入信号。如下图:

开始时,A开关断开,B开关闭合,A开关打开后电磁铁使B开关断开,断开B开关后,电磁铁失去磁性,B开关弹回重新又通电,这样就能不但产生0、1信号的输出。这个反馈电路是实际一个反相器,用这个符号表示:

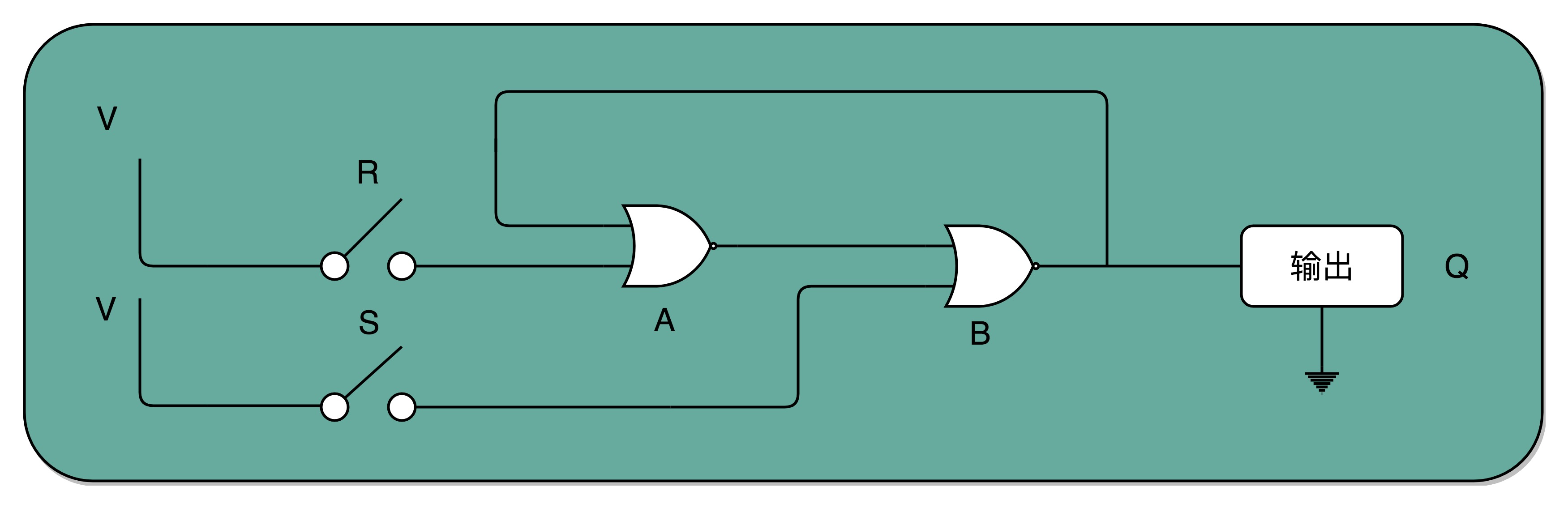

五、通过D触发器实现存储功能

利用反馈电路可以构造出有记忆功能的电路。这种记忆功能的电路可以用来构造计算机中的存储计算结果的寄存器以及存储器。

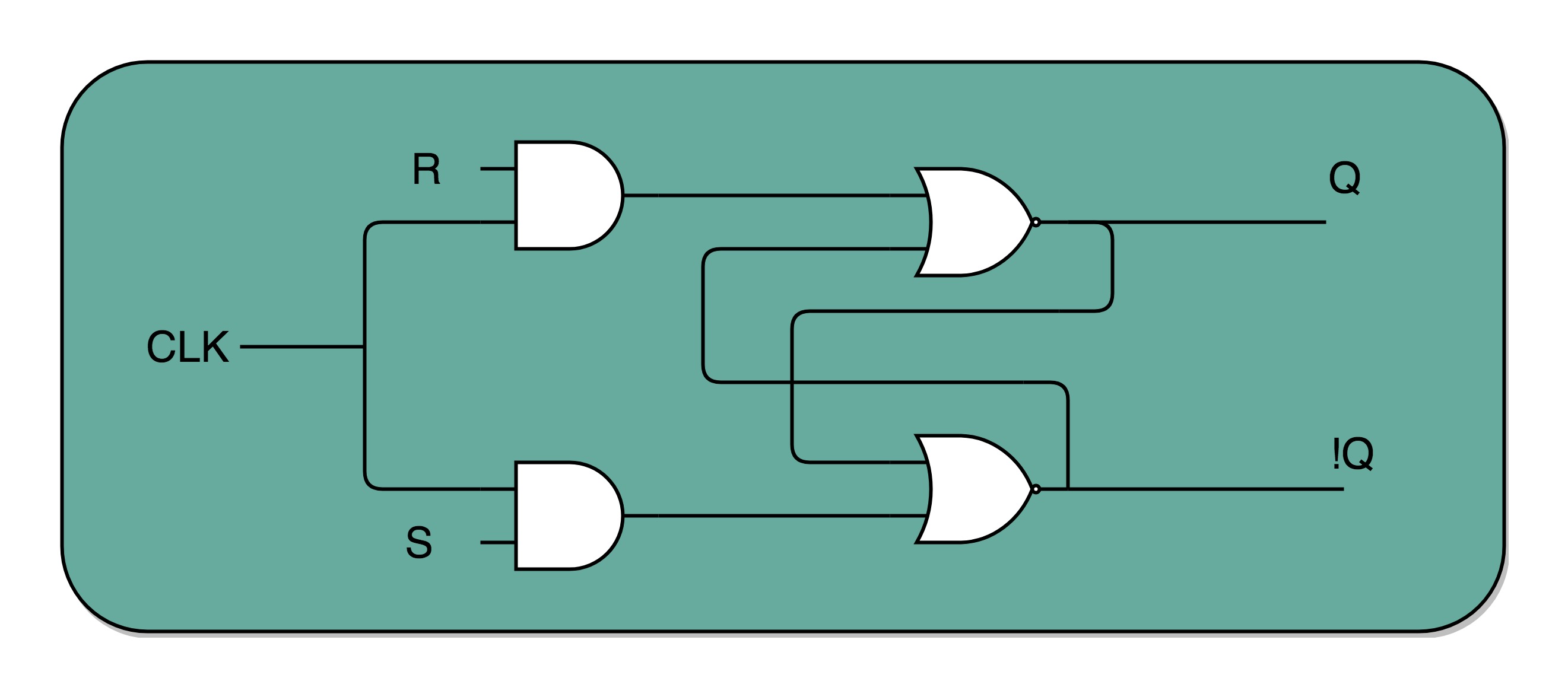

RS触发器:由两个或非门构成,或非门即全0输出1,其余输出0

- 一开始开关R和S都关闭也即是说输入都为0,此时A输出为1,B的输入为1、0因此整个电路输出为0;

- 当开关R合上时,A的输入为1、0,A输出为0,B的输入为0、0,因此整个电路输出为1;

- 此时再次断开R,A的输入为0、1,A输出为0,B输入为0、0,因此整个电路输出为1,也就是说虽然开关状态已经变成和第一步一样,但是输出仍然保持和第二步一样;

- 这时再去打开S,则B有一个输入必然为1,因此整个电路输出必为0;

以上电路,接通R输出为1,即使再次断开R,输出还是1,接通S,输出为0,即使再次断开,输出仍为0,这就是说,整个电路具有了记忆功能。

在RS触发器之上,在R和S之后增加两个与门,同时给这两个与门一个时钟信号作为电路输入,这是时钟电路低电平时,两个与门的输出结果都为0,此时R和S对整个电路输出结果没有影响,当时钟输入高电平时,电路输入的状态完全取决于R和S的状态,这样就用时钟信号控制了电路何时可以写入数据。

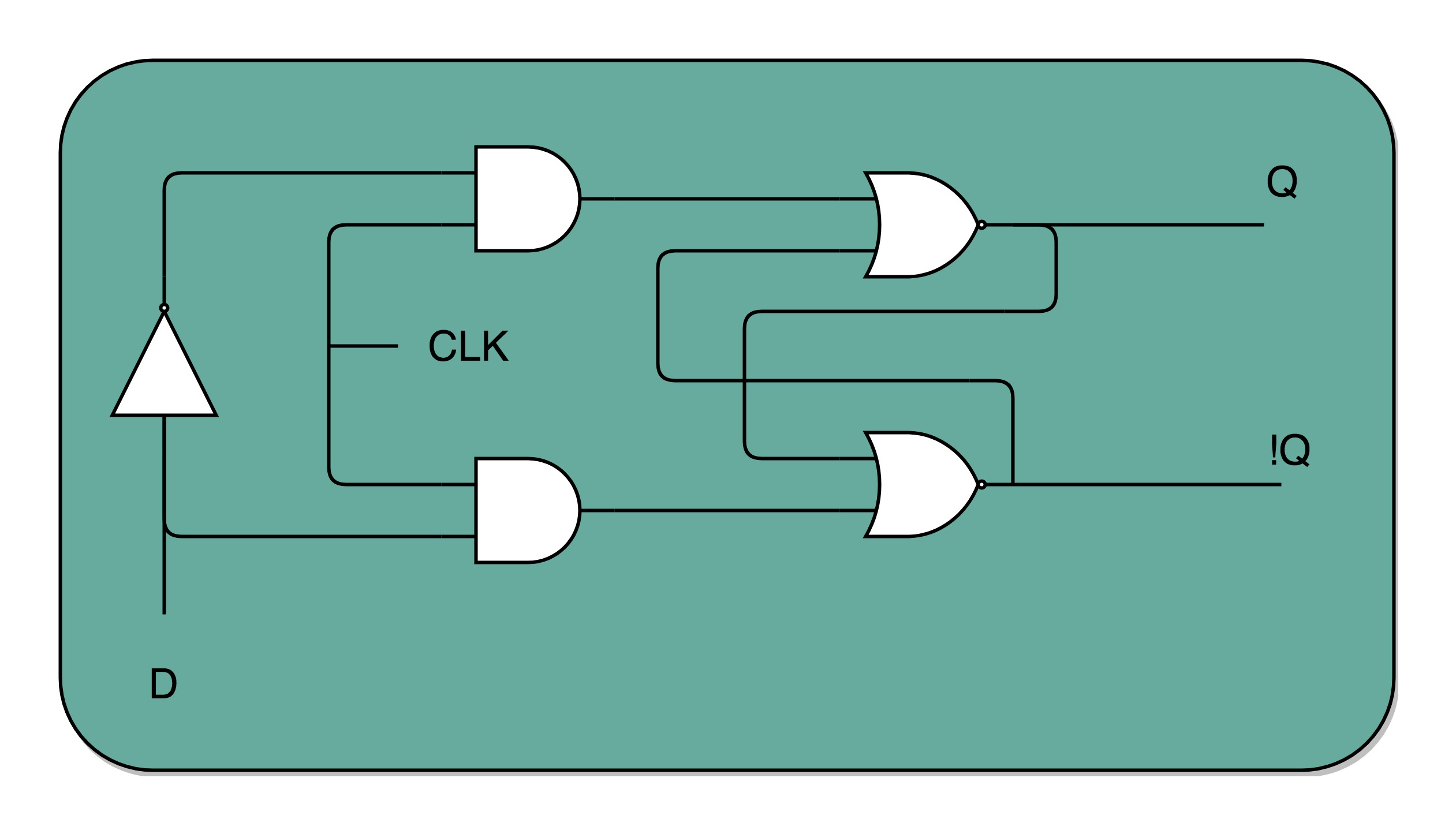

更进一步,我们将R和S使用一个反相器连接起来,就可以使用一个信号控制R和S的输入,这样我们就实现了一比特数据的存储,这就是D触发器。并列N个D触发器就可以得到一个N位的D触发器,使用一个时钟信号控制N位的读写,CPU的寄存器可以直接通过D触发器实现。

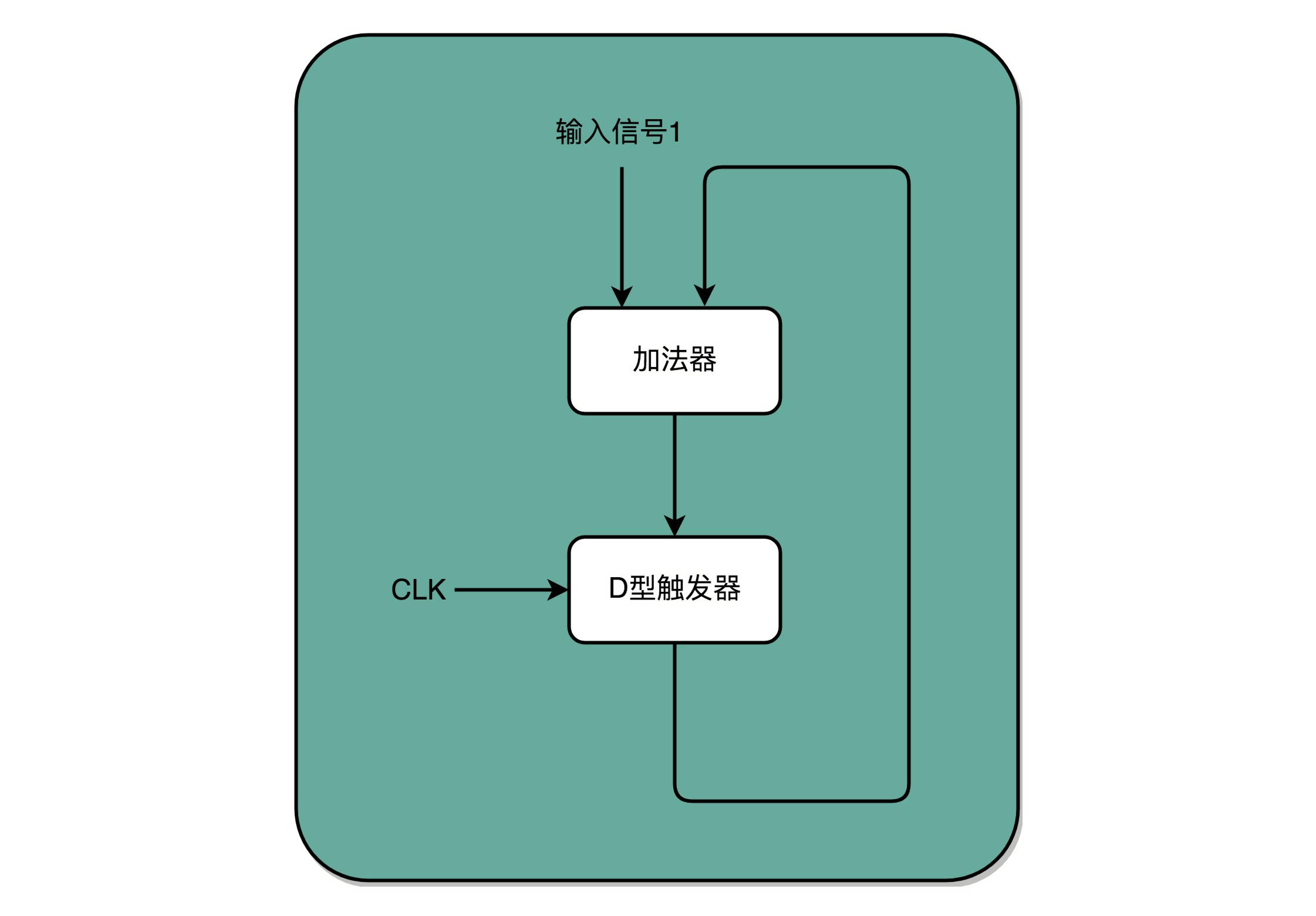

六、PC寄存器所需的计数器

PC寄存器还有一个名称叫做“程序计数器”,我们可以使用一个加法器和一个D触发器实现它:

- 加法器的两端,一端始终输入1,另一端来自触发器的输出;

- 触发器的输入分别是加法器的输出和时钟信号;

这样当每个时钟信号来临加法器就将触发器原本存储的值加一再写入存储器,这样就实现了一个随着时钟信号固定自增1的PC寄存器。

七、读写数据所需要的译码器

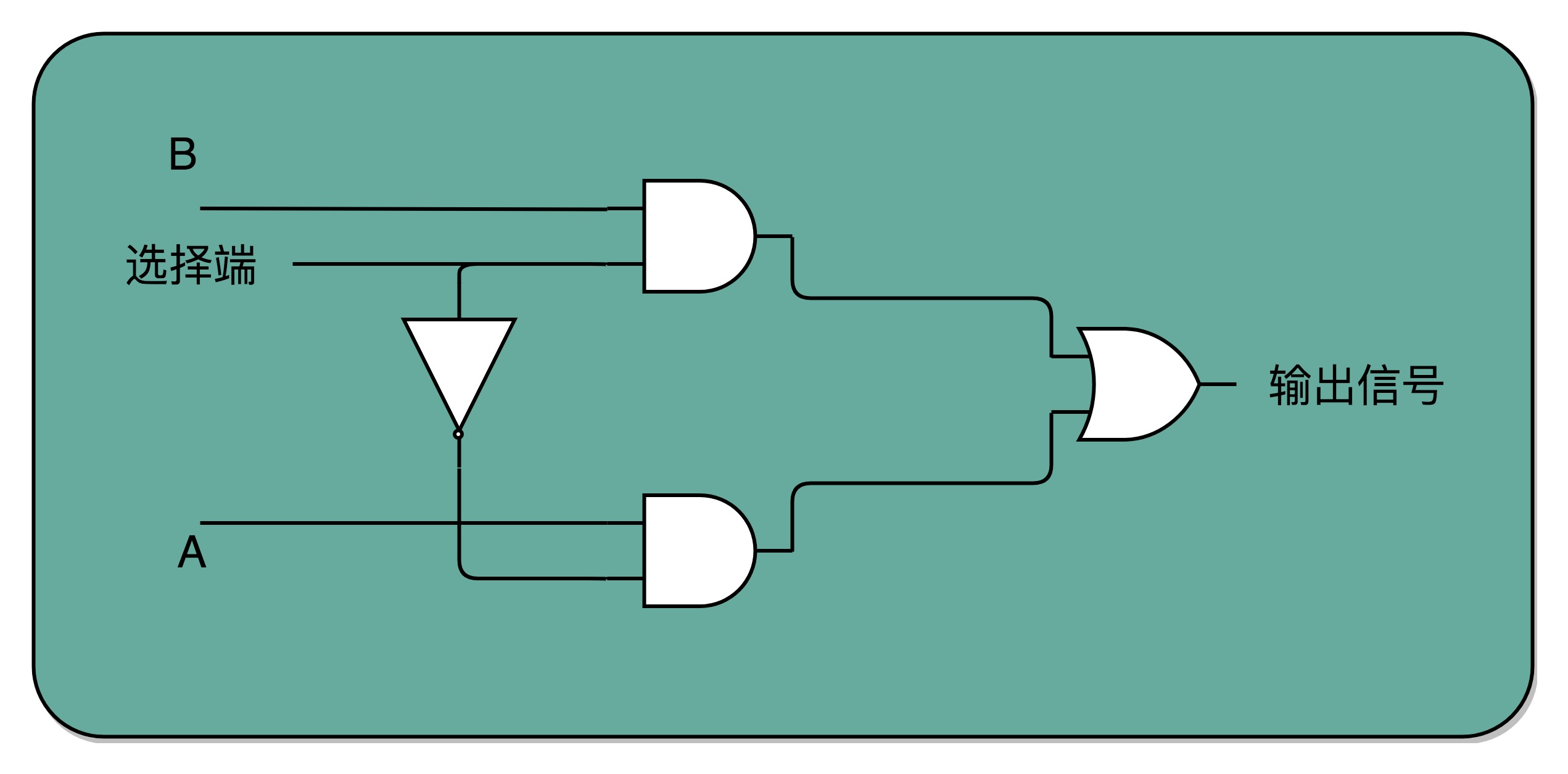

译码器要完成存储器的寻址功能,这里将其简化为从两个地址中选择一个地址的情况,即所谓的2-1选择器:

如图它由两个与门和一个或门以及一个反相器组成,通过反相器的输入就能够决定最终输出A端输入还是输出B端输入。一个反相器只有0/1两种状态,如果输入信号由三个不同的开关,就可以从2^3也就是8个地址中选一个了,这就是3-8译码器。64位CPU就意味着可以寻址2^64空间。译码器除了寻址功能外,还可以使用更复杂的电路实现指令译码操作,就是使用指令码通过译码器得到期望执行的指令。

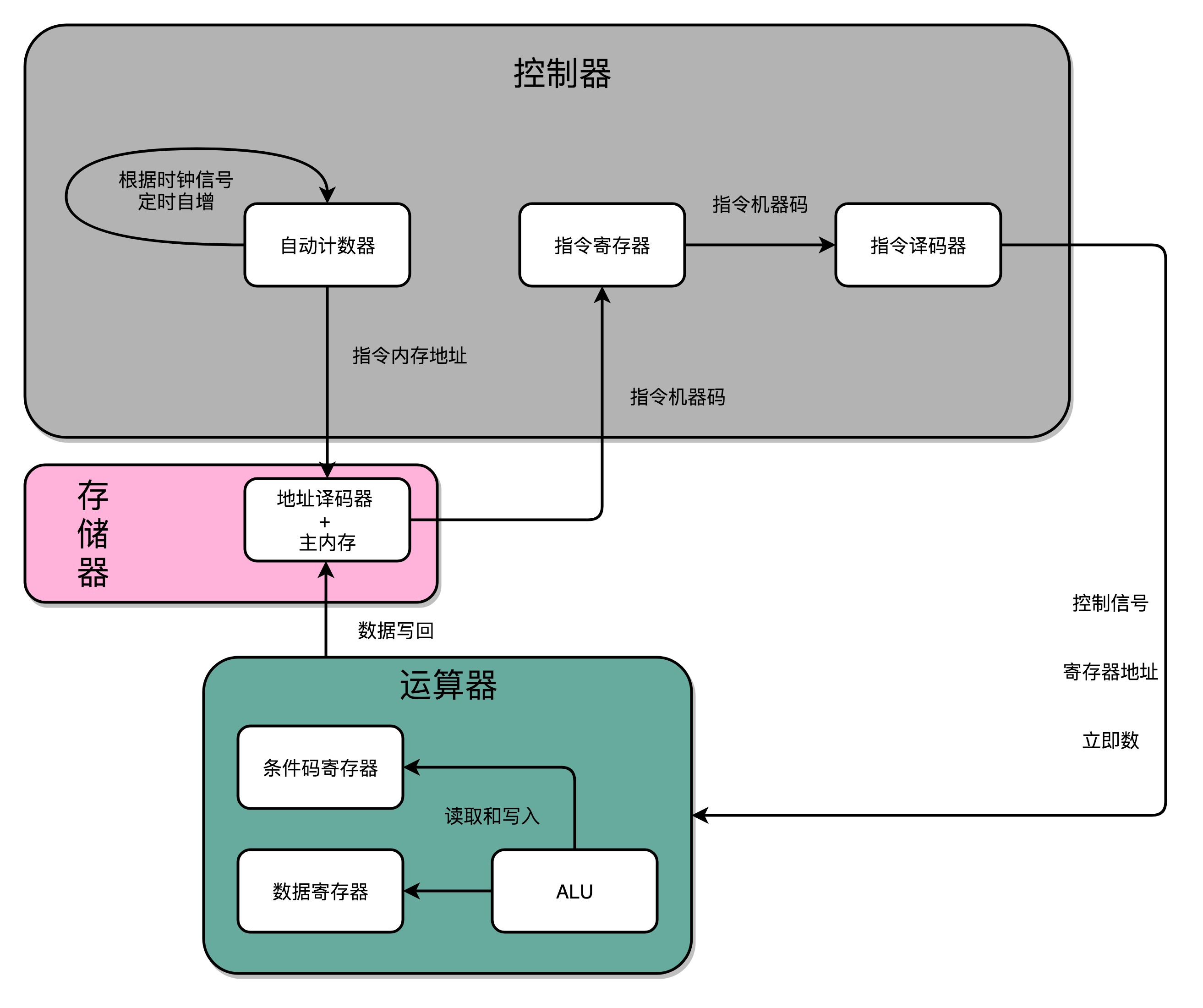

八、数据通路建立:构造一个CPU

由以上的过程,我们已经凑齐了组装一个CPU所需要的零件,现在看看怎么样将它们装配起来:

- 首先,自动计数器随着时钟频率不断自增。作为PC寄存器;

- 自动计数器后面是连接着译码器,译码器连接着大量的D触发器构成的内存;

- 自动计数器随着时钟频率不断自增,并从译码器中找到对应内存地址,取出对应的CPU指令;

- 读取出的指令会通过CPU时钟控制写入指令寄存器,它也由D触发器组成;

- 指令寄存器后跟着另一个译码器,这个译码器将指令转换成opcode和操作数;

- opcode和操作数对应输出线路连接ALU,进行何种算数和逻辑运算。并将结果写回D触发器构成的寄存器和内存中。

这样就构成了一个数据通路。