名人说:非学无以广才,非志无以成学。——诸葛亮

本篇笔记整理:Code_流苏(CSDN)

Last(在此处点击使用,直达文末)

Frist (在文末点击使用,返回文章首部)

★观前提示:本专栏笔记内容适合有一定的基础或复习时观看,内容如有错,还请大家评论指出!非常感谢!

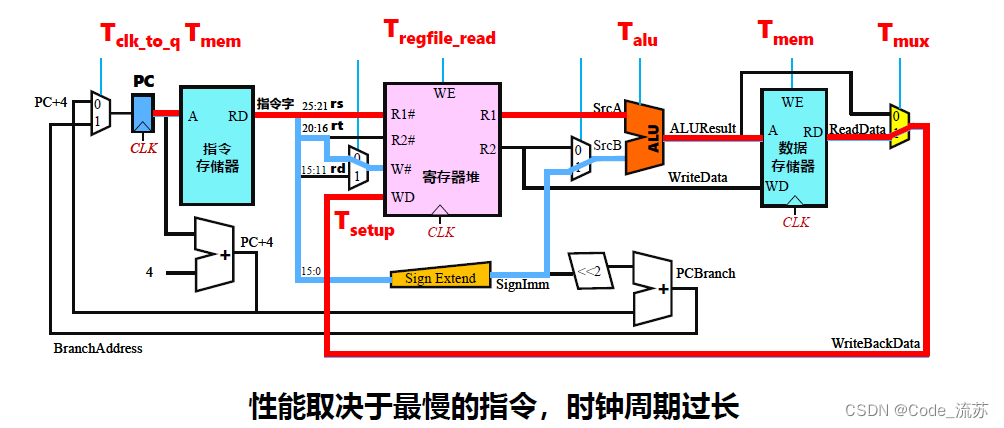

1.单周期MIPS关键路径LW指令

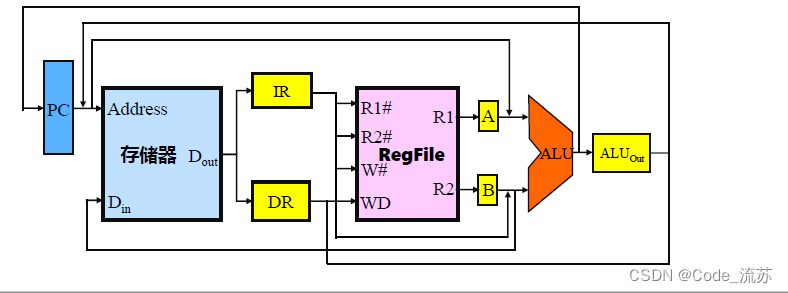

2.多周期MIPS数据通路特点

◆ 不再区分指令存储器和数据存储器,分时使用部分功能部件

◆ 主要功能单元输出端增加寄存器锁存数据

◆ 传输通路延迟变小,时钟周期变短

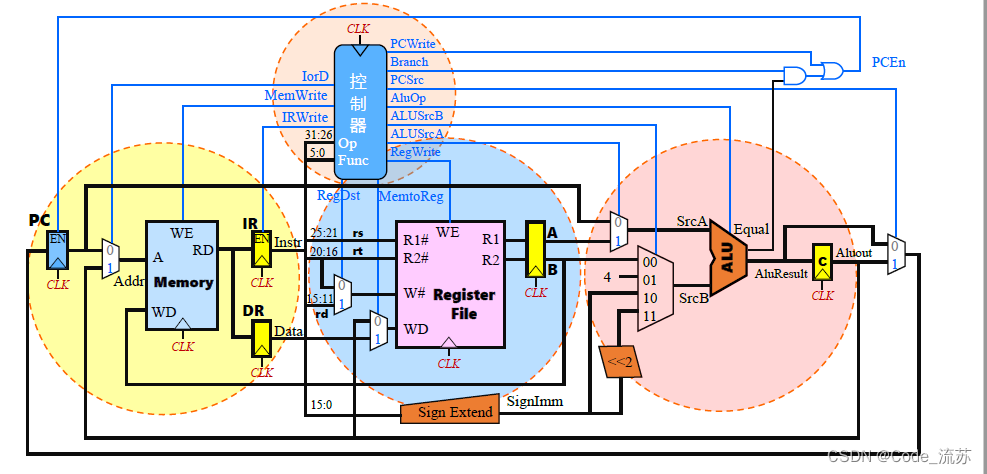

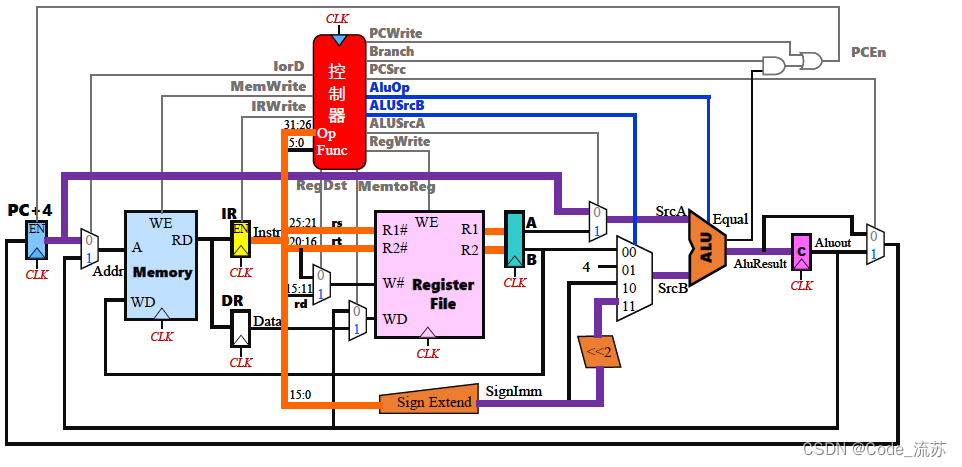

3.多周期MIPS CPU数据通路

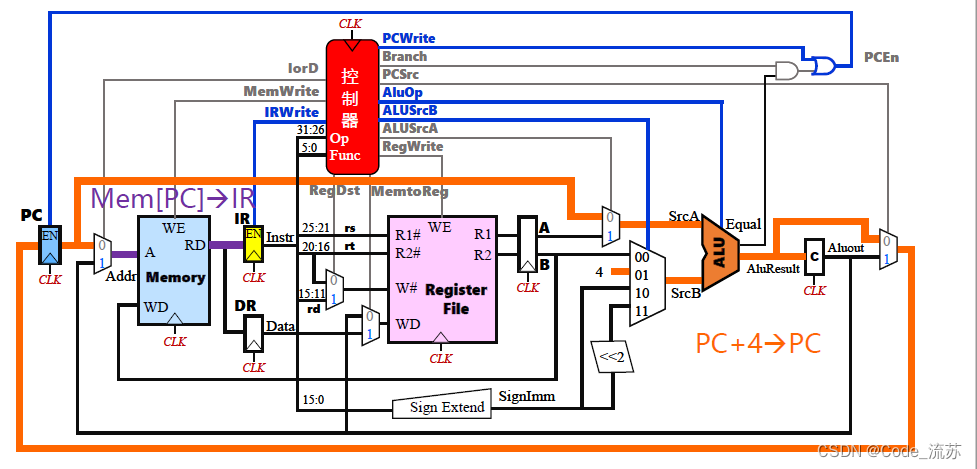

4.多周期MIPS取指令阶段T1

Mem[PC]→IR PC+4→PC

5.多周期MIPS取指令阶段T2

译码、Reg→A、B、PC+4+Imm16<<2→C

★小总结:在上一节的学习中,对单周期MIPS进一步地进行了学习,对相关知识有了更多的了解。本节内容,对多周期 MIPS CPU 数据通路进行学习,通过本节内容的学习,对单周期MIPS关键路径LW指令、多周期MIPS数据通路特点、多周期MIPS CPU数据通路等内容有了一定的认识与了解。

Last (一键到达文章末尾)

First(一键返回到文章目录)

笔记内容学习资料:计算机组成原理微课版(谭志虎、秦磊华等编著)

课件资料及视频学习:MOOC计算机组成原理(华中科大)

计算机组成原理专栏——笔记及测验练习都在这

如果对大家有帮助的话,希望大家能多多点赞+关注!这样我动力会更足哦! ღ( ´・ᴗ・` )比心。