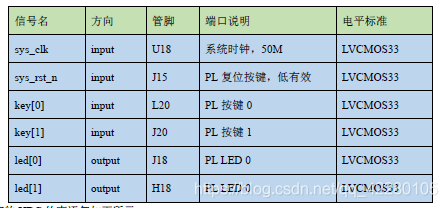

一、基础知识

- 按键按下为低电平,未按为高

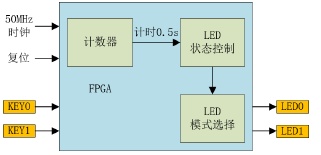

- 两按键未按灯都亮;KEY0按同时亮灭;KEY1按交替闪烁

- 第一个always产生计数器;第二个always每500ms给出LED闪烁信号;第三个always用case表示按键值控制LED闪烁

二、程序

module key_led(

input clk,

input rst_n,

input [1:0] key,

output reg [1:0] led //默认为wire类型 要调整成reg

);

reg [24:0] cnt;

reg led_ctrl;

//计数器

always @(posedge clk or negedge rst_n)begin

if(!rst_n)

cnt <= 25'd0;

else if(cnt < 25'd2500_0000) //计数500ms

cnt <= cnt + 1'b1;

else

cnt <= 25'd0;

end

//每隔500ms就更改LED的闪烁状态

always @(posedge clk or negedge rst_n)begin

if(!rst_n)

led_ctrl <= 1'b0;

else if(cnt == 25'd2500_0000)

led_ctrl <= ~led_ctrl;

end

//根据按键的状态以及LED的闪烁状态来赋值LED

always @(posedge clk or negedge rst_n)begin

if(!rst_n)

led <= 2'b11; //该上面 +reg 就不会报错

else case(key)

2'b10: //如果按键0按下,则两个LED交替闪烁

if(led_ctrl == 1'b0)

led <= 2'b01;

else

led <= 2'b10;

2'b01: //如果按键1按下,则两个LED同时闪烁

if(led_ctrl == 1'b0)

led <= 2'b11;

else

led <= 2'b00;

2'b11: //如果两个按键都未按下,则两个LED都保持点亮

led <= 2'b11;

default:;

endcase

end

endmodule

三、总结

- 关于wire改reg 问题不懂,可能前面讲过忘了

2020.4.24答:这个应该是说wire是直连,上程序中LED需要用LED控制处理,所以说这控制是reg