上节介绍了共模抑制比的定义以及产生的原因。这节主要介绍其影响。

简单来说,CMRR是运放的一个直流精度参数,它的好坏会引起运放的放大电路的输出误差的好坏。

一般运放datasheet标出的CMRR表示:在输入共模电压范围内的直流共模抑制比。

由于CMRR有限,当运放输入端有共模电压Vcm时,会引起一个输入失调电压,称为Vos_CMRR。

假设某运放CMR = 130 dB,当共模电压为5V时,这个失调电压为1.58uV,计算过程如下:

可计算得:CMRR = 0.316uV/V

进一步可算的Vos_CMRR = CMRR*Vcm = 0.316 * 5 = 1.58 uV

对于上图增益等于2 的电路,输出误差为3.16uV。若有一个以2.5V为基准的双极性输入24位ADC,一个LSB电压值为2*2.5/2^24 = 5/16777216 = 0.298uV。与3.16uV相比,相当于LSB有3.16/0.298 = 11 个值的变化。

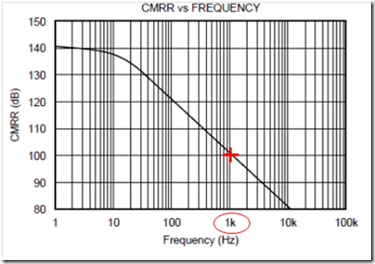

接下来介绍另一个影响:运放的CMRR是随频率增加而降低的。datasheet通常给出曲线图。

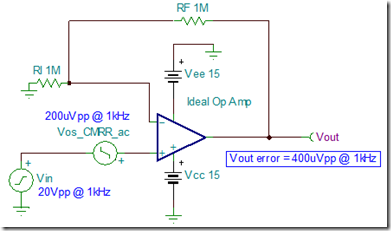

下面计算一下这个特性的影响:如下图所示,当共模信号为一个1KHz的20Vpp正弦信号时,它引起的输入失调电压Vos_CMRR就是1KHz的200uV正弦信号。对于增益为2的放大电路,输出误差就是1KHz 400uV偏差了。

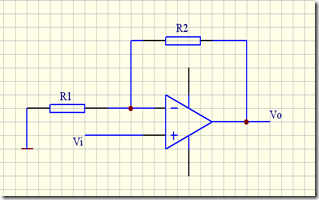

有一点需要注意,对于反向比例放大电路,如下图,它的同向端接地,由于虚短,运放共模信号将为0,并且不随信号频率变化而变化。因此共模信号引起的误差很小。

而对于同向比例放大电路,它的同相端是接的信号,由于虚短,此时运放共模电压就是信号的电压。如果信号本身频率很高,幅值也很大。那么引入的Vos_CMRR_AC势必很大。此时应选择在此信号频率上CMRR依然很高的运放。即使这样,影响也会比较严重。

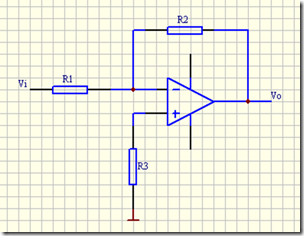

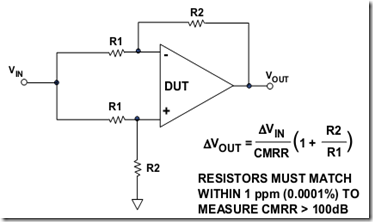

最后简单介绍一下运放的CMRR测试。通常人们会想到通过下图方法测试CMRR,看似简单却有一个问题,就是它要求使用的电阻匹配度非常的高,为了测量CMRR > 100 dB 的运放,需要1ppm以下的电阻。所以这个电路基本不实用。

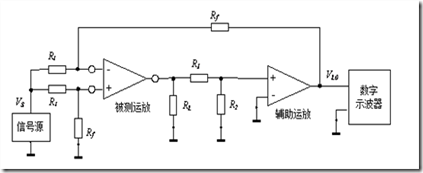

简单易行的方法如下,它对电阻匹配要求低得多。

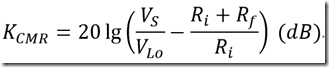

假设信号源出来的电压为Vs,辅助运放输出电压为VLo,则有:

有兴趣的话,可以去找一篇关于CMRR的论文看看,题目是《运算放大器共模抑制比的仿真与测试》,直接点击可下载。

在原贴的part-8 部分的评论里也有下载链接。