前言

环境:

1、Quartus18.0

2、vscode

3、板子型号:EP4CE6F17C8

要求:

每隔0.2s循环亮起LED灯

一、流水灯介绍

从LED0开始亮起到LED3又回到LED0循环往复。

二、系统设计

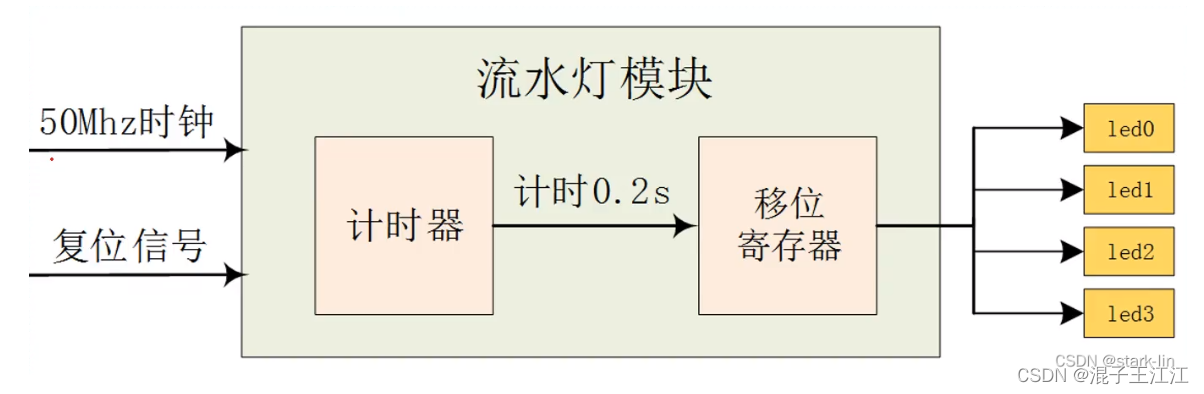

1.模块框图

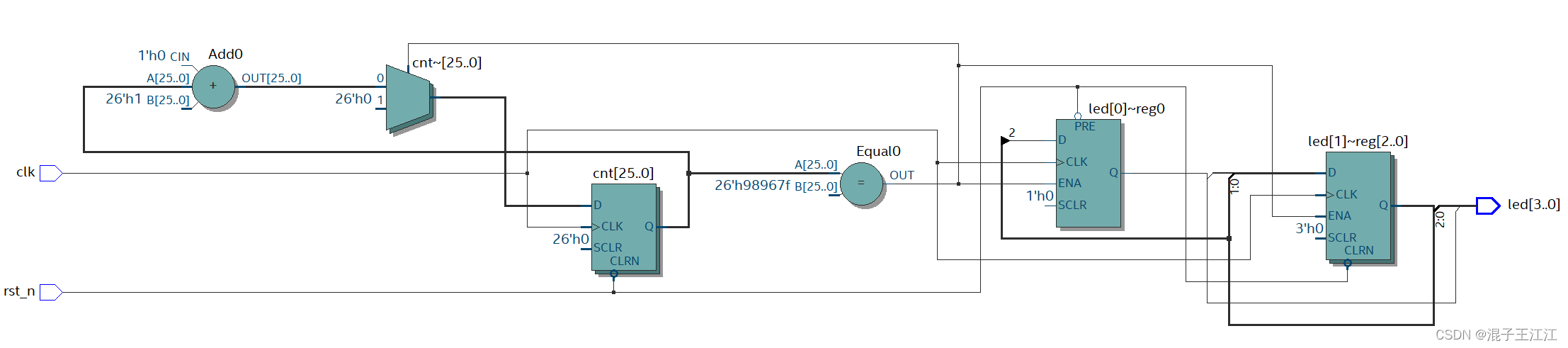

2.RTL视图

三、源码

module led #(

parameter MAX_NUM = 26'd9_999_999

)(

input clk,

input rst_n,

output reg [3:0] led

);//每间隔1s,实现led的亮灭

//parameter MAX_NUM = 26'd9_999_999;

reg [25:0] cnt;

always @(posedge clk or negedge rst_n) begin

if(!rst_n)begin

cnt <= 26'd0;

end

else if(cnt == MAX_NUM)begin

cnt <= 26'd0;

end

else begin

cnt <= cnt + 1'd1;

end

end

//LED控制

always @(posedge clk or negedge rst_n) begin

if(!rst_n)begin

led <= 4'b0001;

end

else if(cnt == MAX_NUM)begin//cnt == 26'd09_999_999

led <= {

led[2:0],led[3]};

end

else begin

led <= led;

end

end

endmodule

四、效果

流水灯

五、总结

这里使用了拼接符对LED进行处理加上一个0.2s的计时器进行控制即可。