对于FPGA的结构原理,先不进行全面的了解,先能根据教程程序看得懂,写得出来跑起来。慢慢的了解程序运行的原理,各种语法的使用。

今天对流水的程序有一个认识,熟悉软件的使用,语法规则,原理。以正点原子的例程为例,代码如下

1 // Created by: 正点原子 2 3 module flow_led( 4 input sys_clk , //系统时钟 5 input sys_rst_n, //系统复位,低电平有效 6 7 output reg [3:0] led //4个LED灯 8 ); 9 10 //reg define 11 reg [23:0] counter; 12 13 // main code 14 //计数器对系统时钟计数,计时0.2秒 15 always @(posedge sys_clk or negedge sys_rst_n) begin 16 if (!sys_rst_n) 17 counter <= 24'd0; 18 else if (counter < 24'd1000_0000) 19 counter <= counter + 1'b1; 20 else 21 counter <= 24'd0; 22 end 23 24 //通过移位寄存器控制IO口的高低电平,从而改变LED的显示状态 25 always @(posedge sys_clk or negedge sys_rst_n) begin 26 if (!sys_rst_n) 27 led <= 4'b0001; 28 else if(counter == 24'd1000_0000) 29 led[3:0] <= {led[2:0],led[3]}; 30 else 31 led <= led; 32 end 33 34 endmodule

这个代码的功能是点亮流水灯。代码的内容是:用一个定时器计时,到了0.2s就自动清零,否则自动+1计数。另一方面,判断是否到了0.2s,到了就换另一个led亮。程序写好后,烧写在芯片里,会形成这样的电路,功能是并行的。不像是stm32需要用C语言写代码,生成指令,cpu取指执行。FPGA会快一些。

代码的整体结构,头和尾有 module 和 endmodule 这是模块的开始和结束。如果工程中有其他的功能代码,写在一个.v文件,也会有这个 module 。就是一个功能或者一个模块卸载一个.v 文件,这样便于管理。

input sys_clk , 可以理解为定义一个输入类型的变量。

output reg [3:0] led, 可以理解为,定义一个输出类型的变量,他占据了4个bit。

always @(posedge sys_clk or negedge sys_rst_n) begin 可理解为,复位了或者有新的始终进来就做下面的代码。

led <= 4'b0001; 这个是赋值,和C语言有些不一样。

4'b0001 是一个数,b:二进制表示,0001。 4' 是指这个数是4位的。

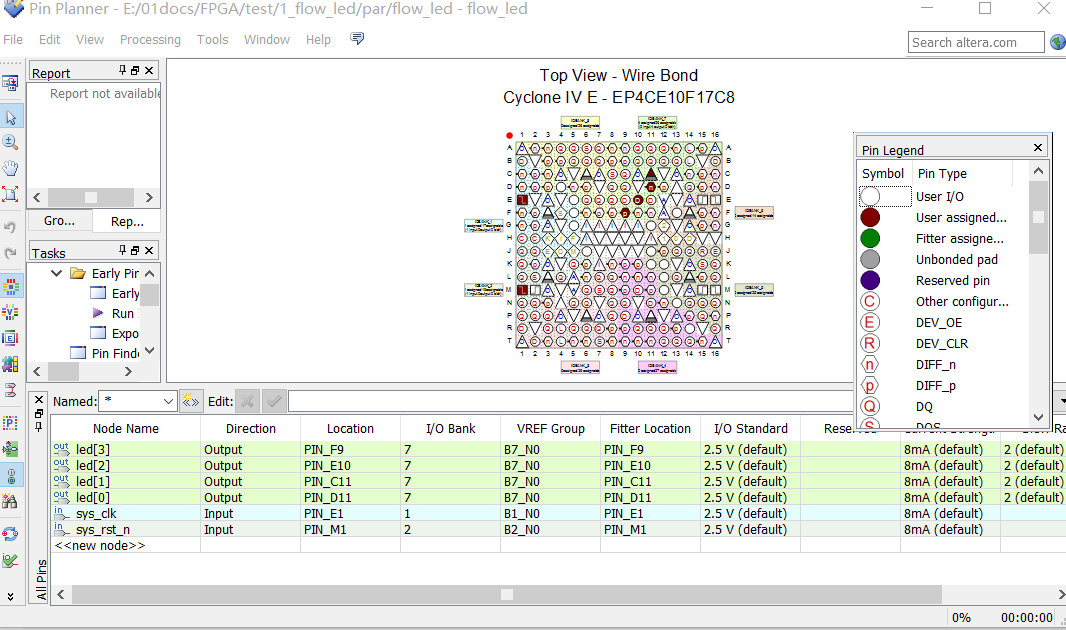

然后这个程序实现了点灯。但是有一点,他是怎么控制的引脚呢,led是接在引脚少了,这里面也没涉及到引脚啊。在下面这里:

通过这个图可以看到,我们在工程里面的变量,需要“绑定”引脚。使使之一一对应,举个例子led变量是4个bit的,把0 1 2 3 分别对应板子上led连接的引脚上,操作led就相当于操作引脚了。