写之前先废话一段。学长两周前给了我一块2010年的FPGA开发板,没有资料没有原理图,那几天简直奔溃。后来买了学生版的黑金开发板AX301,发现例程其实也还好,但就是少了很多自己的理解,代码也需要自己一句一句地啃。为了加深自己的印象,于是决定把学过的例程写成博客,也记录一下自己的学习历程。

凡是入门开发板,点灯是必备的。相信学过ARM系列的同学应该会有一定的基础,那我们就直接进入流水灯环节。首先呈上代码:

module led_test

(

input clk, // system clock 50Mhz on board

input rst_n, // reset ,low active

output reg[3:0] led // LED,use for control the LED signal on board

);

//define the time counter

reg [31:0] timer;

// cycle counter:from 0 to 4 sec

always@(posedge clk or negedge rst_n)

begin

if (rst_n == 1'b0)

timer <= 32'd0; //when the reset signal valid,time counter clearing

else if (timer == 32'd199_999_999) //4 seconds count(50M*4-1=199999999)

timer <= 32'd0; //count done,clearing the time counter

else

timer <= timer + 32'd1; //timer counter = timer counter + 1

end

// LED control

always@(posedge clk or negedge rst_n)

begin

if (rst_n == 1'b0)

led <= 4'b0000; //when the reset signal active

else if (timer == 32'd49_999_999) //time counter count to 1st sec,LED1 lighten

led <= 4'b0001;

else if (timer == 32'd99_999_999) //time counter count to 2nd sec,LED2 lighten

led <= 4'b0010;

else if (timer == 32'd149_999_999) //time counter count to 3rd sec,LED3 lighten

led <= 4'b0100;

else if (timer == 32'd199_999_999) //time counter count to 4th sec,LED4 lighten

led <= 4'b1000;

end

endmodule

这段代码其实非常easy,但对于初学者来说看起来也很费力。(想当初老子看2010年那块板子的资料时为了强调verilog编程的模块化思想,这么简单的流水灯程序强行用了5个文件来写。。。看得吐血。先抛开模块化不说,我来解释下这段程序。)

首先,系统时钟信号:A301的晶振是50MHz,意思就是说,计数器计数50000000就可以实现1秒的效果。因此,4个流水灯就需要50000000*4=200000000,因为从0开始数,因此200000000-1=199999999。那么代码中的第一个always实现的就是计数器功能。当产生rst信号时,计数器归零,否则,计数器+1,直到到达199999999,计数器又归零。

我猜初学者也可能感到疑惑,为什么要计数到200000000呢?因为在verilog语言里面,程序是并行的,而没有先后顺序。因此可以看到第二个程序,4个LED灯是同时工作的,只是规定在一个周期4秒内,LED1第一秒亮,LED2第二秒,LED3第三秒,LED4第四秒,因此实现了流水灯的效果。

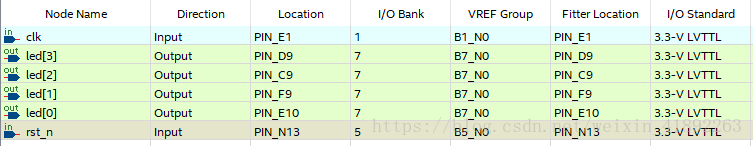

代码写完了,编译一下,没有错误,此时去设置引脚,Assignments/Pin_Planner。打开之后,去找资料里面的原理图,看看CLK,RST,还有四个LED在哪个管脚上。

你可以直接在Location里面打E1、D9、C9、……也可以拖动Node name到芯片图的位置上。

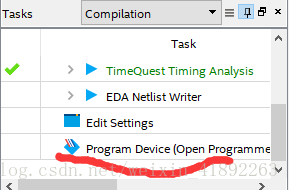

设置好管脚后,不需要保存,再编译。没有错误之后,打开programer,一般可以直接双击编译区最下面的图标:

然后,请连接你的USB blaster,下载程序。

emmmmmmm,关于USB blaster找不到驱动和Quartus生成不了sof下载文件的问题,下次我再另写一篇博客吧。也是心疼自己当时花了一整天时间搞这个事情没有人指点。

那么如果上面的步骤没有问题,恭喜你完成FPGA的第一个入门程序。