LED(Light Emitting Diode)发光二极管

特点:工作电流小,可靠性高,寿命长。

直插式二极管,管脚长的一端为阳极,短的一端为阴极;单项导电

贴片式二极管,有颜色标记的是阴极,对应另一侧是阳极。

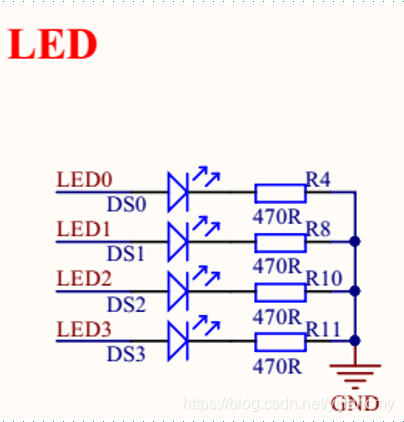

电路原理图:

LED灯与FPGA开发版的管脚连接:

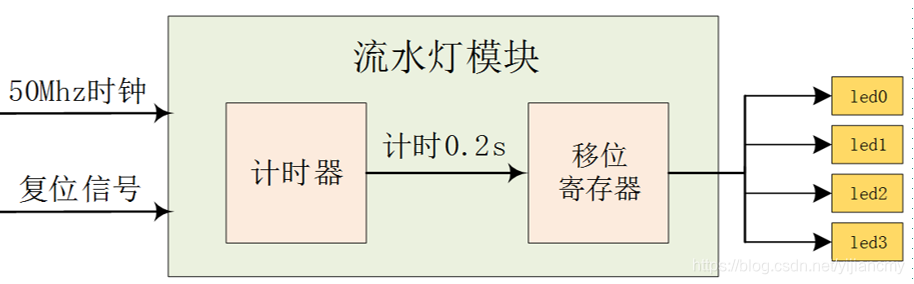

流水灯设计

50Mhz时钟是外部50MHz晶振提供的,整个系统的驱动时钟。

复位信号低电平有效,与外部复位按键连接。

计时器用来计算0.2s的时间,即四个LED灯轮流亮的间隔。

移位寄存器控制四个LED灯的亮灭。

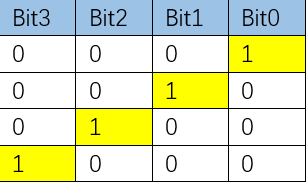

移位寄存器:分别对应LED0,LED1,LED2,LED3

小插曲:系统时钟是50Mhz,所以时钟周期是20ns。计数器需要对系统时钟进行计数,计时0.2秒。

1秒=1000毫秒(ms)

1秒=1000,000微妙(us)

1秒=1000,000,000纳秒(ns)

0.2秒/20ns = 2000,000,00/20=1000,000,0,需要24bit数据

对系统时钟计数1000,000,0次。

流水灯代码:

module flow_led_1(

input sys_clk50, //50Mhz的系统时钟,所以时钟周期是20ns

input rst_n, //复位按键

output reg [3:0] led //led灯的寄存器

);

reg [23:0] cnt; //计数器 对系统时钟进行计数,计时0.2秒

//0.2秒计数器

always @(posedge sys_clk50 or negedge rst_n)

begin

if(!rst_n)

cnt <= 1'b0;

else

if(cnt < 24'd1000_0000)

cnt <= cnt + 1'b1;

else

cnt <= 24'd0;

end

//使用移位寄存器控制LED灯

always @(posedge sys_clk50 or negedge rst_n)

begin

if(!rst_n)

led <= 4'b0001;

else

if(cnt == 24'd1000_0000) //检测计数到0.2秒

led <= {led[2:0],led[3]}; //将led寄存器的第三位放到前面,第四位放置第一位

else

led <= led; //计数还未到达0.2秒,保持灯的状态不变

end

endmodule

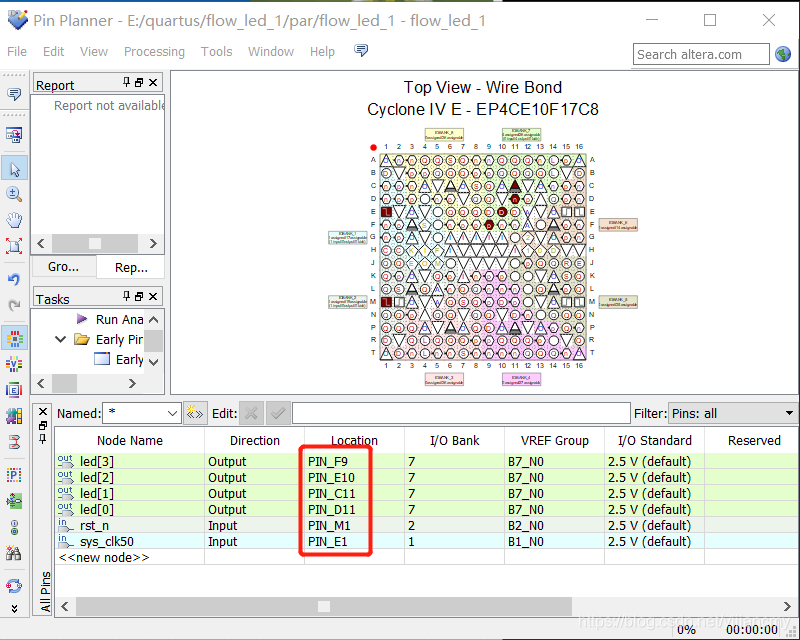

运行后,设置管脚

编译并下载到开发版。