20180805 玩玩FPGA开发,学学Verilog,学学基本操作,制作流水灯

我毕业设计做的就是FPGA,但是什么都没有学。校外毕设老师对我非常无奈,不过还好,校内的指导老师送了我一个很久很久的开发板,配套的教程是2010年的竞赛教程,教程里的截图很显然的win7风格……下面是老师送的开发板上的照片,能玩的地方有:小灯和数码管,还有一个VGA的输出接口。(家里没有VGA线,懒得买,所以就不玩这个了)

图:老师送的板子和下载线

一、开发环境搭建

这点没什么可说的,就是下载一个ISE14.7(板子比较旧,虽说Xilinx提供了新的开发工具Vivado,但是开发板上的芯片似乎只能用ISE开发),然后下载一个破解文件,破解一下就好了。(这个过程其实挺费劲的,网速啊…………………………)

二、新建工程

打开ISE,新建工程,选择对应的芯片类型。Spartan3E XC3S500E……

后面都是基本操作,不截图了。

软件设计出来就是给人用的,要不是给人用的,咱不用就行了。

三、规划思路

要练习做个什么呢?首先需要有个大体的规划,把所有小灯和数码管给用上——

在复位上电以后,8个小灯按照跑马灯从左到右来跑,数码管显示0000,当小灯最右边的一个由亮转灭的时候,数码管显示的数字+1。这是一个非常非常初步的目标,如果用51单片机实现将非常简单,不超过50行代码。

FPGA的开发,按照书本上讲,需要一个自顶而下Top-down的思维:从最顶层的模块开始思考,分析其功能可以细分为什么模块,输入输出是什么,然后针对每个细分后的模块继续分析,直到能够用较为简短的行为级语言描述的模块。然后,将这些行为级模块转化为RTL级(我的理解是门电路、寄存器等非常小的级别)的代码。

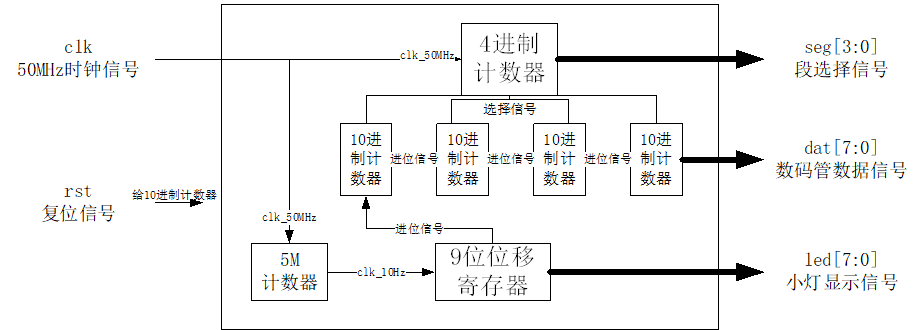

分析顶层模块:

输入:板载的晶振50MHz的clk,复位按钮(信号)rst

输出:8个led小灯,4个8段数码管的选择信号seg和数据信号dat

①为了让人眼能看明白,小灯的切换时间要>人眼能感受到的时间(约0.02s),至少需要一个分频模块,将clk分个5Mà得到大概10Hz频率的信号(晶振不准,精度要求不高,大概调一下觉得舒服就可以了)

②数码管要4个都显示,需要不断地扫描,扫描的时间<人眼感受到的时间,这个用clk就行了,需要一个扫描模块,相当于一个4位的位移寄存器,对于每一个状态,读取不同缓存区(存储要显示的数字的地方)

③由上,需要4个缓存模块

④存储的要显示的数字是什么编码的?如果采用BCD码,则需要一个BCD转数码管显示码的模块,如果直接采用数码管显示码来计数,也是可以的。

⑤8个小灯要跑马灯,需要一个9位的位移寄存器

⑥跑马灯到右边时,数码管显示的数字要+1,需要一个9进制的计数器。

因此,模块示意图如图所示:

四、编写代码

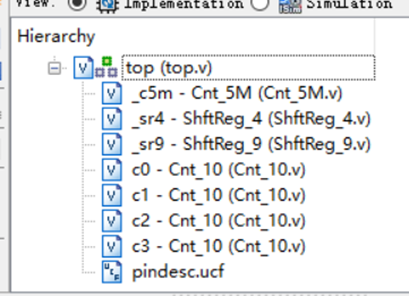

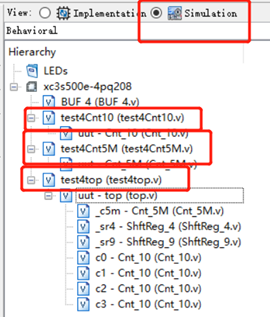

工程结构如图所示:

下面针对每类模块编写代码。

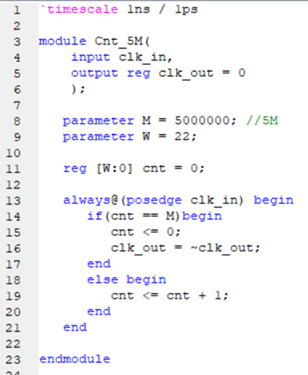

①时钟分频模块,这相当于一个计数器,用行为级代码来编写:

代码大意是每来一个clk的上升沿,计数变量cnt+1,直到计数变量cnt与预设值M相等的时候,输出clk_out取反。

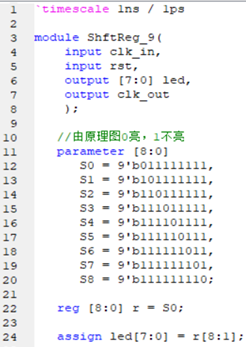

②状态转换器,其实还是一个计数器,编码比较诡异而已

代码大意是每来一个上升沿,如果当前状态是S(X),则输出下一个状态S(X+1)。

虽然这个代码用位移寄存器也可以完成,但我只是想试试这个写法而已。

其他部分的代码类似,在此略过。

五、仿真

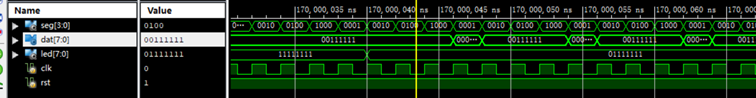

这里针对每种模块都编写了test文件。仿真得到的波形看起来也是正确的……

波形图上seg表示不停地切换要显示的数码管,dat表示数码管要显示的数值,led表示当前小灯的显示情况。

六、下载到开发板

果然会出现错误好吧——

图上数码管看起来要显示7,但是周围的其他部分也似乎亮了起来,而且并没有按照想法显示0007,这就是传说中的"鬼影现象"好吧

╮(╯-╰)╭

七、改进思想

有几个想法:

①加入一个rdy信号,表示数据准备好准备好,再增加一个缓冲模块,当rdy信号有效的时候,输出等于输入;当rdy信号无效的时候,输出为0000,表示一个数码管也不选择。

问题来了,这个rdy信号从什么地方来?计划之一,从10进制计数器来,问题是有4个计数器,这个信号还需要求一个或运算?不准确。计划之二,从4进制计数器来,这个信号从clk延迟一段时间而来,这个需要进一步设计一下。

②专门弄一个负责显示4位(可扩展)数码管的模块,以后都可以调用(复制粘贴),(例化)。

心里感受到了挫败感,明天再弄。