前言:找了好久,网上没有这方面的入门教材,不知是不是自己找的不是地。自己试着编写的流水灯程序,还是为了熟悉ISE软件和开发板。一些步骤不那么详细了,可以参考前篇文章ISE 14.7初次上手(Virtex-6 ML605 实现拨码开关LED–VHDL。

系统:WIN10, 开发平台:ISE 14.7

编程语言:VHDL

硬件平台:Virtex-6 FPGA ML605开发板

项目描述:利用板子上自带66MHz的单极晶振,分频出2Hz的时钟,用来实现8个LED灯依次亮灭,每0.5s亮一个。

Tips:用到了变量之间的类型转换;ISE工具栏最右边的小灯泡很有用!

以下正文

一、创建工程

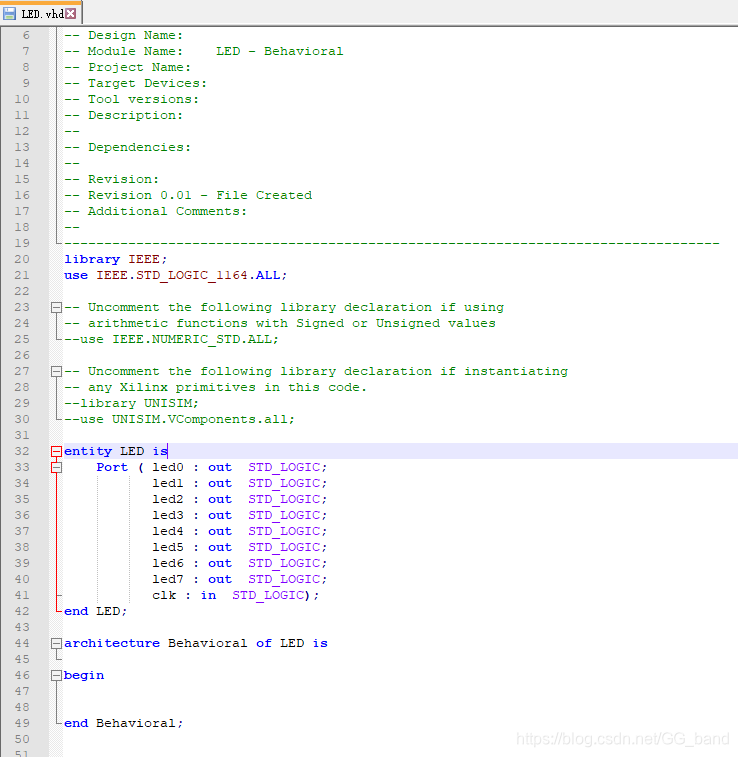

打开ISE软件,按步骤创建顶层文件,同时写入8个LED输出端口和一个CLK时钟输入端口。下图是顶层文件刚创好的时候。注意顶层文件名会是以后.bit的文件名

二、写代码 0.0

architecture Behavioral of LED is

signal clk1: std_logic; -- 时钟分频

signal LED : std_logic_vector (0 to 7); -- 控制灯的整体变量

begin

process (clk) -- 66MHz时钟分频 成2Hz

variable cnt: integer range 0 to 33000000 :=0;

begin

if(clk'event and clk='1')then

if cnt=32999999 then

cnt:=0;

else

cnt:=cnt+1;

end if;

if cnt<=16499999 then

clk1<='1';

else

clk1<='0';

end if ;

end if;

end process;

-------------------------------------------

使用移位操作符SLL移位,但只能 bit_vector类型才可以使用移位操作符,

所以就需要一些变量类型转换。

------------------------------------------

process (clk1)

variable count :bit_vector(8 downto 0):="000000001";

begin

if(clk1'event and clk1 = '1')then

if count = "100000000" then

count:="000000001";

else

LED <= To_StdLogicVector(count(7 downto 0));

count := count SLL 1;

end if ;

end if ;

led0 <= LED(0);

led1 <= LED(1);

led2 <= LED(2);

led3 <= LED(3);

led4 <= LED(4);

led5 <= LED(5);

led6 <= LED(6);

led7 <= LED(7);

end process;

end Behavioral;

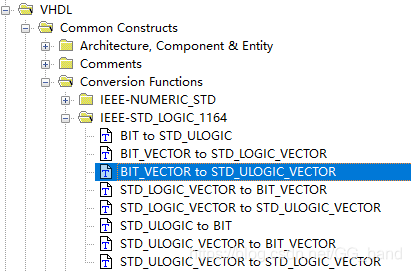

这里我才发现一个很有用的地方!就是ISE工具栏最右边的小灯泡!里面有各个函数的介绍和使用,包含在哪个头文件下很清晰。里面有tcl 操作的使用,UCF约束文件,还有VHDL和Verilog的语法。

在这里可以找到变量转换使用的语句,很方便。

三、综合和仿真

-

直接双击Synthesis -XST 进行综合,等亮绿灯说明没有问题。

-

切换到Simulation栏,右键项目创建 VHDL Test Bench 文件。

signal BLED : std_logic_vector (0 to 7); -- 控制灯的整体变量

在Test Bench文件信号声明下面加上上面句子,因为我的顶层文件名叫LED,与顶层文件里面的信号LED重名了,就改成BLED了。剩下的clk_process不用改,就改下一个进程。

stim_proc: process(clk)

variable count :bit_vector(8 downto 0):="000000001";

begin

led0 <= BLED(0);

led1 <= BLED(1);

led2 <= BLED(2);

led3 <= BLED(3);

led4 <= BLED(4);

led5 <= BLED(5);

led6 <= BLED(6);

led7 <= BLED(7);

if(clk'event and clk = '1')then

if count = "100000000" then

count:="000000001";

else

BLED <= To_StdLogicVector(count(7 downto 0));

count := count SLL 1;

end if ;

end if ;

end process;

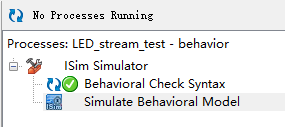

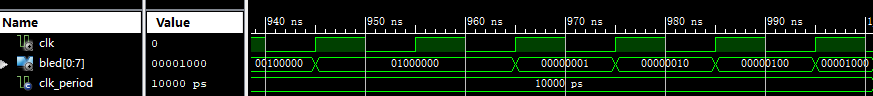

编译成功后,Behavior Model就可以进入Simulate Behavior Model观看仿真波形。

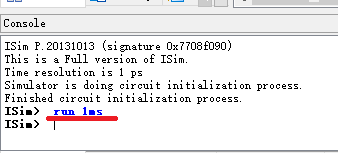

在新弹出的窗口 输入 run 1ms。。这是仿真时长。

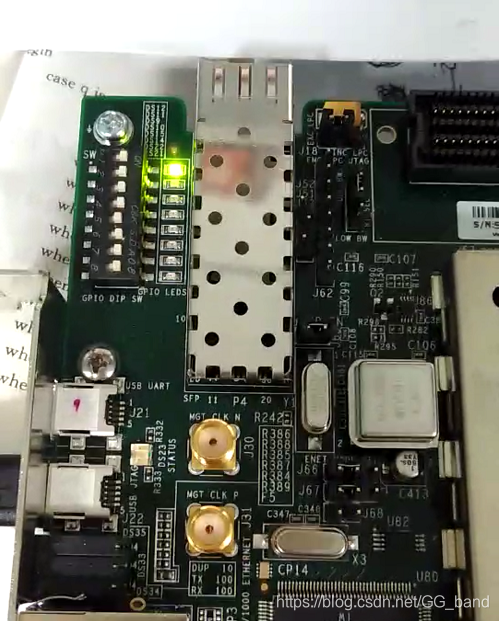

剩下按照前一篇文章进行管脚的锁定和程序的下载就可以了,就只放一张成果照片了~

整个工程我放在了GitHub上,上面还有一些其他的FPGA小设计,有问题欢迎大家进行交流。